AXI UART 16550 v2.0 www.xilinx.com 4

PG143 November 18, 2015 Product Specification

Introduction

The LogiCORE™ IP AXI Universal Asynchronous Receiver

Transmitter (UART) 16550 connects to the Advance

Microcontroller Bus Architecture (AMBA®) AXI and

provides the controller interface for asynchronous serial

data transfer. This soft IP core is designed to connect

through an AXI4-Lite interface.

The AXI UART 16550 detailed in this document

incorporates features described in the PC16550D

Universal Asynchronous Receiver/Transmitter with FIFOs

Data Sheet [Ref 1].

The PC16550D data sheet is referenced throughout this

document and should be used as the authoritative

specification. Differences between the PC16550D and the

AXI UART 16550 product guide are highlighted in

Interrupts in Chapter 2.

Features

• AXI4-Lite interface for register access and data

transfers

• Hardware and software register compatible with all

standard 16450 and 16550 UARTs

• Supports default core configuration for 9600 baud, 8

bits data length, 1 stop bit and no parity

• Implements all standard serial interface protocols

°

5, 6, 7 or 8 bits per character

°

Odd, Even or no parity detection and generation

°

1, 1.5 or 2 stop bit detection and generation

°

Internal baud rate generator and separate

receiver clock input

°

Modem control functions

°

Prioritized transmit, receive, line status and

modem control interrupts

°

False start bit detection and recover

°

Line break detection and generation

°

Internal loopback diagnostic functionality

°

16 character transmit and receive FIFOs

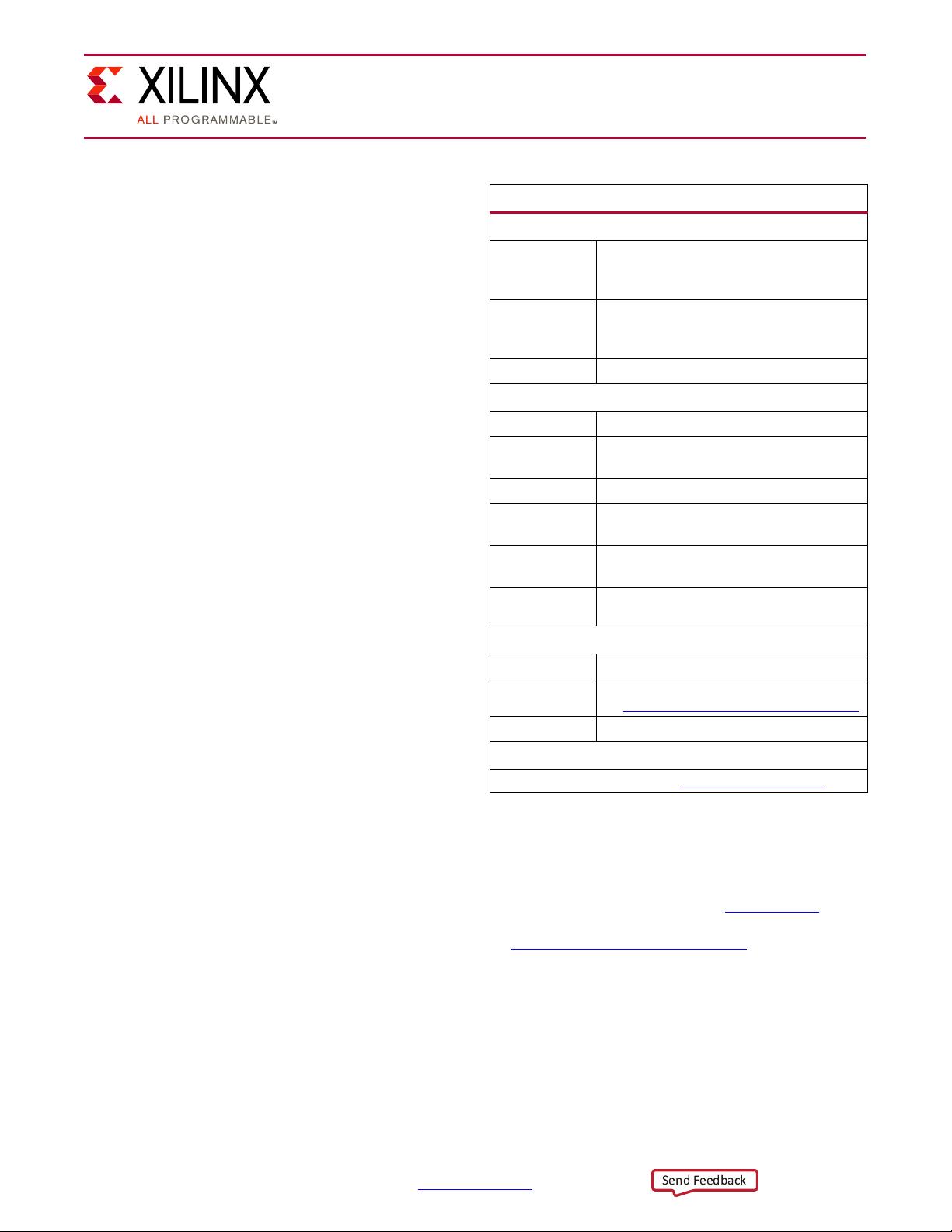

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

UltraScale+™ Families,

UltraScale™ Architecture,

Zynq®-7000, 7 Series

Supported

User

Interfaces

AXI4-Lite

Resources

See Tab le 2 -2.

Provided with Core

Design Files VHDL

Example

Design

VHDL

Tes t Benc h VH D L

Constraints

File

XDC File

Simulation

Model

Not Provided

Supported

S/W Driver

(2)

Standalone and Linux

Tested Design Flows

(3)

Design Entry Vivado® Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the

Vivado IP catalog.

2. Standalone driver details can be found in the SDK

directory (<install_directory>/doc/usenglish/

xilinx_drivers.htm). Linux OS and driver support

information is available from

the Xilinx Wiki page.

3. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

评论5

最新资源