没有合适的资源?快使用搜索试试~ 我知道了~

Section I. Cyclone II Device Family Data Sheet.pdf

需积分: 12 38 下载量 66 浏览量

2013-05-04

17:28:27

上传

评论

收藏 770KB PDF 举报

温馨提示

试读

156页

Section I. Cyclone II Device Family Data Sheet.pdf

资源推荐

资源详情

资源评论

Altera Corporation Section I–1

Preliminary

Section I. Cyclone II

Device Family Data Sheet

This section provides information for board layout designers to

successfully layout their boards for Cyclone

™

II devices. It contains the

required PCB layout guidelines, device pin tables, and package

specifications.

This section includes the following chapters:

■ Chapter 1. Introduction

■ Chapter 2. Cyclone II Architecture

■ Chapter 3. Configuration & Testing

■ Chapter 4. Hot Socketing & Power-On Reset

■ Chapter 5. DC Characteristics & Timing Specifications

■ Chapter 6. Reference & Ordering Information

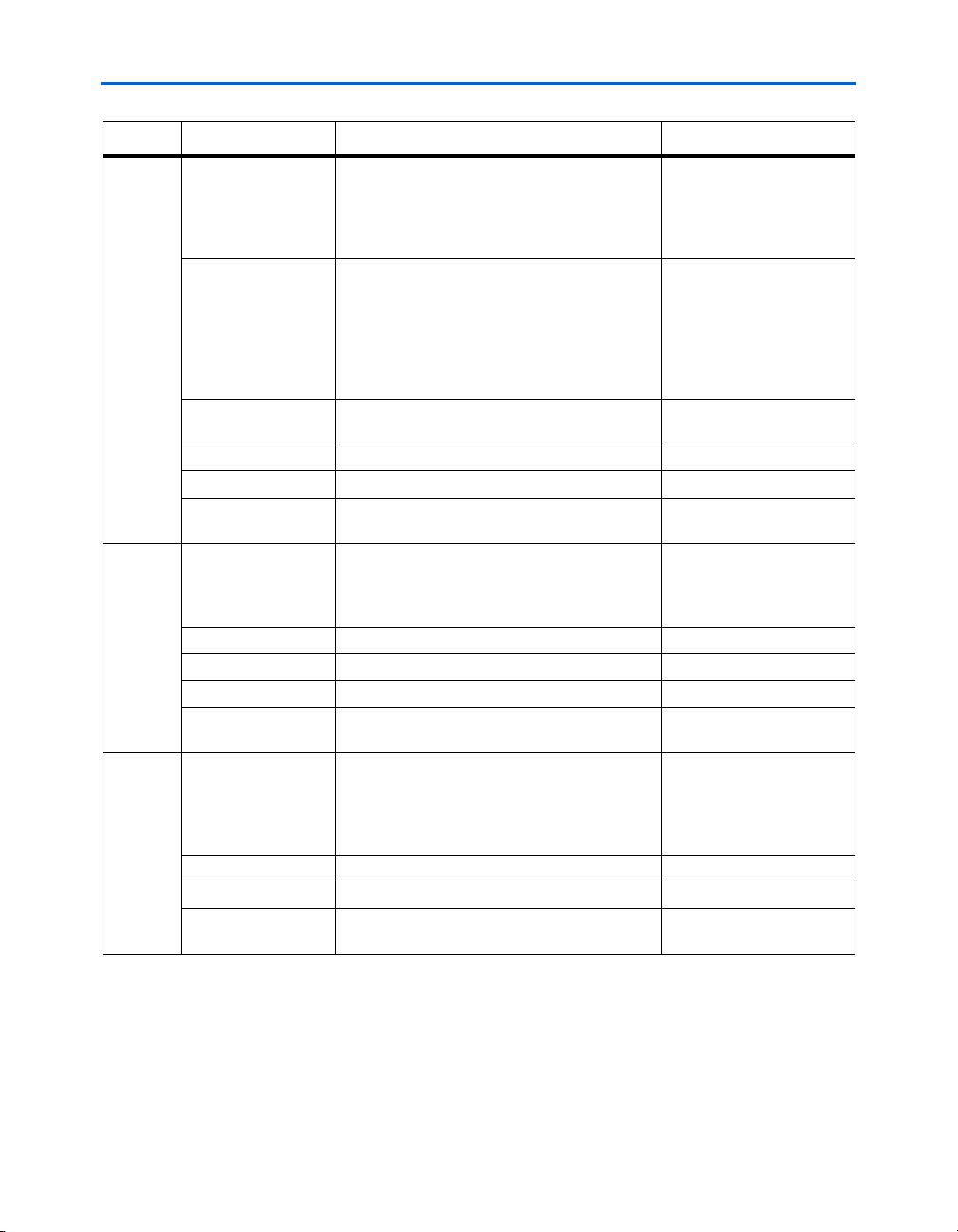

Revision History

The table below shows the revision history for Chapters 1 through 6.

Chapter Date / Version Changes Made Comments

1 June 2006, v3.0 ● Added information for the EP2C15 device.

● Added information for “A” devices.

● Updated all Tables.

November 2005, v2.1

● Updated Introduction and Features.

● Updated Table 1–3.

July 2005, v2.0

● Updated technical content throughout.

● Updated Table 1–2.

● Added Tables 1–3 and 1–4.

November 2004, v1.1

● Updated Table 1–2.

● Updated bullet list in the “Features” section.

June 2004 v1.0 Added document to the Cyclone II Device

Handbook.

Section I–2 Altera Corporation

Preliminary

Cyclone II Device Family Data Sheet Cyclone II Device Handbook, Volume 1

2 June 2006, v3.0 ● Updated Tables 2–1, 2–3, 2–4, 2–6, 2–11,

2–16, 2–19, and 2–21.

● Added information for the EP2C15 device.

● Updated the “Dual-Purpose Clock Pins” and

“Clock Control Block” sections.

November 2005, v2.1

● Updated Table 2–8.

● Updated Figures 2–11 and 2–12.

● Updated Programmable Drive Strength

table.

● Updated Table 2–17.

● Updated Table 2–19.

● Updated Table 2–20.

July 2005, v2.0

● Updated technical content throughout.

● Updated Table 2–17.

February 2005 v1.2 Updated figure 2-12.

November 2004, v1.1 Updated Table 2–20.

June 2004, v1.0 Added document to the Cyclone II Device

Handbook.

3 June 2006, v2.1

● Updated Tables 3–2 and Tables 3–3.

● Updated the “Operating Modes” and

“Cyclone II Automated Single Event Upset

Detection” sections.

July 2005, v2.0 Updated technical content.

February 2005, v1.2 Updated information on JTAG chain limitations.

November 2004. v1.1 Updated Table 3–4.

June 2004, v1.0 Added document to the Cyclone II Device

Handbook.

4 June 2006, v3.0

● Updated the “I/O Pins Remain Tri-Stated

during Power-Up” and “Power-On Reset

Circuitry” sections.

● Added the “"Wake-up" Time for Cyclone II

Devices” section.

Updated Hot Socketing

specifications.

July 2005, v2.0 Updated technical content throughout.

February 2005 v1.1 Removed ESD section.

June 2004, v1.0 Added document to the Cyclone II Device

Handbook.

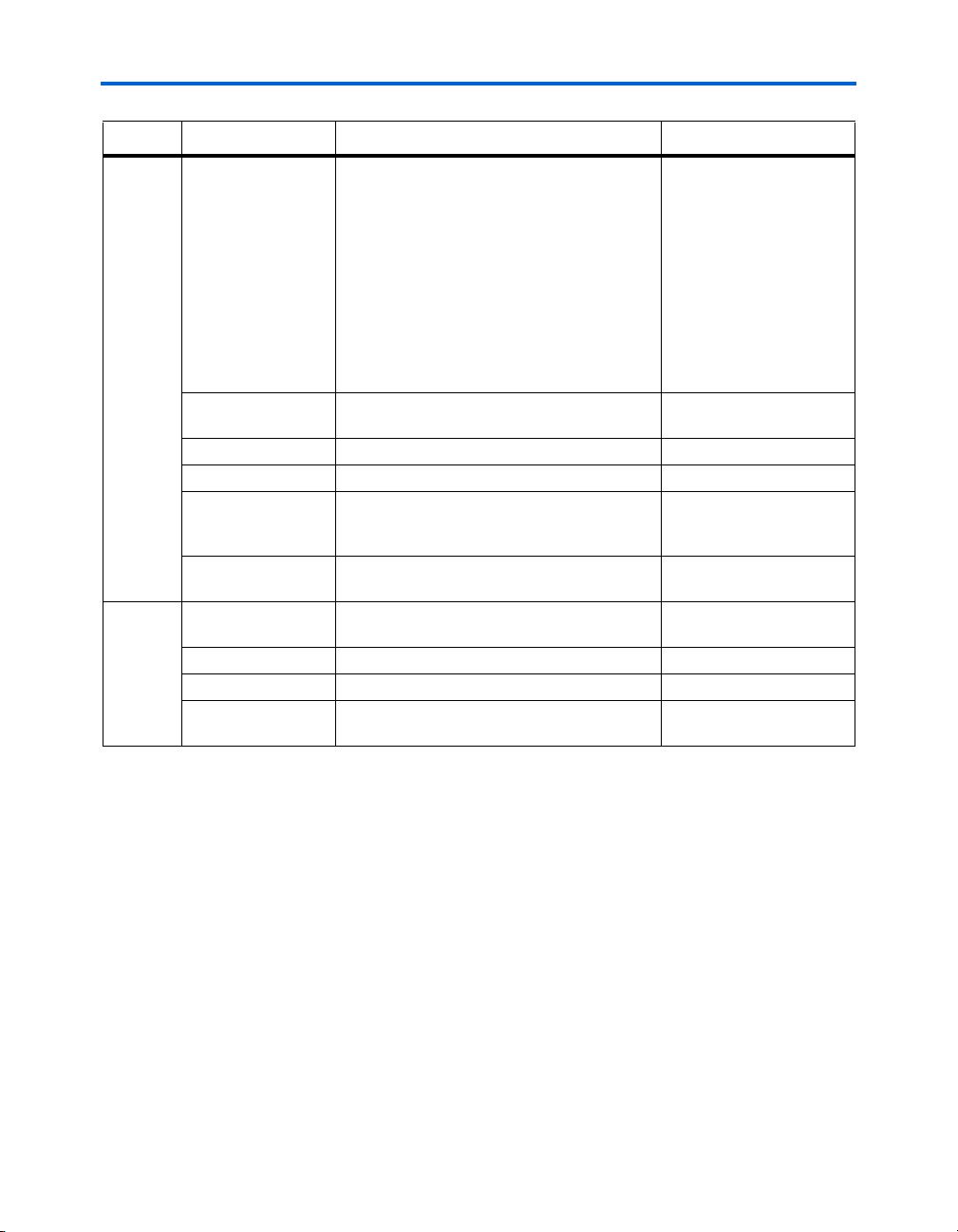

Chapter Date / Version Changes Made Comments

Altera Corporation I–3

Cyclone II Device Handbook, Volume 1

5 June 2006, v3.0 ● Updated the “Operating Conditions”,

“Performance”, and “PLL Timing

Specifications” sections.

● Added the “Duty Cycle Distortion” section.

● Updated Tables 5–2, 5–3, 5–15 through

5–19, 5–21 through 5–24, 5–27 through

5–37, 5–40 through 5–45, 5–51, and 5–53.

● Added 5–25 and 5–26.

● Added measurement

conditions to Rconf

specification.

● Added memory

interface-related timing

specifications.

● Updated Table 5–51

with t

PLL_PSERR

specification.

● Added duty cycle

distortion

specifications.

December 2005,

v2.2

● Updated PLL Timing Specifications

November 2005, v2.1 Updated technical content throughout.

July 2005, v2.0 Updated technical content throughout.

November 2004, v1.1

● Updated the “Differential I/O Standards”

section.

● Updated Table 5–53.

June 2004, v1.0 Added document to the Cyclone II Device

Handbook.

6 June 2006, v1.3 Updated Figure 6–1. Added ordering information

for EP2C15.

November 2005, v1.2 Updated software introduction.

November 2004, v1.1 Updated Figure 6–1.

June 2004, v1.0 Added document to the Cyclone II Device

Handbook.

Chapter Date / Version Changes Made Comments

I–4 Altera Corporation

Cyclone II Device Handbook, Volume 1

Cyclone II Device Family Data Sheet

Altera Corporation 1–1

June 2006

1. Introduction

Introduction

Following the immensely successful first-generation Cyclone

™

device

family, Altera

®

Cyclone II FPGAs extend the low-cost FPGA density

range to 68,416 logic elements (LEs) and provide up to 622 usable I/O

pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are

manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric

process to ensure rapid availability and low cost. By minimizing silicon

area, Cyclone II devices can support complex digital systems on a single

chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who

compromise power consumption and performance for low-cost, Altera’s

latest generation of low-cost FPGAs —Cyclone II FPGAs, offer 60 percent

higher performance and half the power consumption of competing

90-nm FPGAs. The low cost and optimized feature set of Cyclone II

FPGAs make them ideal solutions for a wide array of automotive,

consumer, communications, video processing, test and measurement,

and other end-market solutions. Reference designs, system diagrams,

and IP, found at www.Altera.com, are available to help you rapidly

develop complete end-market solutions using Cyclone II FPGAs.

Low-Cost Embedded Processing Solutions

Cyclone II devices support the Nios II embedded processor which allows

you to implement custom-fit embedded processing solutions. Cyclone II

devices can also expand the peripheral set, memory, I/O, or performance

of embedded processors. Single or multiple Nios II embedded processors

can be designed into a Cyclone II device to provide additional

co-processing power or even replace existing embedded processors in

your system. Using Cyclone II and Nios II together allow for low-cost,

high-performance embedded processing solutions which allow you to

extend your product's life cycle and improve time to market over

standard product solutions.

Low-Cost DSP Solutions

Use Cyclone II FPGAs alone or as DSP co-processors to improve

price-to-performance ratios for digital signal processing (DSP)

applications. You can implement high-performance yet low-cost DSP

systems with the following Cyclone II features and design support:

■ Up to 150 18 × 18 multipliers

■ Up to 1.1 Mbit of on-chip embedded memory

■ High-speed interfaces to external memory

CII51001-3.0

剩余155页未读,继续阅读

资源评论

磁场OS

- 粉丝: 35

- 资源: 636

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- mmqrcode1714153659780.png

- Screenshot_2024-04-27-06-08-58-486_com.baidu.xin.aiqicha.jpg

- 基于Javaweb+Tomcat+MySQL的大学生公寓管理系统+sql文件.zip

- 实训作业基于javaweb的订单管理系统源码+数据库+实训报告.zip

- 多机调度问题贪心算法基于最小堆和贪心算法求解多机调度问题.zip

- 基于同态加密技术的匿名电子投票系统源码.zip

- Pyqt5项目框架-PyQt项目开发实践

- 基于C通过MQTT的智能农业大棚管理系统(本科毕业设计)

- python+CNN的网络入侵检测算法源码.zip

- js 实现记住密码功能 js.cookie.min.js

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功