Contents

State Diagram ................................................................................................................................................ 11

Functional Description ................................................................................................................................... 12

Industrial Temperature ............................................................................................................................... 12

General Notes ............................................................................................................................................ 12

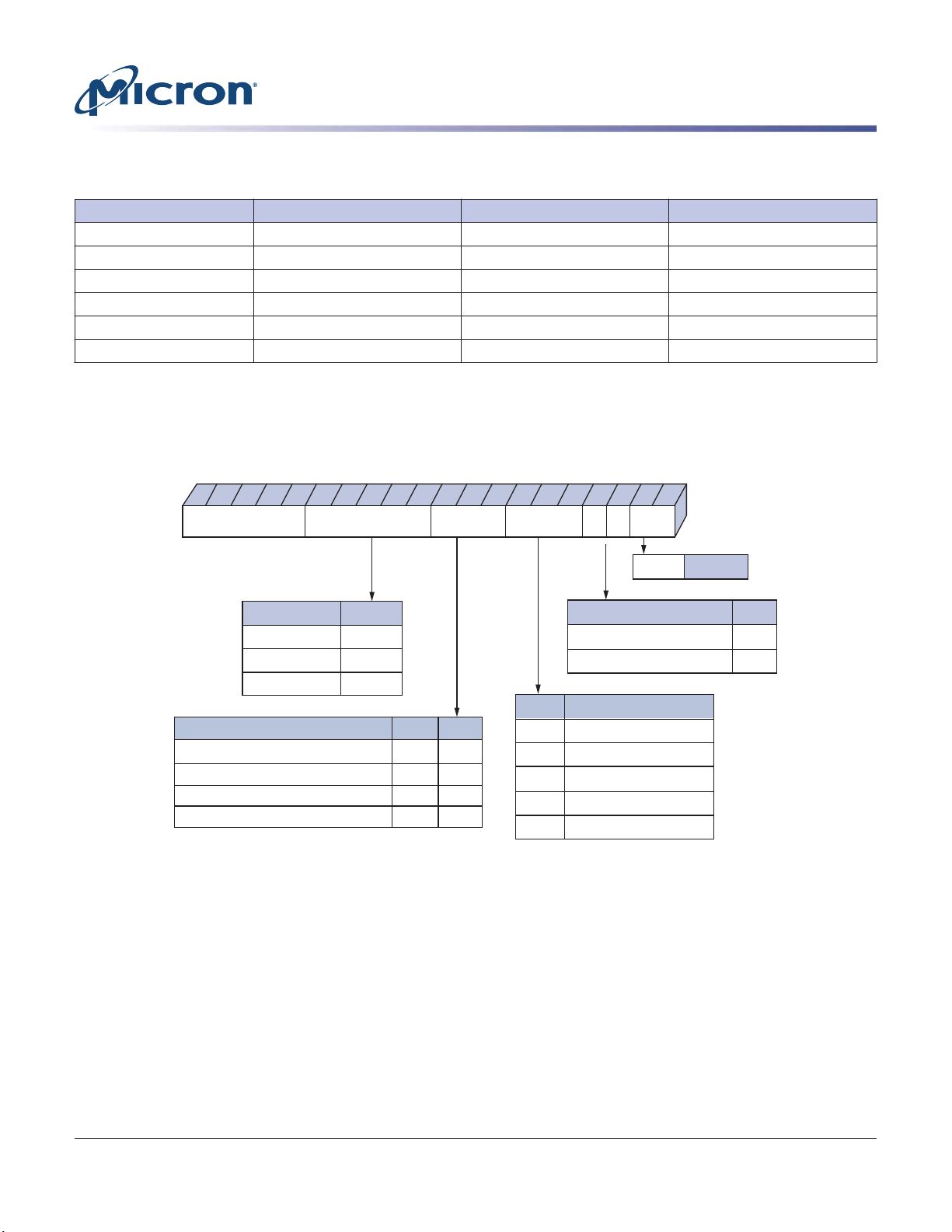

Functional Block Diagrams ............................................................................................................................. 14

Ball Assignments and Descriptions ................................................................................................................. 17

Package Dimensions ....................................................................................................................................... 23

Electrical Specifications .................................................................................................................................. 27

Absolute Ratings ......................................................................................................................................... 27

Input/Output Capacitance .......................................................................................................................... 28

Thermal Characteristics .................................................................................................................................. 29

Electrical Specifications – I

DD

Specifications and Conditions ............................................................................ 31

Electrical Characteristics – I

DD

Specifications .................................................................................................. 42

Electrical Specifications – DC and AC .............................................................................................................. 46

DC Operating Conditions ........................................................................................................................... 46

Input Operating Conditions ........................................................................................................................ 46

AC Overshoot/Undershoot Specification ..................................................................................................... 49

Slew Rate Definitions for Single-Ended Input Signals ................................................................................... 53

Slew Rate Definitions for Differential Input Signals ...................................................................................... 55

ODT Characteristics ....................................................................................................................................... 56

ODT Resistors ............................................................................................................................................ 57

ODT Sensitivity .......................................................................................................................................... 58

ODT Timing Definitions ............................................................................................................................. 58

Output Driver Impedance ............................................................................................................................... 62

34 Ohm Output Driver Impedance .............................................................................................................. 63

34 Ohm Driver ............................................................................................................................................ 64

34 Ohm Output Driver Sensitivity ................................................................................................................ 65

Alternative 40 Ohm Driver .......................................................................................................................... 66

40 Ohm Output Driver Sensitivity ................................................................................................................ 66

Output Characteristics and Operating Conditions ............................................................................................ 68

Reference Output Load ............................................................................................................................... 70

Slew Rate Definitions for Single-Ended Output Signals ................................................................................. 71

Slew Rate Definitions for Differential Output Signals .................................................................................... 72

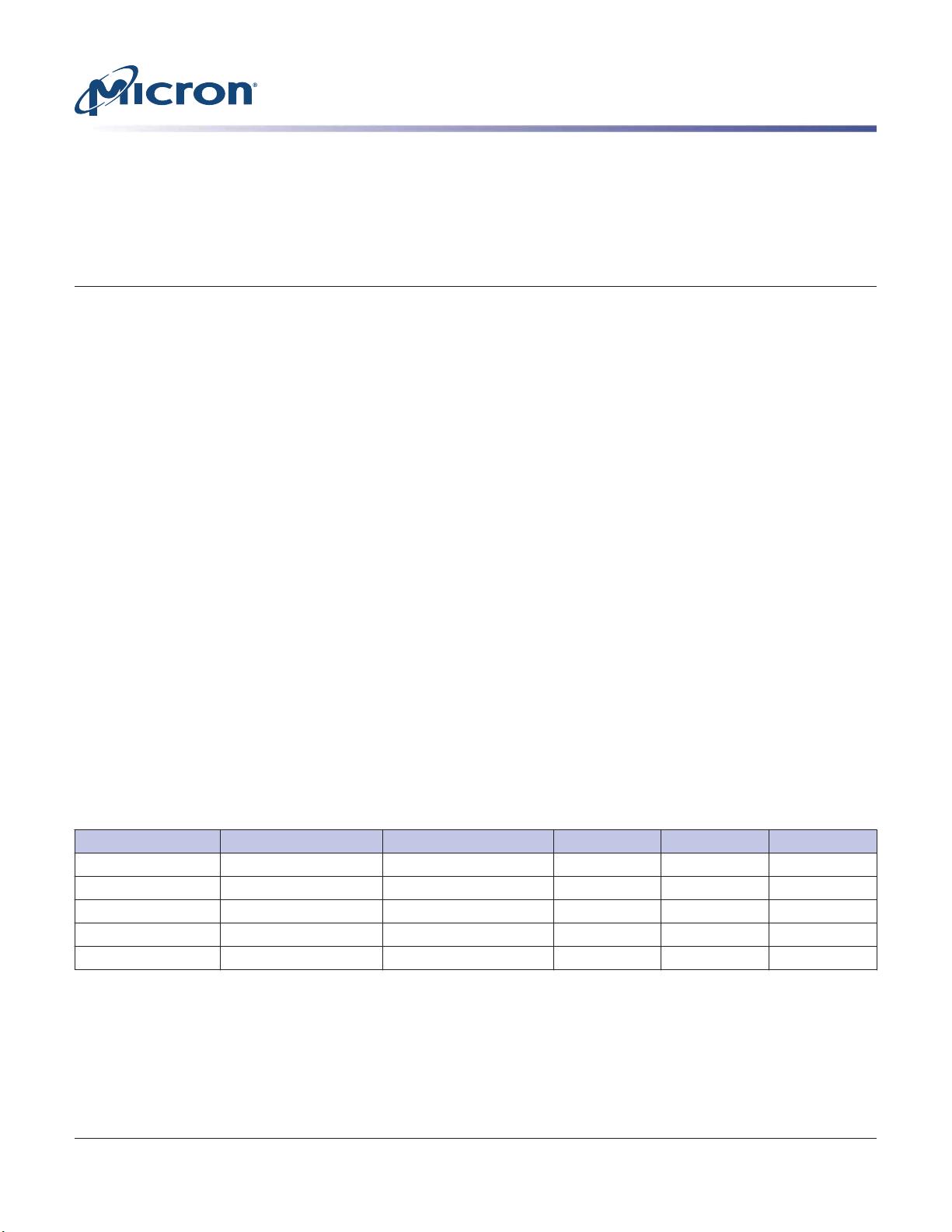

Speed Bin Tables ............................................................................................................................................ 73

Electrical Characteristics and AC Operating Conditions ................................................................................... 78

Command and Address Setup, Hold, and Derating ........................................................................................... 98

Data Setup, Hold, and Derating ...................................................................................................................... 106

Commands – Truth Tables ............................................................................................................................. 115

Commands ................................................................................................................................................... 118

DESELECT ................................................................................................................................................ 118

NO OPERATION ........................................................................................................................................ 118

ZQ CALIBRATION LONG ........................................................................................................................... 118

ZQ CALIBRATION SHORT .......................................................................................................................... 118

ACTIVATE ................................................................................................................................................. 118

READ ........................................................................................................................................................ 118

WRITE ...................................................................................................................................................... 119

PRECHARGE ............................................................................................................................................. 120

REFRESH .................................................................................................................................................. 120

SELF REFRESH .......................................................................................................................................... 121

DLL Disable Mode ..................................................................................................................................... 122

4Gb: x4, x8, x16 DDR3 SDRAM

Features

PDF: 09005aef8417277b

4Gb_DDR3_SDRAM.pdf - Rev. M 4/13 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2009 Micron Technology, Inc. All rights reserved.

gdsgdj2022-11-08不错,谢谢分享

gdsgdj2022-11-08不错,谢谢分享 c49822123302019-06-23谢谢分享。

c49822123302019-06-23谢谢分享。 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功