DDR SDRAM控制器verilog代码及中文说明文档(公司内部解禁

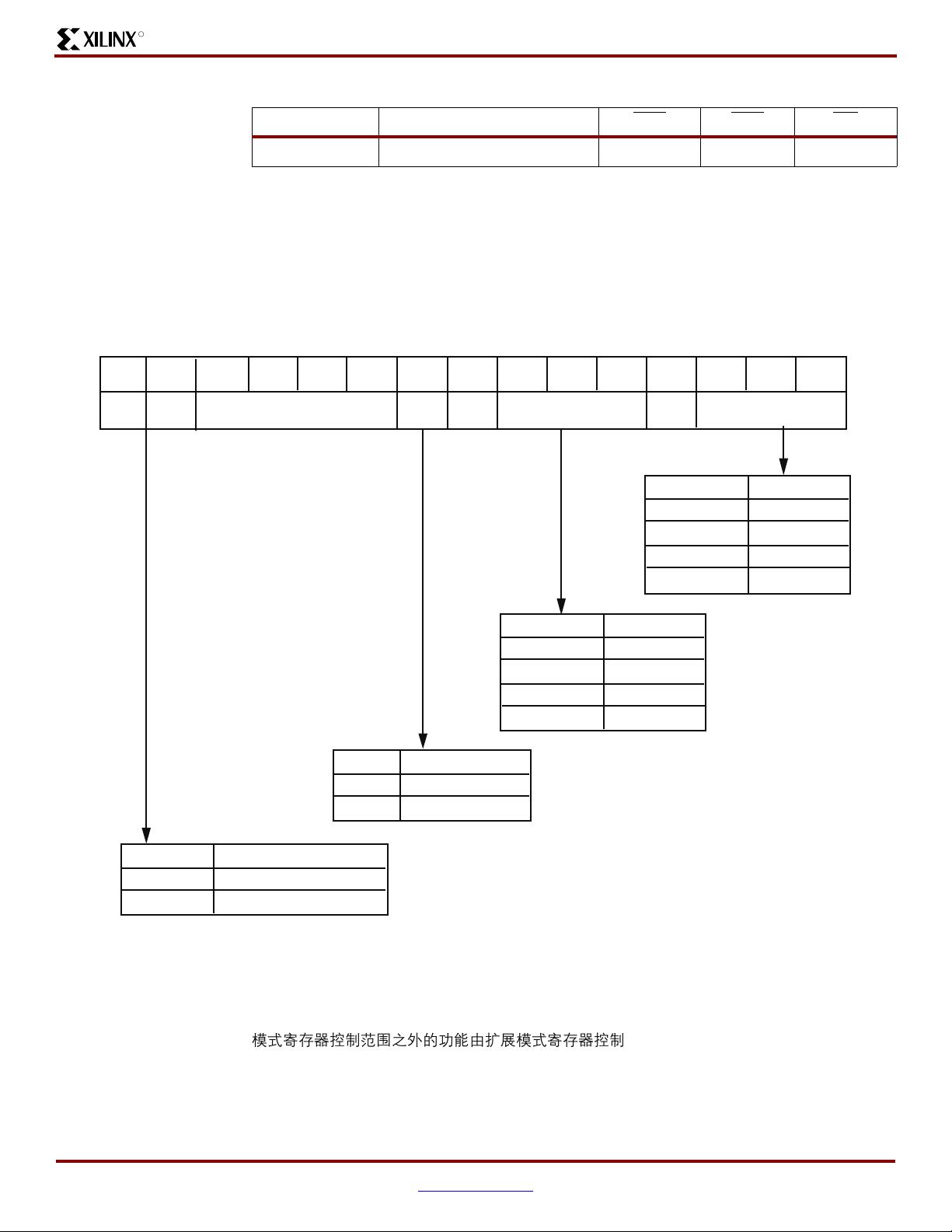

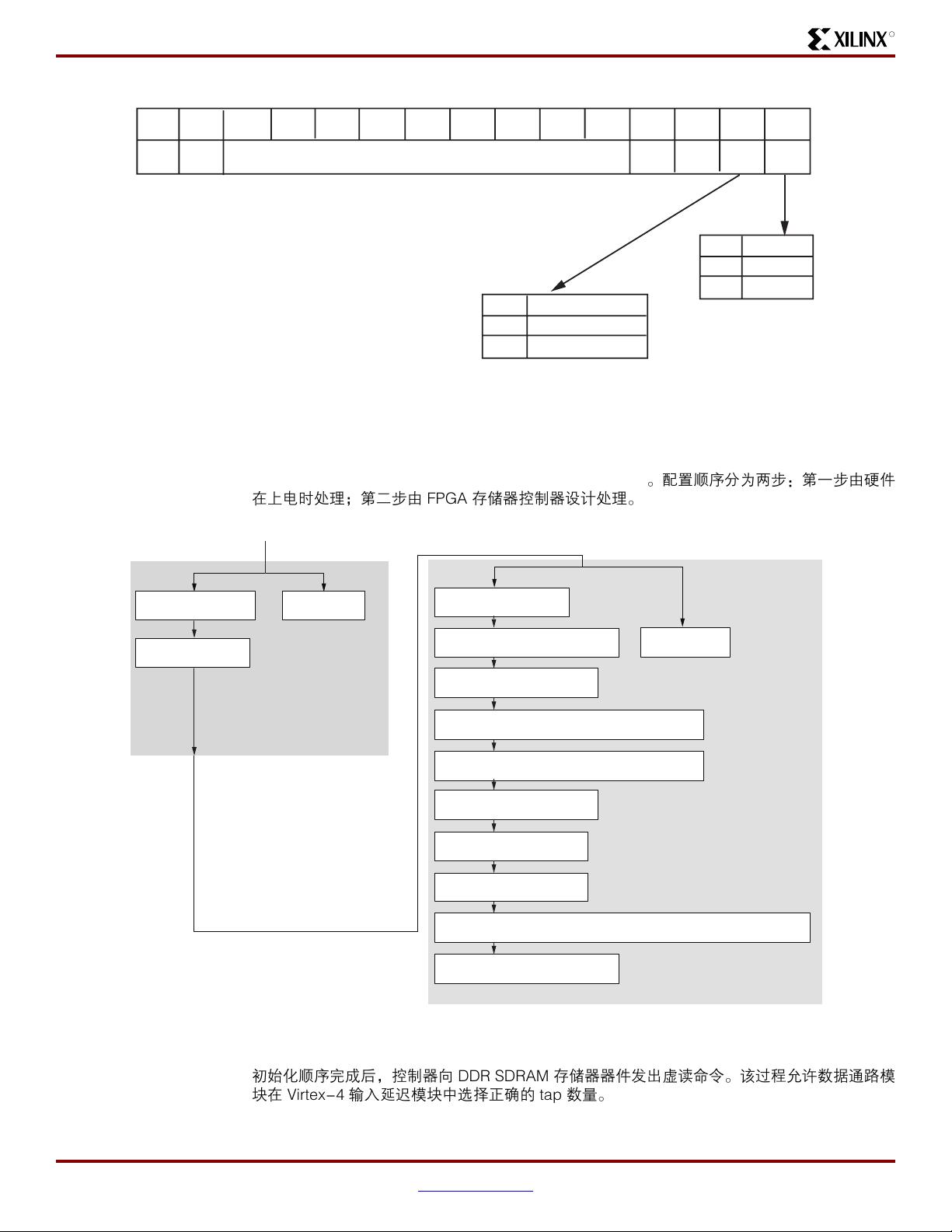

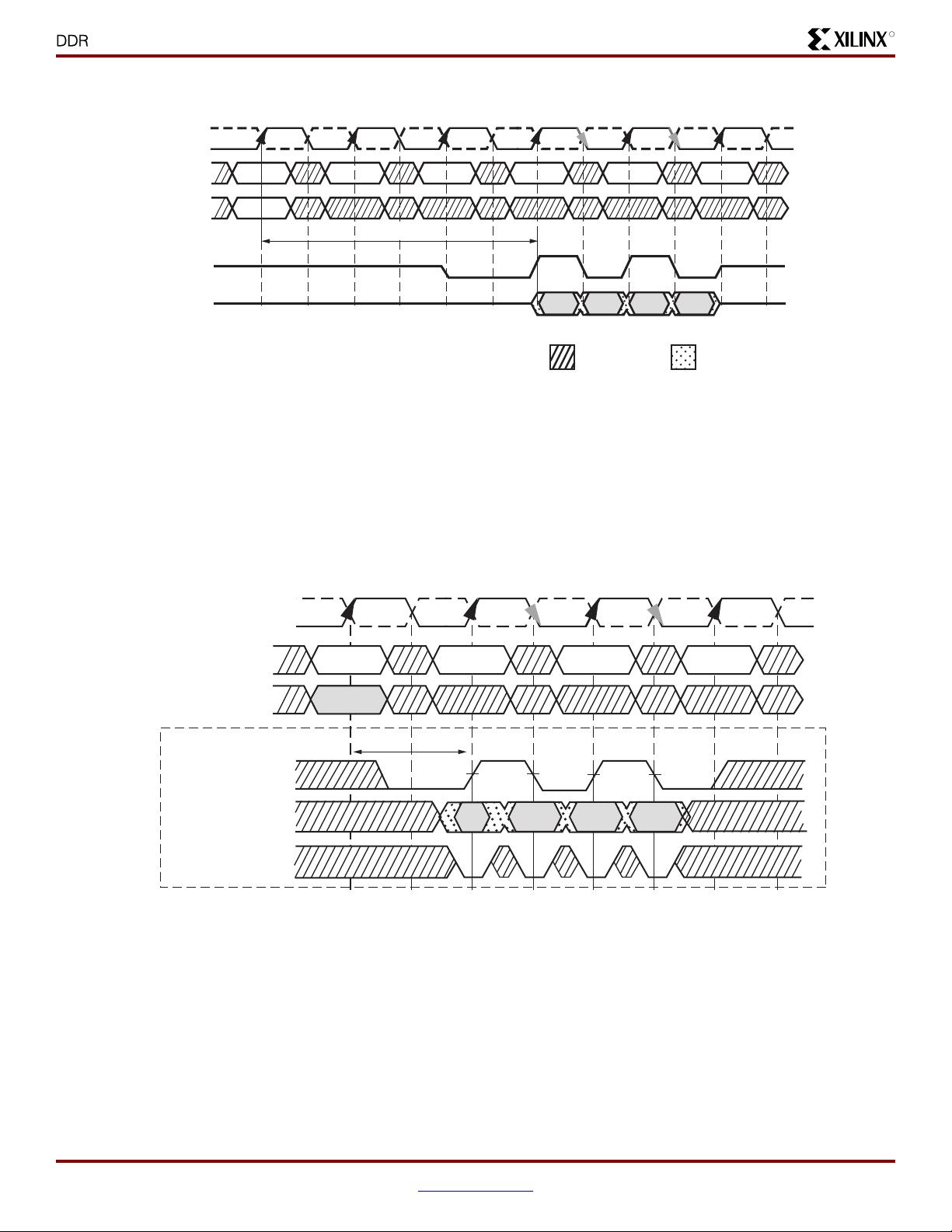

DDR SDRAM(Double Data Rate Synchronous Dynamic Random-Access Memory)是一种高速、同步的动态随机访问存储器,广泛应用于计算机系统中的内存模块。DDR SDRAM控制器是实现系统与DDR内存芯片间高效通信的关键组件,它负责管理和调度数据传输,确保数据在正确的时间、正确的时序下读写。 本资源包含一个DDR SDRAM控制器的Verilog代码实现,以及对应的中文说明文档,这对于理解DDR内存控制器的工作原理,以及学习如何用硬件描述语言(如Verilog)设计此类控制器,具有极大的价值。Verilog是一种广泛应用的硬件描述语言,它允许工程师用类似于编程的方式来描述数字系统的结构和行为。 DDR SDRAM控制器的Verilog代码通常会包含以下几个关键部分: 1. **时钟管理**:DDR SDRAM的操作依赖于精确的时钟信号。控制器需要生成合适的时钟边沿(上升沿和下降沿)来驱动数据传输,这涉及到DLL(Delay-Locked Loop)或者PLL(Phase-Locked Loop)的设计。 2. **地址生成与管理**:控制器需生成并管理内存地址,确保数据在正确的位置读写。这包括对行地址(Bank Address)、列地址(Column Address)的处理和预充电命令的生成。 3. **命令序列生成**:DDR SDRAM的操作需要一系列特定顺序的命令,如ACT(Activate)、RD(Read)、WR(Write)、PRE(Precharge)。控制器需要根据操作类型和当前内存状态生成这些命令。 4. **数据总线管理**:在数据传输期间,控制器需要控制数据总线的流向,确保数据在正确的时序上被读取或写入。这包括DQ(Data Bits)和DM(Data Mask)的管理。 5. **刷新控制**:DDR SDRAM需要定期进行刷新操作以保持数据完整性。控制器必须定时发出刷新命令,并管理刷新计时。 6. **错误检测与纠正**:高级的控制器可能还包括ECC(Error Correction Code)功能,用于检测和纠正内存中的数据错误。 中文说明文档通常会详细解释这些设计细节,包括代码逻辑、关键模块的功能、接口定义以及如何在实际FPGA或ASIC设计中集成和测试该控制器。对于初学者来说,阅读这样的文档可以帮助他们理解硬件描述语言的实际应用,提高数字系统设计能力。 这个资源为学习和实践DDR SDRAM控制器设计提供了宝贵的材料,无论是对硬件工程师还是对嵌入式系统开发者,都是极其有价值的学习资源。通过深入研究代码和文档,不仅可以了解DDR内存的工作机制,还能掌握Verilog编程技巧,为设计更复杂的数字系统打下坚实基础。

DDR SDRAM控制器verilog代码及中文说明文档(公司内部解禁).zip (33个子文件)

DDR SDRAM控制器verilog代码及中文说明文档(公司内部解禁).zip (33个子文件)  DDR SDRAM控制器verilog代码及中文说明文档(公司内部解禁)

DDR SDRAM控制器verilog代码及中文说明文档(公司内部解禁)  DDR SDRAM控制器源代码

DDR SDRAM控制器源代码  mem_interface_top_tap_ctrl_0.v 16KB

mem_interface_top_tap_ctrl_0.v 16KB mem_interface_top_test_bench_0.v 7KB

mem_interface_top_test_bench_0.v 7KB mem_interface_top_idelay_ctrl.v 1KB

mem_interface_top_idelay_ctrl.v 1KB mem_interface_top_tap_logic_0.v 5KB

mem_interface_top_tap_logic_0.v 5KB mem_interface_top_backend_rom_0.v 6KB

mem_interface_top_backend_rom_0.v 6KB mem_interface_top.v 3KB

mem_interface_top.v 3KB mem_interface_top_controller_iobs_0.v 4KB

mem_interface_top_controller_iobs_0.v 4KB mem_interface_top_top_0.v 11KB

mem_interface_top_top_0.v 11KB mem_interface_top_rd_wr_addr_fifo_0.v 4KB

mem_interface_top_rd_wr_addr_fifo_0.v 4KB mem_interface_top_pattern_compare8.v 6KB

mem_interface_top_pattern_compare8.v 6KB mem_interface_top_backend_fifos_0.v 4KB

mem_interface_top_backend_fifos_0.v 4KB mem_interface_top_data_tap_inc.v 4KB

mem_interface_top_data_tap_inc.v 4KB mem_interface_top_infrastructure_iobs_0.v 4KB

mem_interface_top_infrastructure_iobs_0.v 4KB mem_interface_top_rd_data_0.v 19KB

mem_interface_top_rd_data_0.v 19KB mem_interface_top_RAM_D_0.v 4KB

mem_interface_top_RAM_D_0.v 4KB mem_interface_top_v4_dq_iob.v 3KB

mem_interface_top_v4_dq_iob.v 3KB mem_interface_top_data_write_0.v 5KB

mem_interface_top_data_write_0.v 5KB mem_interface_top_ddr_controller_0.v 53KB

mem_interface_top_ddr_controller_0.v 53KB mem_interface_top_data_path_0.v 4KB

mem_interface_top_data_path_0.v 4KB mem_interface_top_user_interface_0.v 4KB

mem_interface_top_user_interface_0.v 4KB mem_interface_top_rd_data_fifo_0.v 7KB

mem_interface_top_rd_data_fifo_0.v 7KB mem_interface_top_data_path_iobs_0.v 56KB

mem_interface_top_data_path_iobs_0.v 56KB mem_interface_top_v4_dm_iob.v 2KB

mem_interface_top_v4_dm_iob.v 2KB mem_interface_top_parameters_0.v 4KB

mem_interface_top_parameters_0.v 4KB mem_interface_top_cmp_rd_data_0.v 6KB

mem_interface_top_cmp_rd_data_0.v 6KB mem_interface_top_main_0.v 5KB

mem_interface_top_main_0.v 5KB mem_interface_top_infrastructure.v 4KB

mem_interface_top_infrastructure.v 4KB mem_interface_top_wr_data_fifo_16.v 2KB

mem_interface_top_wr_data_fifo_16.v 2KB mem_interface_top_data_gen_16.v 7KB

mem_interface_top_data_gen_16.v 7KB mem_interface_top_addr_gen_0.v 5KB

mem_interface_top_addr_gen_0.v 5KB mem_interface_top_iobs_0.v 5KB

mem_interface_top_iobs_0.v 5KB mem_interface_top_v4_dqs_iob.v 3KB

mem_interface_top_v4_dqs_iob.v 3KB 使用 Virtex-4 FPGA 器件实现DDR SDRAM控制器.pdf 625KB

使用 Virtex-4 FPGA 器件实现DDR SDRAM控制器.pdf 625KB- 1

- 粉丝: 2

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 09MnNiDR钢制低温压力容器焊接工艺的确定.pdf

- 09MnNiDR钢制球罐用W707DRQ焊条焊接性能 - .pdf

- 09MnNiDR低温压力容器钢板的试验及焊接检验.pdf

- 9Ni钢低温储罐焊接工艺研究.pdf

- 9Cr与CrMoV异种焊接接头疲劳裂纹扩展门槛值研究.pdf

- 10CrMo910耐热钢的焊接工艺.pdf

- 10CrMo910炉管焊接.pdf

- 10Ni3MoVD锻件焊接裂纹敏感性试验研究.pdf

- 10t电动单梁桥式起重机主梁焊接变形的控制 - .pdf

- 10CrNi3MoV钢双面双弧焊接头组织与性能研究 - .pdf

- 10焊接工字形钢轴压构件截面设计的直接算法.pdf

- 10吨级叉车驱动桥体焊接工艺设计 - .pdf

- 10T级后桥焊接工艺分析.pdf

- 10万m 3原油储罐底板现场焊接及变形控制.pdf

- 10万m3大型原油储罐底板焊接质量控制分析.pdf

- 10万m3原油储罐典型焊接质量缺陷分析与处理.pdf

信息提交成功

信息提交成功

- 1

- 2

前往页