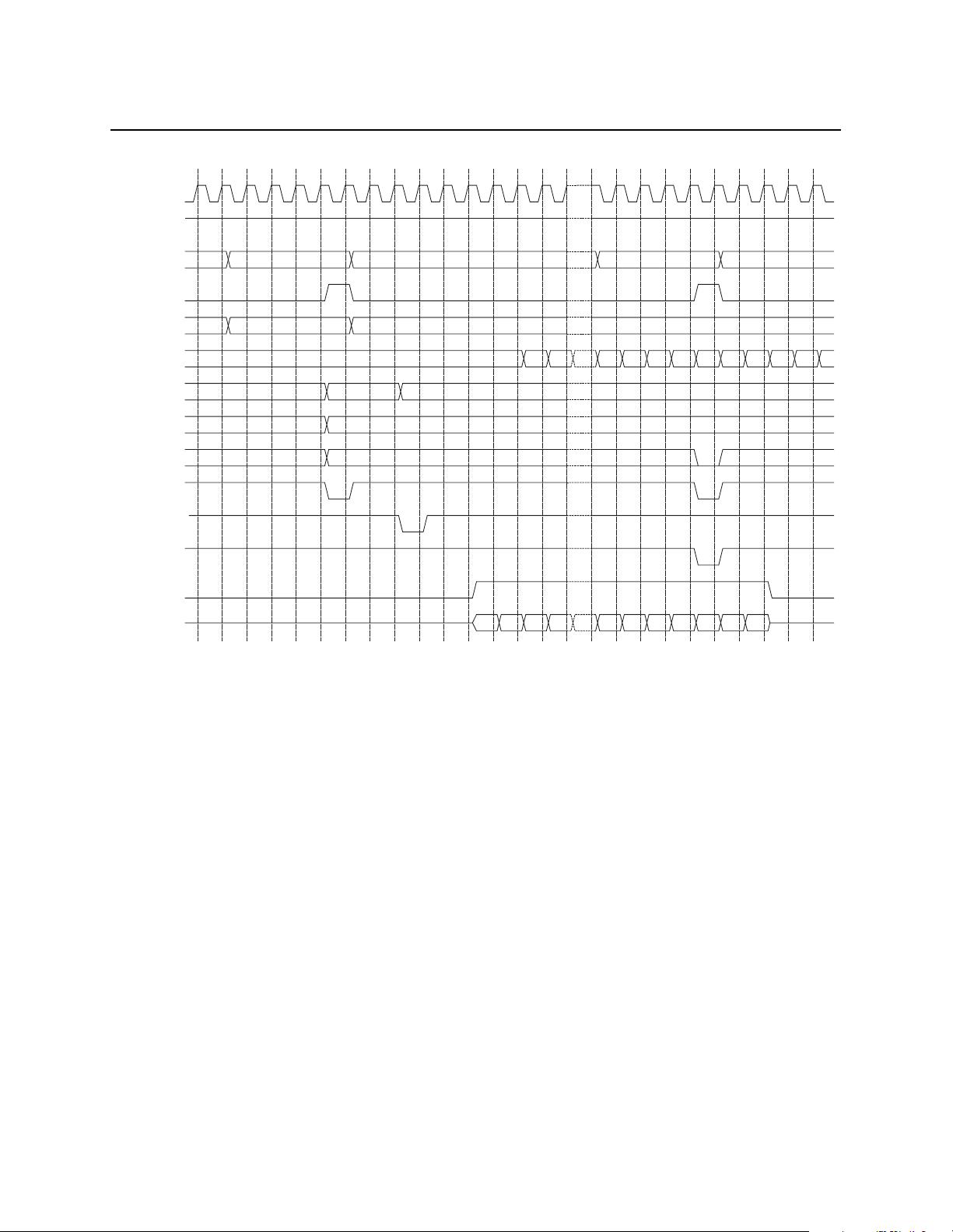

SDRAM(Synchronous Dynamic Random-Access Memory)同步动态随机访问内存是一种常见的系统内存,它以时钟信号同步操作,提供高速数据传输。在 FPGA(Field-Programmable Gate Array)设计中,为了与SDRAM进行通信,需要一个专门的SDRAM控制器。本篇文章将详细介绍如何使用Verilog语言编写一个功能完善的SDRAM控制器。 Verilog是一种硬件描述语言,用于描述数字系统的逻辑行为,包括CPU、存储器控制器等。编写SDRAM控制器,主要涉及以下知识点: 1. **SDRAM时序**:理解SDRAM的时序是编写控制器的基础。这包括地址预充电、行激活、列选择、读写操作等。例如,控制器需要在正确的时间点发出命令,如RAS(行地址选通)、CAS(列地址选通)和CS(片选)信号。 2. **地址映射**:控制器需要将系统地址空间映射到SDRAM的物理地址上,处理地址线的分页和bank选择。 3. **刷新管理**:SDRAM需要定期刷新以保持数据的完整性,控制器需定时发送刷新命令。 4. **数据缓冲和同步**:由于SDRAM和FPGA内部逻辑速度不匹配,需要数据缓冲区进行同步,通常采用双口RAM实现。 5. **命令序列**:SDRAM的操作通常由一系列命令组成,如初始化、预充电、加载模式寄存器、读写等,控制器需要按照正确的顺序和时间间隔发出这些命令。 6. **时钟管理和DLL(Delay-Locked Loop)**:由于SDRAM时钟通常与系统时钟不同,控制器需要能够处理时钟域之间的转换。DLL用于调整时钟延迟,确保数据的准确同步。 7. **错误检测与处理**:控制器应包含错误检测机制,如读取数据的奇偶校验,以确保数据的正确性。 8. **仿真与验证**:在实际编写代码之前,通过行为模型进行仿真,验证控制器的功能和性能。使用工具如ModelSim或Vivado Simulator进行验证。 9. **综合与实现**:完成Verilog代码后,使用综合工具(如Synopsys的Design Compiler或Xilinx的Vivado)将其转换为逻辑门级网表,然后在FPGA上实现。 10. **硬件调试**:通过JTAG接口或其他调试工具进行硬件调试,检查SDRAM控制器的实际工作情况,确保其在真实环境中的正确运行。 在"基于FPGA对SDRAM控制器的设计(VERILOG语言)"这个压缩包中,可能包含了详细的Verilog代码实现,以及相关的仿真波形、测试平台和文档说明,这些都是学习和理解SDRAM控制器设计的重要资源。通过分析和研究这些文件,可以深入理解上述知识点,并掌握实际的Verilog编程技巧。同时,这样的项目也提供了动手实践的机会,帮助提升FPGA设计能力。

SDRAM控制器(用Verilog编写) (208个子文件)

SDRAM控制器(用Verilog编写) (208个子文件)  _info 15KB

_info 15KB verilog.asm 805KB

verilog.asm 805KB verilog.asm 736KB

verilog.asm 736KB verilog.asm 586KB

verilog.asm 586KB verilog.asm 583KB

verilog.asm 583KB verilog.asm 536KB

verilog.asm 536KB verilog.asm 266KB

verilog.asm 266KB verilog.asm 262KB

verilog.asm 262KB verilog.asm 256KB

verilog.asm 256KB verilog.asm 244KB

verilog.asm 244KB verilog.asm 210KB

verilog.asm 210KB verilog.asm 193KB

verilog.asm 193KB verilog.asm 172KB

verilog.asm 172KB verilog.asm 152KB

verilog.asm 152KB verilog.asm 144KB

verilog.asm 144KB verilog.asm 142KB

verilog.asm 142KB verilog.asm 141KB

verilog.asm 141KB verilog.asm 138KB

verilog.asm 138KB verilog.asm 115KB

verilog.asm 115KB verilog.asm 96KB

verilog.asm 96KB verilog.asm 85KB

verilog.asm 85KB verilog.asm 78KB

verilog.asm 78KB verilog.asm 76KB

verilog.asm 76KB verilog.asm 72KB

verilog.asm 72KB verilog.asm 62KB

verilog.asm 62KB verilog.asm 58KB

verilog.asm 58KB verilog.asm 53KB

verilog.asm 53KB verilog.asm 52KB

verilog.asm 52KB verilog.asm 43KB

verilog.asm 43KB verilog.asm 37KB

verilog.asm 37KB verilog.asm 37KB

verilog.asm 37KB verilog.asm 35KB

verilog.asm 35KB verilog.asm 32KB

verilog.asm 32KB verilog.asm 29KB

verilog.asm 29KB verilog.asm 28KB

verilog.asm 28KB verilog.asm 27KB

verilog.asm 27KB verilog.asm 26KB

verilog.asm 26KB verilog.asm 24KB

verilog.asm 24KB verilog.asm 24KB

verilog.asm 24KB verilog.asm 23KB

verilog.asm 23KB verilog.asm 22KB

verilog.asm 22KB verilog.asm 21KB

verilog.asm 21KB verilog.asm 21KB

verilog.asm 21KB verilog.asm 19KB

verilog.asm 19KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 15KB

verilog.asm 15KB verilog.asm 14KB

verilog.asm 14KB verilog.asm 13KB

verilog.asm 13KB verilog.asm 13KB

verilog.asm 13KB verilog.asm 11KB

verilog.asm 11KB verilog.asm 9KB

verilog.asm 9KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 8KB

verilog.asm 8KB verilog.asm 6KB

verilog.asm 6KB verilog.asm 5KB

verilog.asm 5KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 4KB

verilog.asm 4KB verilog.asm 2KB

verilog.asm 2KB verilog.asm 2KB

verilog.asm 2KB verilog.asm 1KB

verilog.asm 1KB verilog.asm 1KB

verilog.asm 1KB verilog.asm 1KB

verilog.asm 1KB verilog.asm 1KB

verilog.asm 1KB _primary.dat 71KB

_primary.dat 71KB _primary.dat 51KB

_primary.dat 51KB _primary.dat 46KB

_primary.dat 46KB _primary.dat 46KB

_primary.dat 46KB _primary.dat 30KB

_primary.dat 30KB _primary.dat 29KB

_primary.dat 29KB _primary.dat 27KB

_primary.dat 27KB _primary.dat 18KB

_primary.dat 18KB _primary.dat 18KB

_primary.dat 18KB _primary.dat 17KB

_primary.dat 17KB _primary.dat 16KB

_primary.dat 16KB _primary.dat 15KB

_primary.dat 15KB _primary.dat 14KB

_primary.dat 14KB _primary.dat 13KB

_primary.dat 13KB _primary.dat 12KB

_primary.dat 12KB _primary.dat 11KB

_primary.dat 11KB _primary.dat 10KB

_primary.dat 10KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 6KB

_primary.dat 6KB _primary.dat 6KB

_primary.dat 6KB _primary.dat 6KB

_primary.dat 6KB _primary.dat 5KB

_primary.dat 5KB _primary.dat 5KB

_primary.dat 5KB _primary.dat 5KB

_primary.dat 5KB _primary.dat 4KB

_primary.dat 4KB _primary.dat 4KB

_primary.dat 4KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB _primary.dat 3KB

_primary.dat 3KB- 1

- 2

- 3

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 贵阳市五险一金办事指南.docx

- 三亚市五险一金办事指南.docx

- 秦皇岛市五险一金办事指南.docx

- 张北市五险一金办事指南.docx

- 焦作市五险一金办事指南.docx

- Erlang26.2.5.4+RabbitMQ3.13.7及4.0.2

- 通化市五险一金办事指南.docx

- 昆山市五险一金办事指南.docx

- 常熟市五险一金办事指南.docx

- python作业资料代码文件.zip

- java项目,课程设计-springboot学生综合测评系统

- ChristmasTree.html

- 营口市五险一金办事指南.docx

- 济南市五险一金办事指南.docx

- 潍坊市五险一金办事指南.docx

- 晋中市五险一金办事指南.docx

信息提交成功

信息提交成功

- 1

- 2

- 3

- 4

- 5

前往页