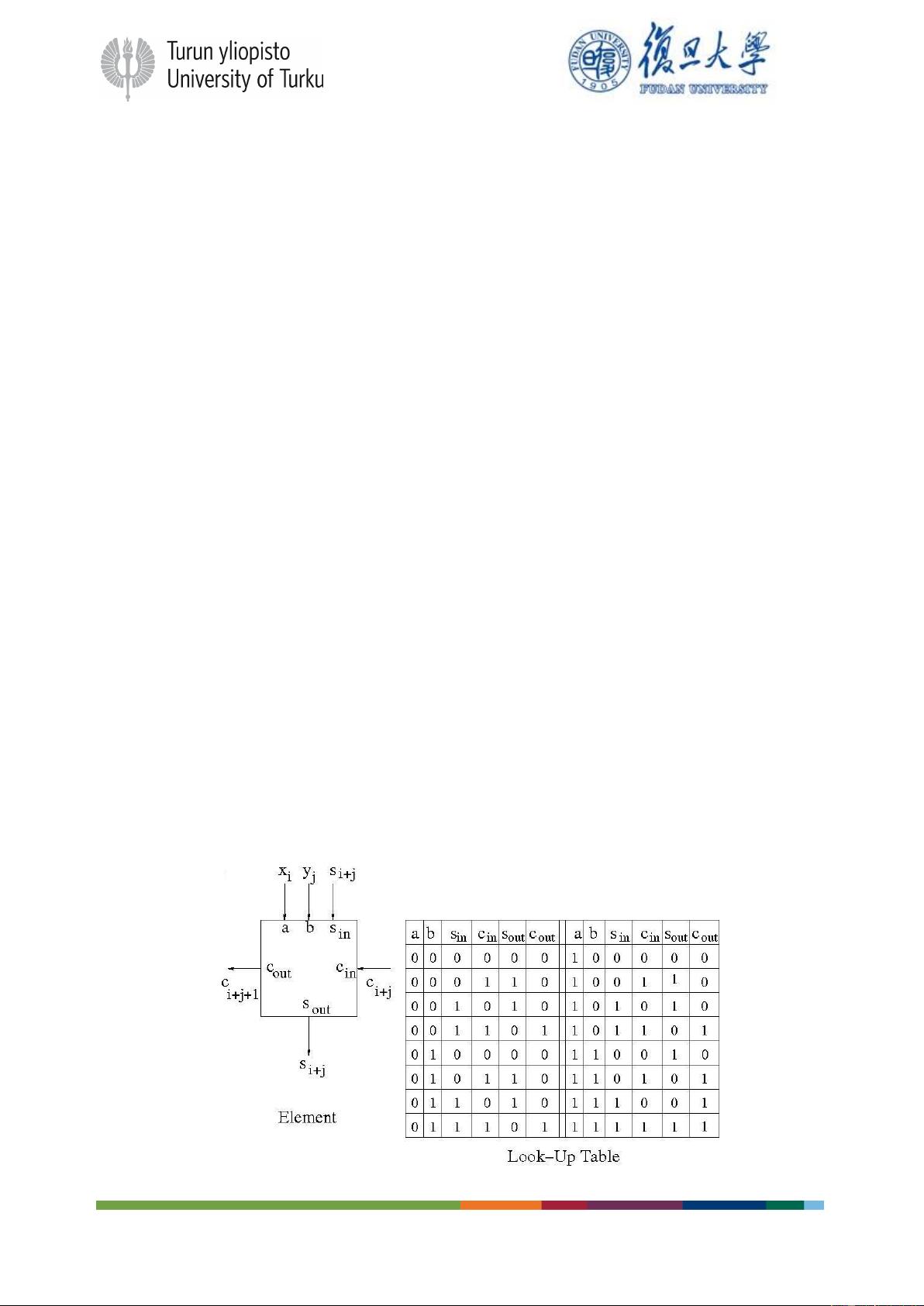

在数字电路设计领域,VHDL(Very High-Speed Integrated Circuit Hardware Description Language)是一种重要的硬件描述语言,用于描述数字系统的逻辑功能、行为和结构。本文将深入探讨如何使用VHDL来实现任意N位和M位的乘法器,并基于描述中的内容进行详细解释。 让我们理解乘法器的基本原理。乘法器是数字电路中的基本元件,其功能是将两个二进制数相乘。在VHDL中,我们可以设计出灵活的乘法器结构,使得乘数和被乘数的位数可以通过参数动态设定,从而实现“任意N位和M位”的乘法器。这种设计方法的灵活性在于,它允许我们根据需要调整输入位宽,而不必为每种特定宽度创建一个独立的实体。 VHDL的设计通常包括实体和结构体两部分。实体定义了模块的外部接口,包括输入和输出信号;结构体则描述了内部的工作原理和连接方式。在实现任意位宽的乘法器时,我们可能需要定义以下参数: 1. `N`:被乘数的位数。 2. `M`:乘数的位数。 然后,我们会在实体中声明这些参数以及输入(如`A`和`B`,分别代表N位和M位的二进制数)和输出(如`P`,代表乘积)信号。结构体中,我们可以采用分治策略,将乘法器分解为多个较小的乘法单元,如半加器和全加器,它们会根据位宽自动组合。 描述中的"任意N位和M位的乘法器VHDL实现(代码)"可能包含以下步骤: 1. **位扩展**:为了将乘法转化为位并行的加法,需要将较短的二进制数进行位扩展,使其与较长的二进制数长度相同。 2. **逐位相乘**:接下来,对每个位进行逐位乘法,这可以通过一系列的与门(AND gate)完成,产生一系列中间结果。 3. **累加器**:这些中间结果随后需要被累积起来。可以使用累加器结构,如串行进位加法器,对这些结果进行求和。这个过程涉及到多次进位,因此可能需要嵌套的全加器结构。 4. **Testbench**:测试平台(Testbench)是验证设计正确性的关键部分。通过编写Testbench,可以模拟不同的输入值并检查输出是否符合预期,确保乘法器的功能正确无误。 5. **综合和仿真**:完成设计后,使用EDA工具(如Xilinx Vivado, Altera Quartus等)进行综合和仿真,将VHDL代码转换为逻辑门级表示,并验证其在实际硬件上的行为。 总结来说,"任意N位和M位的乘法器VHDL实现"是一个高级的数字逻辑设计项目,涉及到VHDL编程、参数化设计、位扩展、逐位乘法、累加器构造以及测试平台的编写。这样的设计不仅有助于理解数字系统的工作原理,而且在 FPGA 或 ASIC 设计中具有实际应用价值,因为它们能适应不同位宽的需求,提高硬件资源的利用率。

任意N位和M位的乘法器VHDL实现(代码).rar (8个子文件)

任意N位和M位的乘法器VHDL实现(代码).rar (8个子文件)  任意N位和M位的乘法器VHDL实现(代码)

任意N位和M位的乘法器VHDL实现(代码)  任意N位和M位的乘法器VHDL实现(代码)

任意N位和M位的乘法器VHDL实现(代码)  Title.pdf 195KB

Title.pdf 195KB CODE

CODE  Multiplier_4x4_sources.f 61B

Multiplier_4x4_sources.f 61B Multiplier_4x4_tb.vhd 3KB

Multiplier_4x4_tb.vhd 3KB bit_multiplier.vhd 543B

bit_multiplier.vhd 543B Multiplier_NxM.vhd 3KB

Multiplier_NxM.vhd 3KB Multiplier_4x4.vhd 3KB

Multiplier_4x4.vhd 3KB Multiplier_NxM_sources.f 61B

Multiplier_NxM_sources.f 61B Multiplier_NxM_tb.vhd 2KB

Multiplier_NxM_tb.vhd 2KB- 1

wonderfulchips2017-09-27感谢,超棒的资源!

wonderfulchips2017-09-27感谢,超棒的资源!

- 粉丝: 9

- 资源: 35

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- AllSort(直接插入排序,希尔排序,选择排序,堆排序,冒泡排序,快速排序,归并排序)

- 模拟qsort,改造冒泡排序使其能排序任意数据类型,即日常练习

- 数组经典习题之顺序排序和二分查找和冒泡排序

- 基于 Oops Framework 提供的游戏项目开发模板,项目中提供了最新版本 Cocos Creator 3.x 插件与游戏资源初始化通用逻辑

- live-ai这是一个深度学习的资料

- FeiQ.rar 局域网内通信服务软件

- 172.16.100.195

- 光储并网simulink仿真模型,直流微电网 光伏系统采用扰动观察法是实现mppt控制,储能可由单独蓄电池构成,也可由蓄电池和超级电容构成的混合储能系统,并采用lpf进行功率分配 并网采用pq控制

- python编写微信读取smart200plc的数据发送给微信联系人

- 光储并网VSG系统Matlab simulink仿真模型,附参考文献 系统前级直流部分包括光伏阵列、变器、储能系统和双向dcdc变器,后级交流子系统包括逆变器LC滤波器,交流负载 光储并网VSG系

信息提交成功

信息提交成功