实验报告

1、基本门电路

一、实验目的

1、了解基于 Verilog 的基本门电路的设计及其验证。

2、熟悉利用 EDA 工具进行设计及仿真的流程。

3 、 学 习 针 对 实 际 门 电 路 芯 片

74HC00、74HC02、74HC04、74HC08、74HC32、74HC86 进行 VerilogHDL 设计的方

法。

4、掌握 Libero 软件的使用方法。

二、实验环境

Libero 仿真软件。

三、实验内容

1、在自己的工程文件中,新建一个设计代码文件(Verilog Source File),文件命

名规则:学号+下划线+BasGate

例:3115000001_BasGate.v

在自己的工程文件中,新建一个测试平台文件(HDL Stimulus File),文件命名规

则:test_BasGate.v

2、进行针对 74 系列基本门电路的设计,并完成相应的仿真实验。

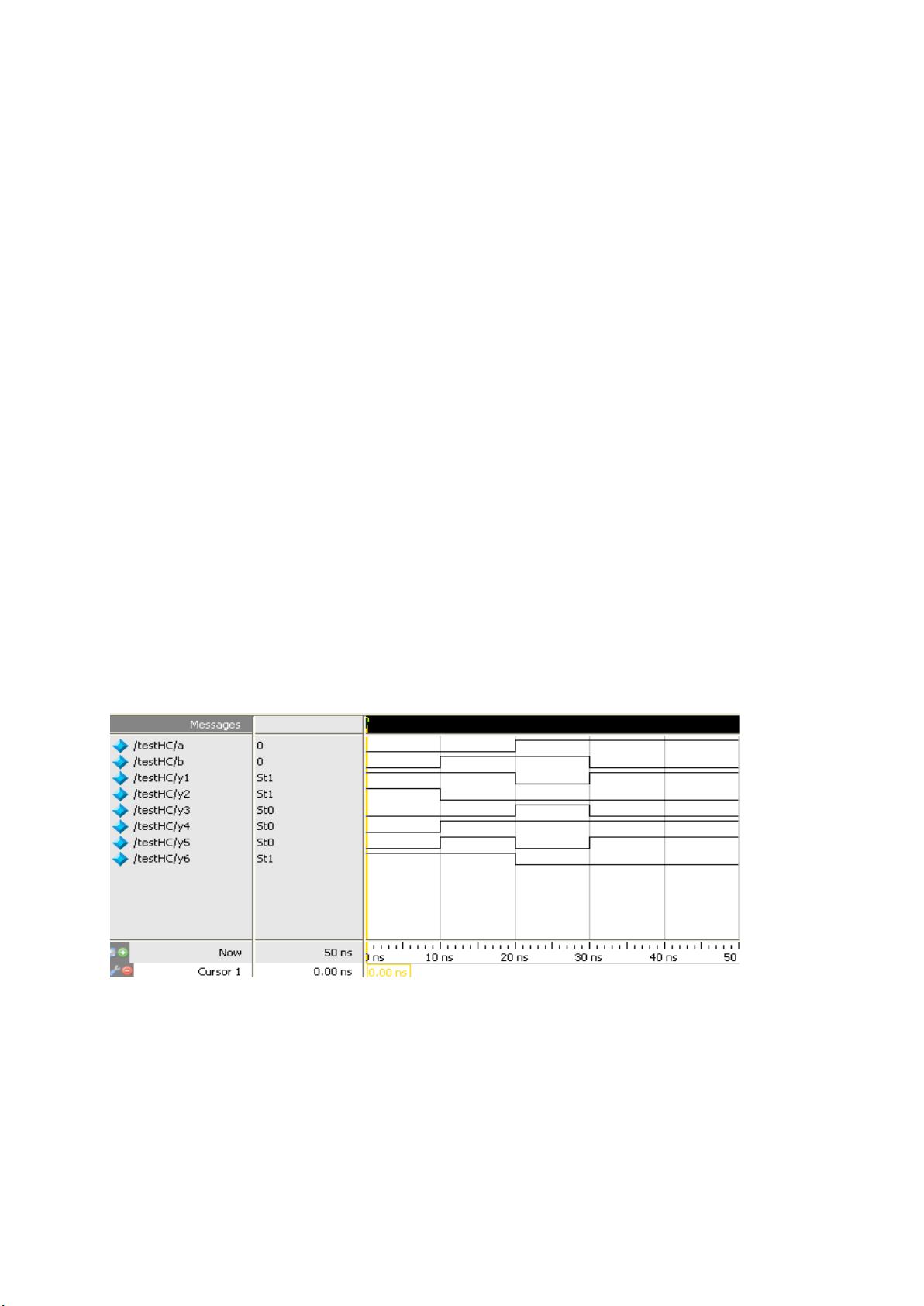

3、参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成 2 输入

与非门、2 输入或非门、2 输入与门、2 输入或门、2 输入异或门、非门的设计、综合

及仿真。

4、提交针对基本门电路的综合结果,以及相应的仿真结果。

四、实验结果和数据处理

1、门电路模块清单及测试平台代码清单

(1)所有硬件功能模块的代码清单(关键代码应有注释)

// 3115005595_BasGate.v

module HC(a, b, y1, y2, y3, y4, y5, y6);

input a, b;

output y1, y2, y3, y4, y5, y6;

assign y1 = ~(a&b);

1

评论1