张俊鸿_基于Libero的数字逻辑设计仿真及验证实验实验报告(2020_1)1

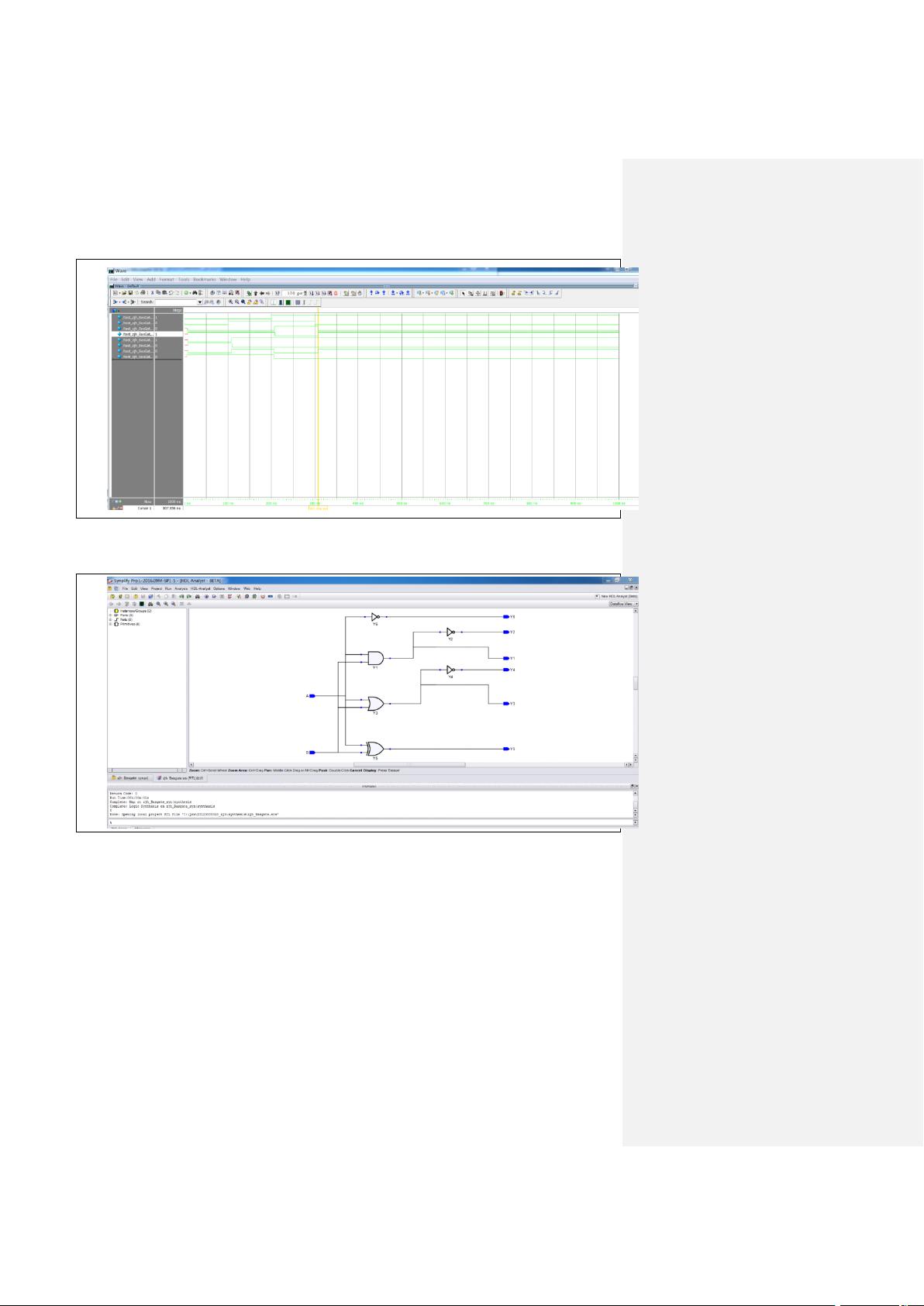

【基于Libero的数字逻辑设计仿真及验证实验】 在本次实验中,主要目的是学习和掌握数字逻辑设计的基础知识,特别是如何使用Libero软件进行Verilog HDL的设计、仿真和验证。实验者张俊鸿通过一系列步骤,实现了基本门电路的设计,并在Libero SoC环境下进行了完整的流程操作。 1. **实验内容** - 实验者创建了一个新的设计文件(Verilog Source File),遵循特定的命名规则,如3120005043_BasGate.v(学号+设计功能描述)。 - 接着,创建了测试平台文件(HDL Stimulus File),命名为test_BasGate.v,用于功能仿真。 - 在设计文件中,实验者定义了一个功能模块,例如zjh_BasGate,包含两个输入信号A和B,六个输出信号Y1到Y6,分别对应不同的逻辑运算。 - 测试平台模块(test_zjh_BasGate)被用来验证功能模块的正确性,通过设定不同的输入值进行仿真。 - 经过综合后,实验者对设计模块进行了布局布线,并进行了布局布线后的仿真,以检验实际硬件实现的效果。 - 实验者还进行了烧录和实物接电测试,以确保设计的门电路在硬件上也能正常工作。 2. **实验步骤** - 设计阶段,使用Verilog HDL编写门电路模块,例如实现与、与非、或、或非、异或和非等基本逻辑操作。 - 功能仿真阶段,通过测试平台模块模拟输入信号的变化,观察输出是否符合预期逻辑。 - 综合阶段,将Verilog代码转化为适合FPGA或ASIC的硬件描述语言,以优化逻辑资源。 - 布局布线阶段,确定逻辑单元在物理芯片上的位置和连接,以减少延迟并优化性能。 - 仿真验证阶段,检查综合和布局布线后的逻辑功能是否保持不变,同时关注信号延迟。 3. **实验结果分析** - 综合前仿真显示了设计的逻辑功能,没有明显的延迟。 - 综合后仿真和布局布线后的仿真表明存在约0.3ns的延迟,这是由于硬件实现的固有延迟。 - 改变布局布线的引脚分配会影响信号延迟,因为不同的物理路径可能导致不同的延迟时间。 通过这个实验,张俊鸿掌握了基于Libero SoC的数字逻辑设计过程,包括Verilog HDL编程、EDA工具的使用以及硬件实现的考虑。这为后续的数字逻辑设计和验证打下了坚实的基础,如组合逻辑电路、时序逻辑电路、有限状态机等更复杂的系统设计。

剩余46页未读,继续阅读

- 粉丝: 37

- 资源: 351

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- C#ASP.NET企业在线记账平台源码数据库 SQL2012源码类型 WebForm

- PHP客户关系CRM管理系统源码数据库 MySQL源码类型 WebForm

- python-勇者斗恶龙 回合制游戏 有图有真相 英雄和怪兽行为和状态的设定

- JAVA的Springboot垃圾分类识别小程序源码带部署文档数据库 MySQL源码类型 WebForm

- 图像分类数据集:番茄叶片病害图像识别数据集(包括划分好的数据【文件夹保存】、类别字典文件)

- web版本实现迅飞语音听写(流式版)封装代码

- JAVAspringboot校园转转二手电商市场源码数据库 MySQL源码类型 WebForm

- MICO_Android_Release_2_4_54.apk

- 个人日常总结,待整理 杂乱的笔记

- liteidex38.3-win64

信息提交成功

信息提交成功