"EDA设计实验报告"

本实验报告涵盖了数字逻辑基础设计仿真及验证的基本概念和方法。实验旨在让学生了解基于 Verilog 的基本门电路的设计及其验证,熟悉利用 EDA 工具进行设计及仿真的流程,并学习针对实际门电路芯片 74HC00、74HC02、74HC04、74HC08、74HC32、74HC86 进行 VerilogHDL 设计的方法。

一、实验目的

* 了解基于 Verilog 的基本门电路的设计及其验证

* 熟悉利用 EDA 工具进行设计及仿真的流程

* 学习针对实际门电路芯片 74HC00、74HC02、74HC04、74HC08、74HC32、74HC86 进行 VerilogHDL 设计的方法

* 熟悉实验箱的使用和程序下载(烧录)及测试的方法

二、实验环境及仪器

* Libero 仿真软件

* 数字逻辑与系统设计实验箱及烧录器

三、实验内容

* 掌握 Libero 软件的使用方法

* 进行针对 74 系列基本门电路的设计,并完成相应的仿真实验

* 参考教材中相应章节的设计代码、测试平台代码(可自行编程),完成 74HC00、74HC02、74HC04、74HC08、74HC32、74HC86 相应的设计、综合及仿真

* 提交针对 74HC00、74HC02、74HC04、74HC08、74HC32、74HC86 的综合结果,以及相应的仿真结果

四、实验结果和数据处理

* 74HC00 表 1:输入输出状态、逻辑状态

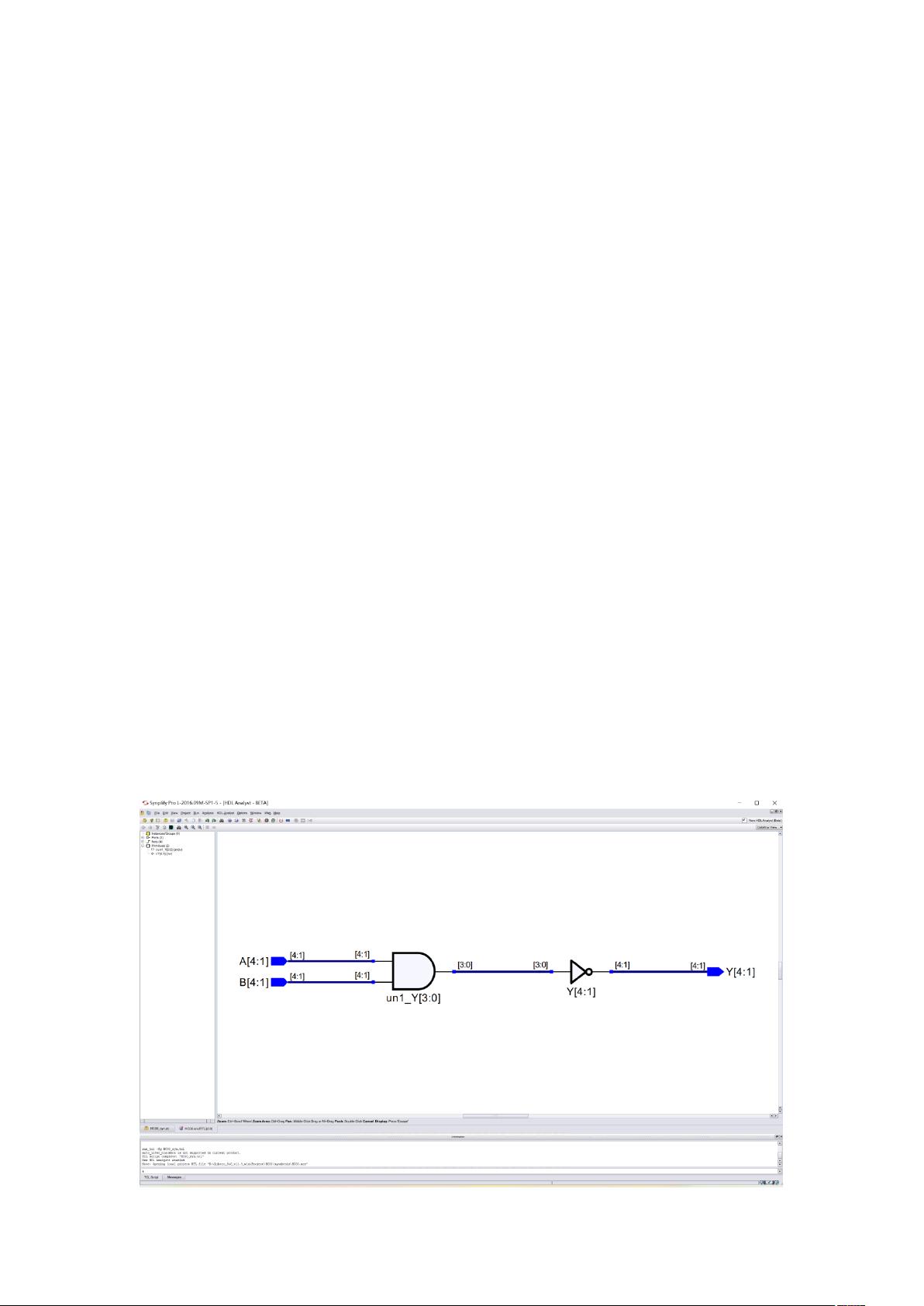

* Verilog 代码:module HC00(A,B,Y); input [4:1]A,B; output [4:1]Y; assign Y=~(A&B); endmodule

* 测试平台代码:`timescale 1ns/100ps module testbench; reg[3:0]a,b; wire [3:0]y; HC00 u1(a,b,y); initial begin ... end endmodule

* RTL view:technology view:综合前仿真:综合后仿真:布局布线后仿真:

* 74HC02 表 2:输入输出状态、逻辑状态

* Verilog 代码:module HC02( A,B,Y ); input A,B; output Y; assign Y=~(A|B); endmodule

* 测试平台代码:`timescale 1ns/100ps module testbench; reg a,b; wire y; HC02 u1(a,b,y); initial begin ... end endmodule

* RTL view:technology view:综合前仿真:综合后仿真:布局布线后仿真:

* 74HC04 表 3:输入输出状态、逻辑状态

* Verilog 代码:module HC04( A,Y ); input A; output Y ; assign Y=~A; endmodule

* 测试平台代码:`timescale 1ns/100ps module testbench; reg A; wire Y; HC04 u1(A,Y); initial begin ... end endmodule

* RTL view:technology view:综合前仿真:综合后仿真:布局布线后仿真:

* 74HC08 表 4:输入输出状态、逻辑状态

* Verilog 代码:module HC08(A,B,Y); input A,B; output Y; assign Y=A&B; endmodule

* 测试平台代码:`timescale 1ns/100ps module testbench; reg A,B; wire Y; HC08 u1(A,B,Y); initial begin ... end endmodule

* RTL view:technology view:综合前仿真:综合后仿真:布局布线后仿真:

* 74HC32 表 5:输入输出状态、逻辑状态

* Verilog 代码:module HC32( A,B,Y ); input A,B; output Y; assign Y=A&B; endmodule

* 测试平台代码:`timescale 1ns/100ps module testbench; reg A,B; wire Y; HC32 u1(A,B,Y); initial begin ... end endmodule

* RTL view:technology view:综合前仿真:综合后仿真:布局布线后仿真:

本实验报告对数字逻辑基础设计仿真及验证的基本概念和方法进行了详细的介绍和实践,旨在增强学生对EDA设计的理解和掌握能力。