testbench的写法

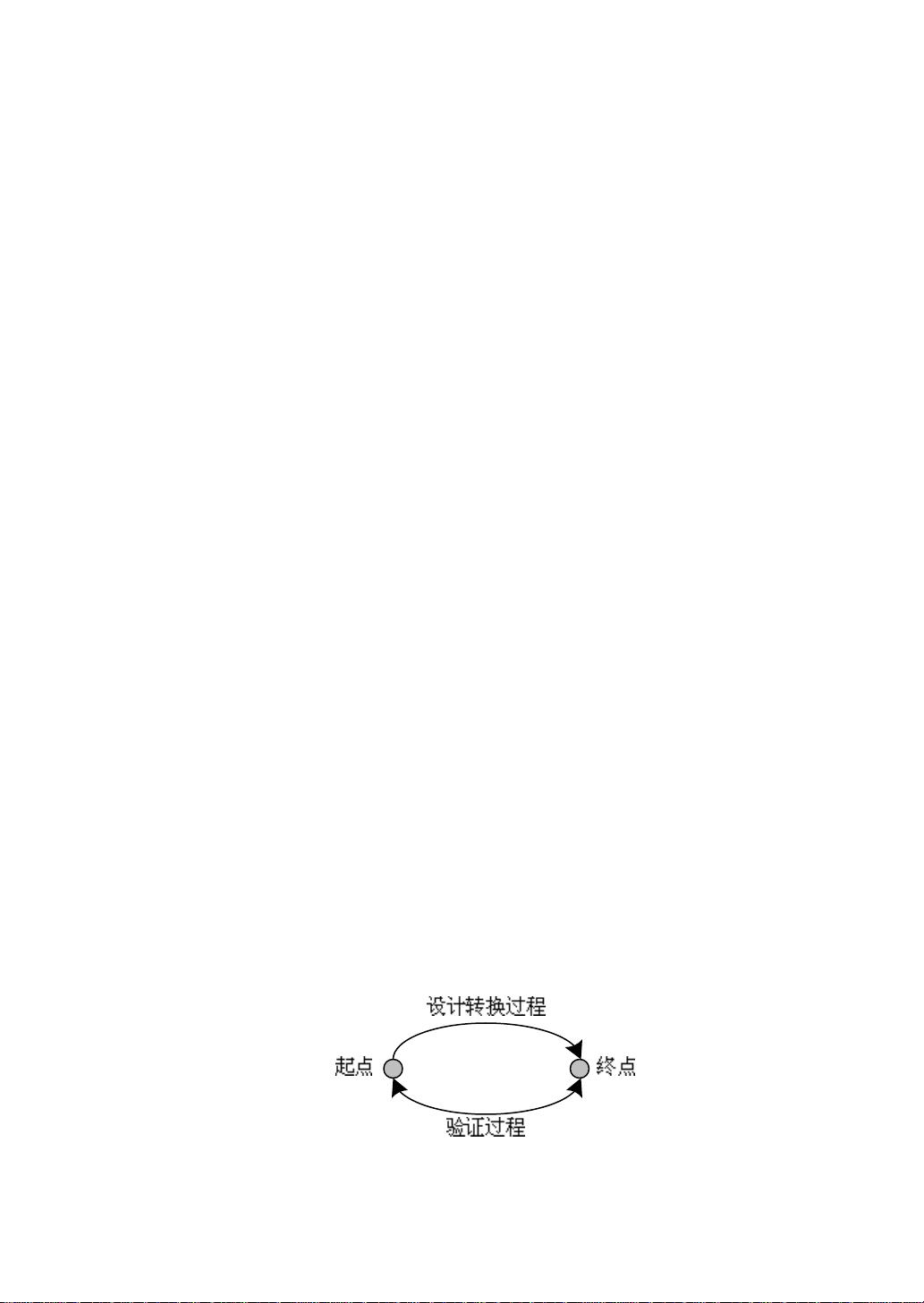

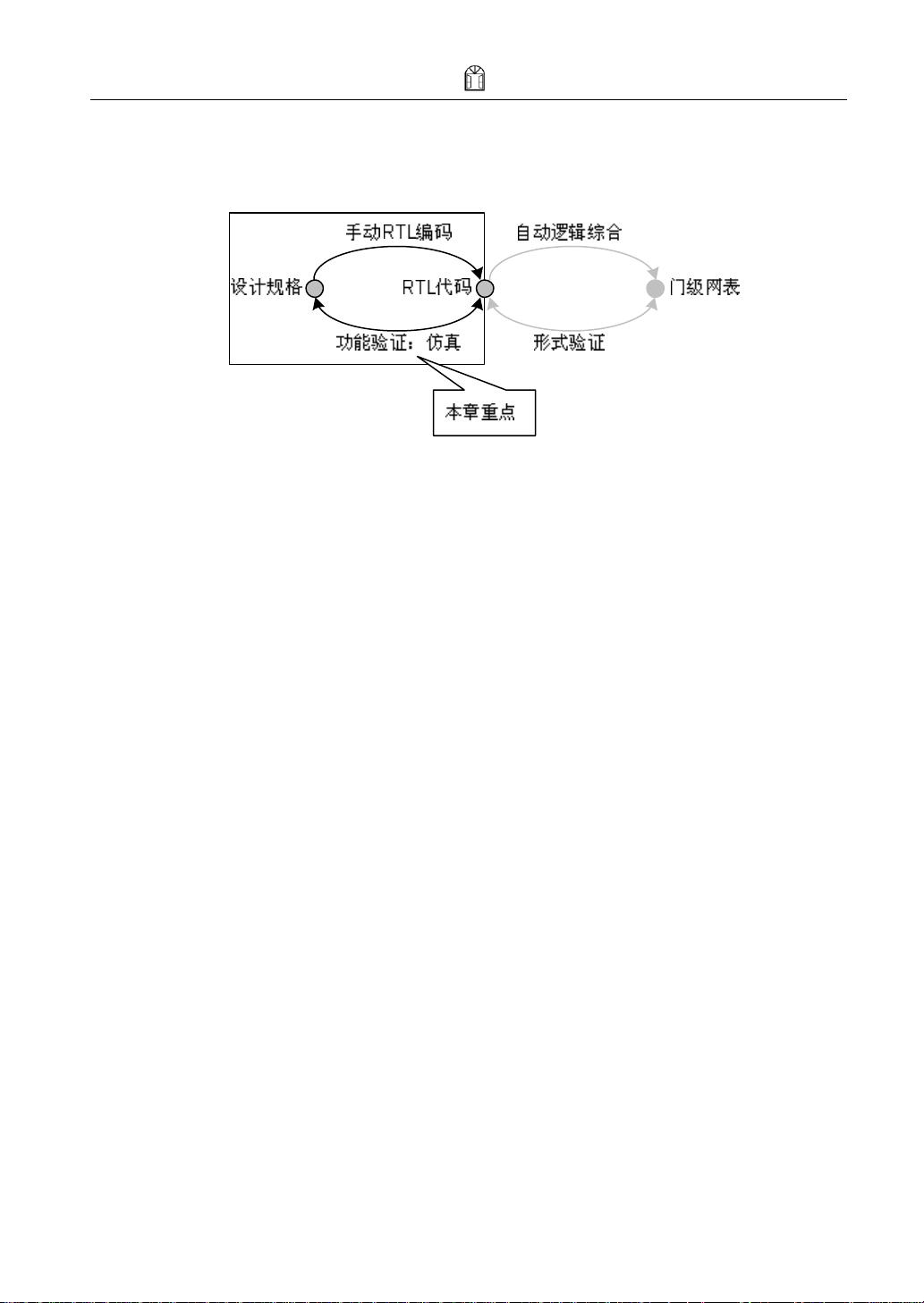

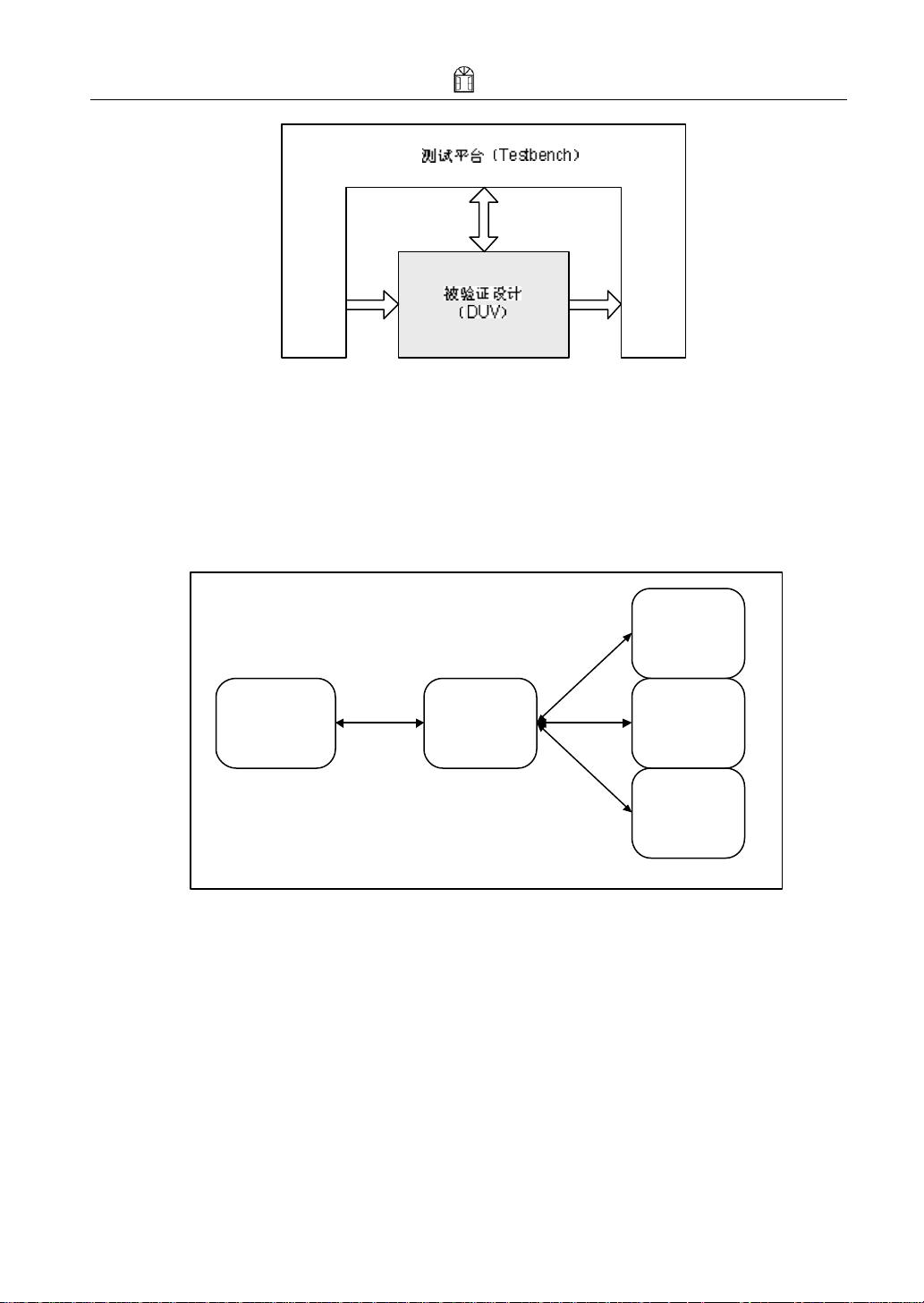

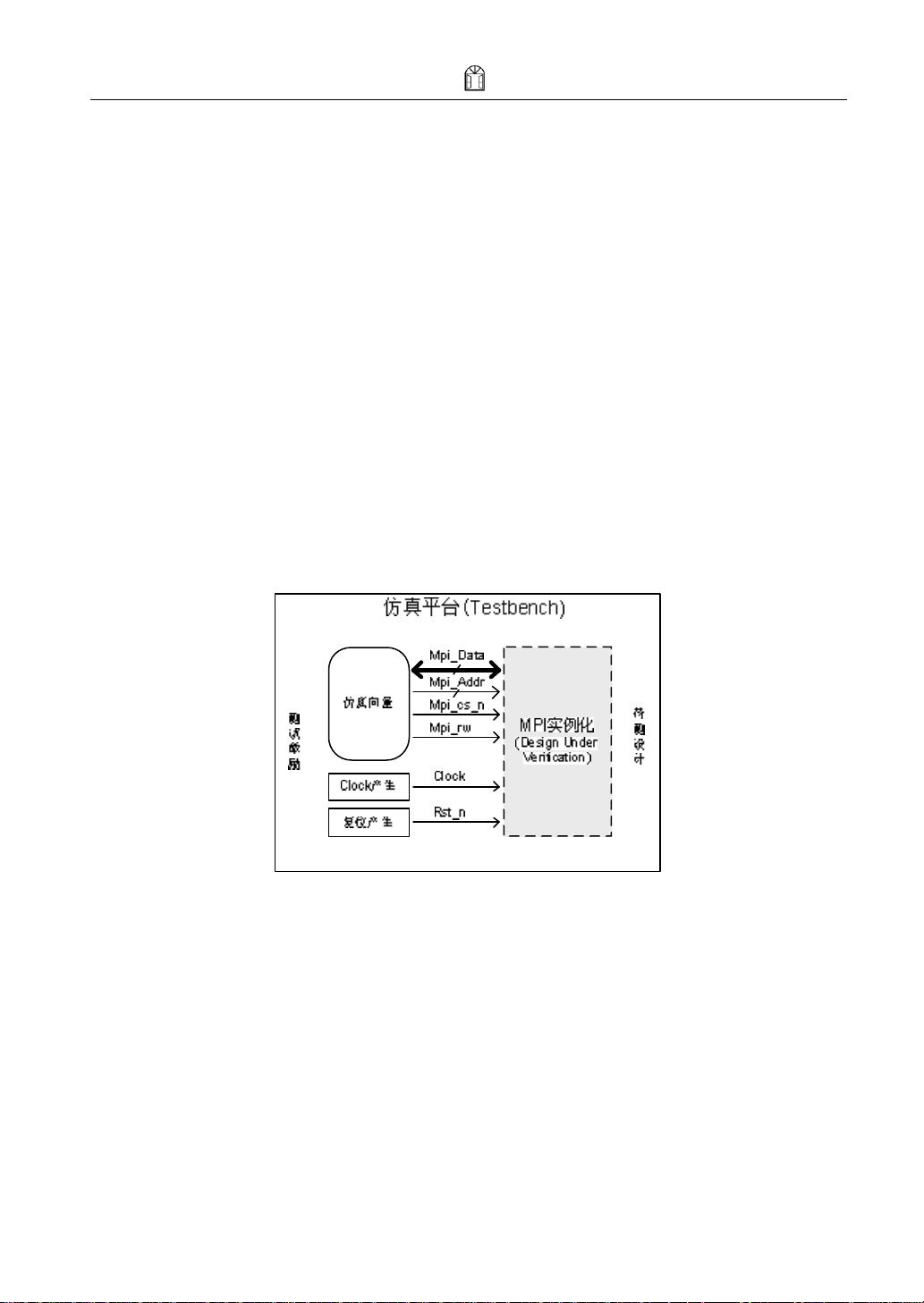

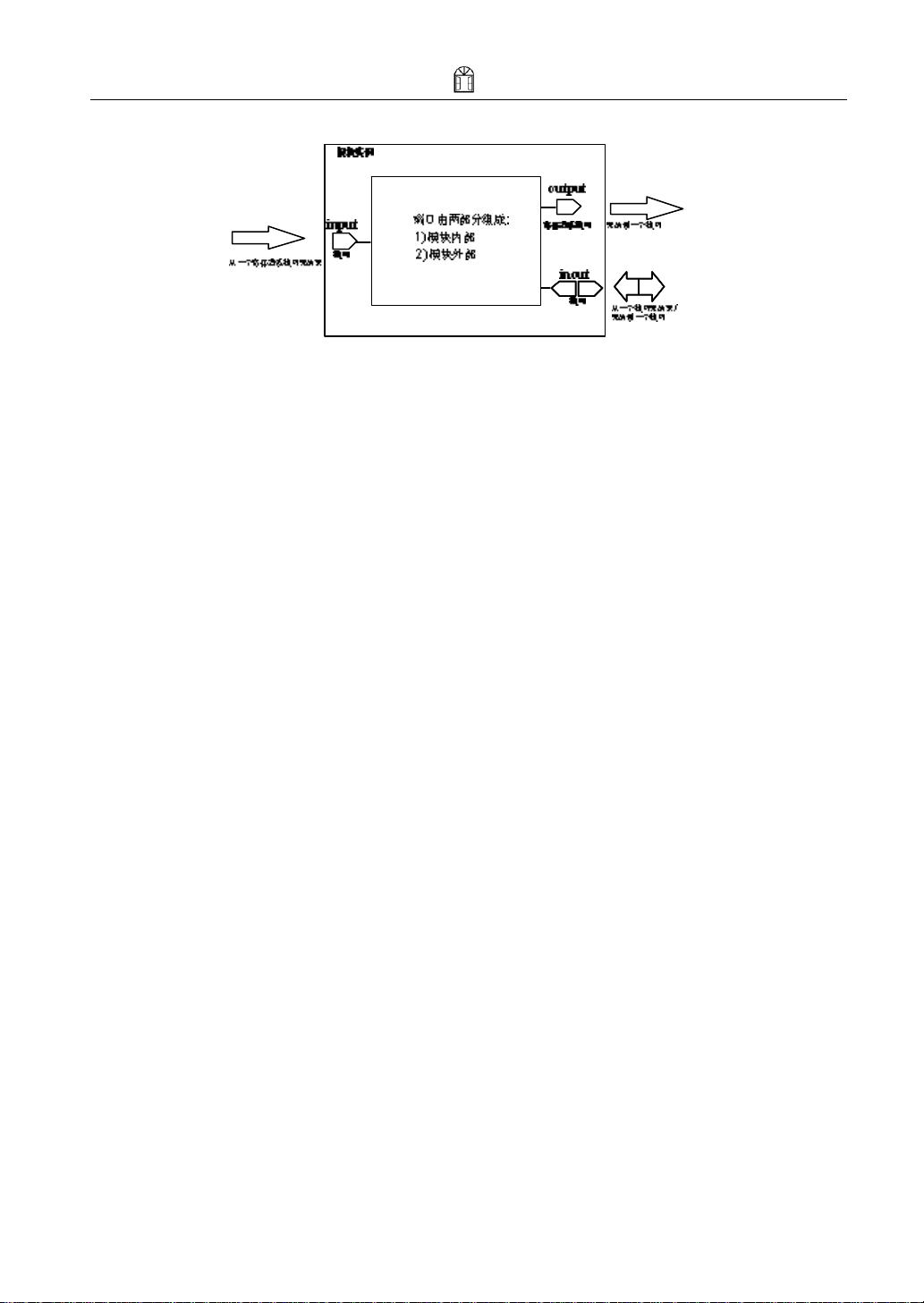

### Testbench的写法及其在逻辑验证中的应用 #### 一、引言 在现代电子设计自动化(EDA)领域,特别是在集成电路(IC)设计中,验证是确保设计正确性的关键步骤之一。验证不仅是为了发现设计错误,更重要的是为了保证设计在功能上能够满足规格要求。在这一过程中,Testbench扮演着至关重要的角色。本文将深入探讨Testbench的编写方法及其在逻辑验证中的应用。 #### 二、Testbench的概念与重要性 **Testbench**是一种用于验证电路设计正确性的软件环境。它通过提供一系列输入激励给待验证设计(Design Under Verification, DUV),并观察其输出响应,以此来判断设计是否符合预期的行为。在集成电路设计的各个环节,例如RTL级设计验证、门级验证以及系统级验证等,Testbench都是必不可少的一部分。 #### 三、仿真与验证的基本概念 **仿真**是指使用EDA工具模拟电路设计的工作状态,以验证其功能正确性。根据不同的验证目标和层次,仿真可以分为多种类型,如行为仿真、功能仿真、时序仿真等。而**验证**的目标是确保设计在功能上完全符合规格书的要求,这是一个持续的过程,贯穿于整个设计周期之中。 #### 四、基于Testbench的仿真流程 基于Testbench的仿真流程通常包括以下几个步骤: 1. **编写Testbench**: 这是仿真流程的第一步,也是最重要的一步。在Testbench中,需要定义各种测试场景和激励序列,以便全面地覆盖设计的功能点。 2. **编译与链接**: 将Testbench和待验证设计一起编译,并链接成一个可执行的仿真模型。 3. **运行仿真**: 执行仿真模型,根据预设的激励序列运行仿真,获取输出结果。 4. **结果分析与调试**: 分析仿真结果,如果发现问题,则需要返回到设计阶段进行修改。如果一切正常,则表明设计通过了当前阶段的验证。 #### 五、Testbench的编写要点 1. **激励信号的设计**: Testbench需要为待验证设计提供一系列激励信号。这些信号应该能够覆盖所有可能的输入组合,确保设计的所有功能点都得到了验证。 2. **DUT的实例化**: 在Testbench中正确地实例化待验证设计(DUT)至关重要。这通常涉及到设置正确的端口映射,以确保激励信号能够正确地传递给DUT。 3. **输出结果的处理**: Testbench需要收集DUT的输出结果,并对其进行处理。这可能包括将结果记录到文件中、显示在波形窗口或通过自动比较工具与预期结果进行对比。 4. **自动比较工具的应用**: 对于复杂的测试场景,手动分析仿真结果可能非常耗时且容易出错。因此,引入自动比较工具来检查仿真结果与预期结果的一致性是非常必要的。 #### 六、实例:结构化Testbench的编写 结构化Testbench是一种组织良好的Testbench编写方式,它将Testbench分解成多个模块,每个模块负责特定的功能。例如,可以将Testbench分为以下几个部分: 1. **测试控制模块**: 负责启动和停止测试,管理测试流程。 2. **激励生成模块**: 生成各种测试激励信号。 3. **数据采集模块**: 收集DUT的输出数据。 4. **结果比较模块**: 比较DUT的输出结果与预期结果。 5. **日志记录模块**: 记录测试过程中的关键信息。 #### 七、结论 Testbench是逻辑验证的核心组成部分,对于确保集成电路设计的正确性和可靠性具有重要意义。通过合理设计Testbench,不仅可以提高验证效率,还能有效减少设计错误。因此,对于FPGA学习者来说,掌握Testbench的编写技巧是非常必要的。在未来的设计工作中,随着设计复杂度的不断提高,更加高效、灵活的验证方法和技术将会得到广泛应用。

剩余39页未读,继续阅读

pennel20082013-01-10内容少,已经会的人看看复习还可以,不适合初学

pennel20082013-01-10内容少,已经会的人看看复习还可以,不适合初学 lgddd2012-04-27挺不错的 适合初学者 节选自《Verilog设计与验证》 作者:吴继华、王诚

lgddd2012-04-27挺不错的 适合初学者 节选自《Verilog设计与验证》 作者:吴继华、王诚

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功