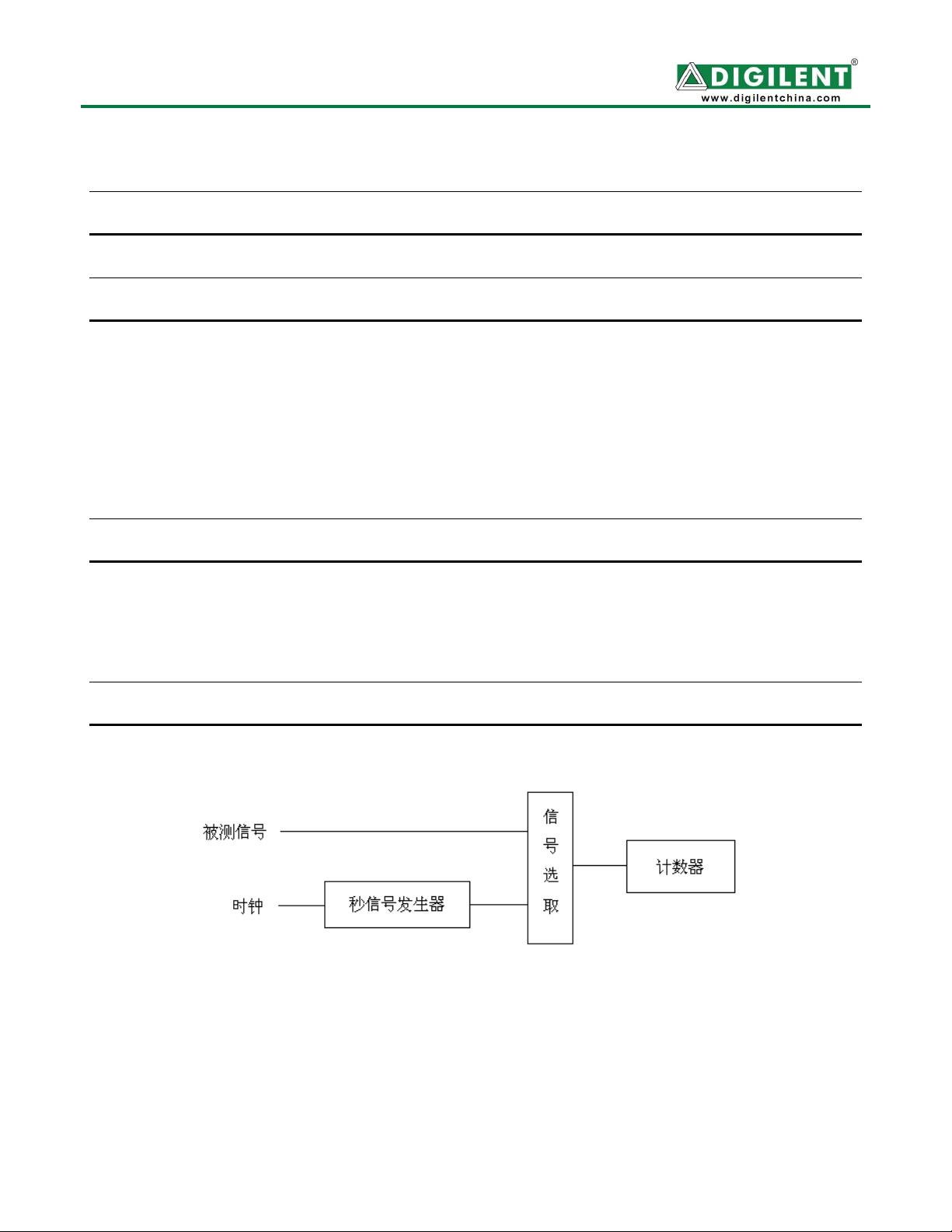

"数字系统实践 秒信号发生器" 数字系统实践是指利用现代数字技术和编程语言来设计和实现各种数字系统的实践活动。在本实验中,我们将使用Verilog语言编写程序,在FPGA上实现面信号发生器。 知识点1:秒信号发生器的结构 秒信号发生器是能够直观显示单位时间内被测信号周期数的设备。其结构主要包括频率计、计数器和后续电路三部分。频率计用于选取1秒内的被测信号信号,提供给计数器,计数器将计数结果传送给后续电路进行处理和显示。 知识点2:Verilog HDL语言 Verilog HDL是用于数字电路设计的硬件描述语言。它可以用来描述数字电路的行为和结构。在本实验中,我们将使用Verilog HDL语言编写秒信号发生器的代码,并使用ISE软件进行综合和仿真。 知识点3:ISE软件的使用 ISE软件是Xilinx公司开发的一款集成开发环境,用于设计和实现数字系统。它提供了一个统一的开发平台,支持从设计到实现的整个开发过程。在本实验中,我们将使用ISE软件来设计和实现秒信号发生器。 知识点4:触发器和计数器的设计要素 触发器和计数器是数字系统中的基本组件。触发器用于存储和输出信号,而计数器用于计数和统计信号的周期数。在本实验中,我们将设计和实现一个触发器和计数器,以实现秒信号发生器的功能。 知识点5:频率计的设计 频率计是秒信号发生器的关键组件。它用于选取1秒内的被测信号信号,提供给计数器,计数器将计数结果传送给后续电路进行处理和显示。在本实验中,我们将设计和实现一个频率计,以实现秒信号发生器的功能。 知识点6:分频技术 分频技术是数字系统中的一种常用技术。它用于将高频信号降频到低频信号,以便于后续处理和显示。在本实验中,我们将使用分频技术来产生秒信号。 知识点7:DCM的使用 DCM(Digital Clock Manager)是Xilinx FPGA中的一个组件,用于产生高频数字时钟信号。在本实验中,我们将使用DCM来产生高频时钟信号,然后使用分频技术来产生秒信号。 知识点8:Testbench的写法 Testbench是ISE软件中的一个组件,用于测试和验证数字系统的正确性。在本实验中,我们将编写Testbench代码,以便于测试和验证秒信号发生器的正确性。 本实验旨在指导学生通过使用ISE软件进行频率计秒信号发生器的设计和仿真,掌握数字系统中触发器和计数器的设计要素,熟悉Verilog HDL语言,并初步掌握ISE软件的用法。

剩余6页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- (源码)基于gRPC和Zookeeper的GirafKV分布式键值存储系统.zip

- javaEE企业级B2C商城源码带文档数据库 MySQL源码类型 WebForm

- (源码)基于Spark2.x和Flume的实时新闻分析系统.zip

- (源码)基于C#的礼服管控系统.zip

- R语言数据去重与匹配:20种常用函数详解及实战示例

- (源码)基于SpringCloudAlibaba的系统管理平台.zip

- java企业级维修订单系统源码数据库 MySQL源码类型 WebForm

- (源码)基于ESP32S2和腾讯云的物联网设备管理系统.zip

- DENON天龙回音壁功放DHT-S514维修手册dpf

- (源码)基于Arduino和Firebase的物联网称重监测系统.zip

信息提交成功

信息提交成功