一个简单16位CPU的设计

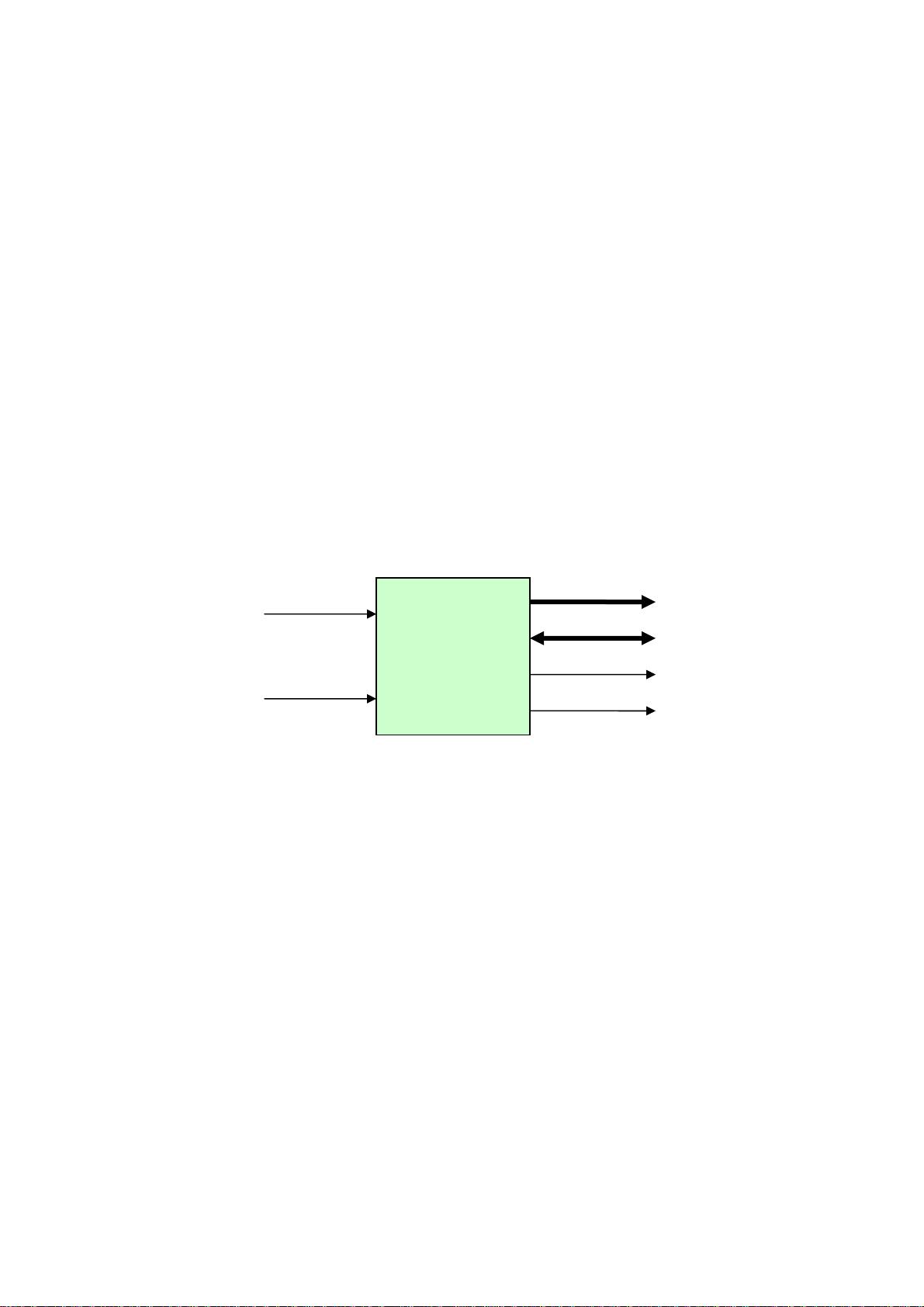

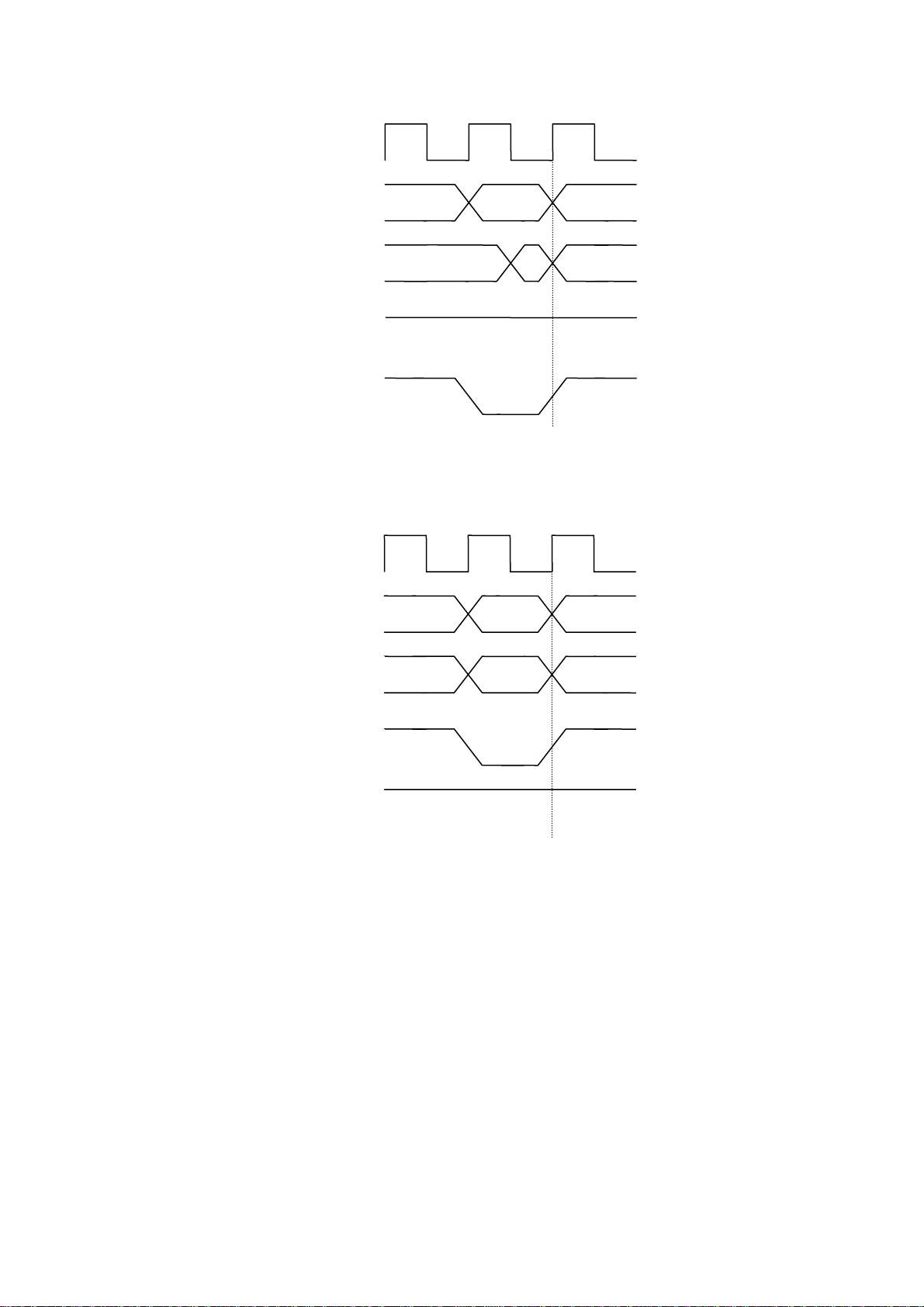

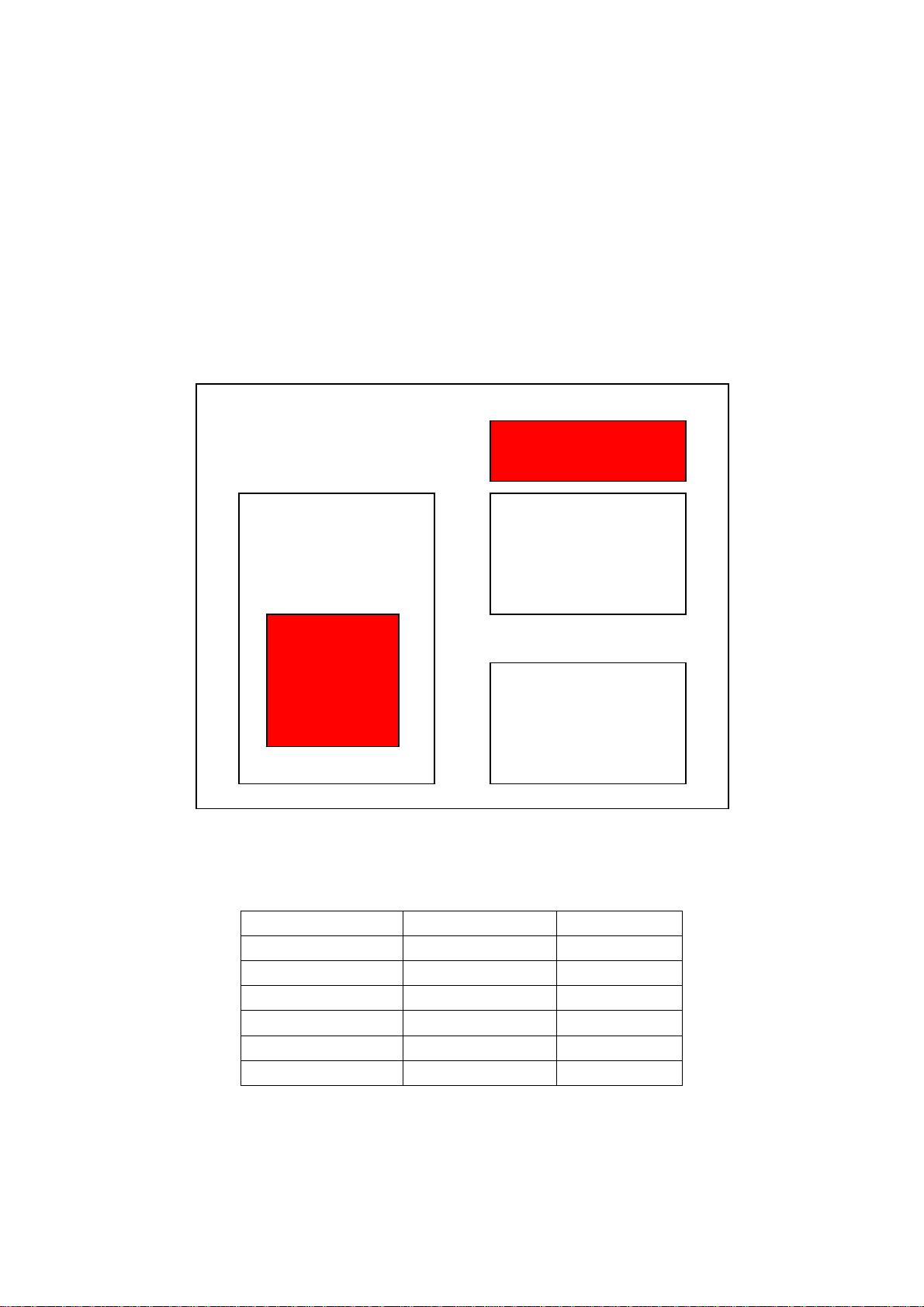

### 一个简单16位CPU的设计 #### 项目概述与目标 该项目旨在设计一款极其简易的16位CPU,基于冯·诺依曼架构,并命名为ERVS16-CPU(EasyRight Very Simple 16-bit CPU)。ERVS16拥有自己独立的指令集,并计划在项目尾声阶段使用该指令集编写一个简单的操作系统来测试ERVS16的性能。 项目重点在于研究和实现CPU、寄存器、内存和指令集之间的交互作用。具体而言,涉及以下方面: 1. **读/写寄存器** 2. **读/写内存** 3. **执行指令集中的所有指令** #### ERVS16的硬件设计 **图1.1** 显示了ERVS16的抽象模型,其中包含了CPU、内存读写控制信号等关键组件。为了确保设计的一致性和可靠性,项目采用了正缘触发时钟频率(Positive Edge Triggered Clocking)技术,即系统时钟频率为1MHz。 - **复位信号**: 首先输入高电平以初始化CPU,随后在复位信号变为低电平时启动位于内存地址0处的指令。 - **内存读写循环**: 在内存读写操作过程中,需确保读/写信号处于低电平状态,以避免冲突。每次内存读写操作都需要一个完整的信号周期才能完成。 - **时钟技术**: 定义了信号可以被读写的时间窗口。边缘触发时钟频率技术被用于防止同时进行读写操作,确保数据的完整性。 #### 测试环境与平台 项目采用Xilinx开发板进行设计验证。该开发板包含以下组件: - **I/O设备**: 包括一系列开关和7段显示屏。 - **RAM**: 1k x 16位。 - **ROM**: 1k x 16位,用于存储测试程序。 - **测试文件**: 测试程序将从一个特定的测试文件中加载,文件内容由地址和对应的二进制值组成。 - **系统**: 包括内存和I/O设备的接口。 **图1.4** 描述了开发板的主要组成部分及其实现需求。 #### 设备技术细节 | 设备 | 地址范围 | 访问模式 | |------|-----------------|------------| | ROM | 0x0000–0x03FF | 只读 | | RAM | 0x0400–0x07FF | 读写 | | 开关 | 0x8000 | 只读 | | 7段显示屏 | 0x8001–0x8002 | 读写 | | 第一个串口 | 0xC000–0xC001 | 读写 | | 第二个串口 | 0xC002–0xC003 | 读写 | #### 项目计划与时间表 该项目预计耗时四个月(从2003年7月27日至2003年11月27日),具体时间安排如下: - **2003年7月27日 - 8月2日** - 确定支持的指令集及其格式。 - 绘制CPU寄存器级元件图,包括程序计数器、指令内存、数据内存、寄存器、算术逻辑单元(ALU)等,并规划它们之间的连接方式。 - 使用有限状态机(FSM)来列出所有可能的信号和状态组合。 - **2003年8月3日 - 8月9日** - Multi...(此处文档片段中断) ### 总结 该项目通过设计并实现一个基于冯·诺依曼架构的简单16位CPU,不仅深入探讨了CPU内部工作原理,还为参与者提供了宝贵的实践经验。从硬件设计到软件开发,项目覆盖了完整的CPU开发流程,对于培养计算机科学领域的专业技能具有重要意义。

剩余28页未读,继续阅读

wangyun_12162012-09-01很不错的资料,可以通过他了解CPU的架构

wangyun_12162012-09-01很不错的资料,可以通过他了解CPU的架构 kingsloveqzy2012-10-17材料太少了,是基本的设计计划,还是个类mips的core

kingsloveqzy2012-10-17材料太少了,是基本的设计计划,还是个类mips的core

- 粉丝: 1

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Oracle10gDBA学习手册中文PDF清晰版最新版本

- 扒网站数据软件项目全套技术资料100%好用.zip

- AI爬虫项目全套技术资料100%好用.zip

- 倪海厦讲义及笔记,易学数据测算

- 智能图书管理系统项目全套技术资料.zip

- 基于java写的爬虫项目全套技术资料.zip

- 218) Leverage - 创意机构与作品集 WordPress 主题 2.2.7.zip

- 220) Vinkmag - 多概念创意报纸新闻杂志 WordPress v5.0.zip

- 219) Axtra - 数字机构创意作品集主题 v2.0.zip

- 217) Voice - 清洁新闻 - 杂志 WordPress 主题 v3.0.3.zip

- 215) Classiera – 分类广告 WordPress 主题 v4.0.28.zip

- 216) Creote - 企业与咨询业务 WordPress 主题 v2.7.8.zip

- 212) Outgrid - 多用途 Elementor WordPress 主题 v2.0.0.zip

- 213) Blacksilver - 摄影 WordPress 主题 v9.4.zip

- 214) Nokri - 招聘板 WordPress 主题 v1.5.9.zip

- 211) TopDeal - 多供应商市场 WordPress 主题(移动布局就绪) v2.3.15.zip

信息提交成功

信息提交成功