设计一个非常简单的 16 位 CPU

I hear and I forget. I see and I remember. I do and I understand.

--

孔子

EasyRight 计算机研究小组

http://www.EasyRight.net August 2003

1

第一章 简介

1.目的

本项目的目的是设计一个十分简单的基于冯·诺依曼架构的 16 位 CPU。我们将这

颗 CPU 命名为 ERVS16-CPU( EasyRight Very Simple 16-bit CPU )。 ERVS16

有它自己的指令集。并且,为了测试 ERVS16,我们将在项目的最后用它的指令

集编写一个十分简单的操作系统。简单的说,我们在这个项目中只考虑 CPU,

寄存器,内存和指令集之间的关系。这就是说我们只需要实现:

(1)读/写寄存器

(2)读/写内存

(3)执行指令集中的所有指令

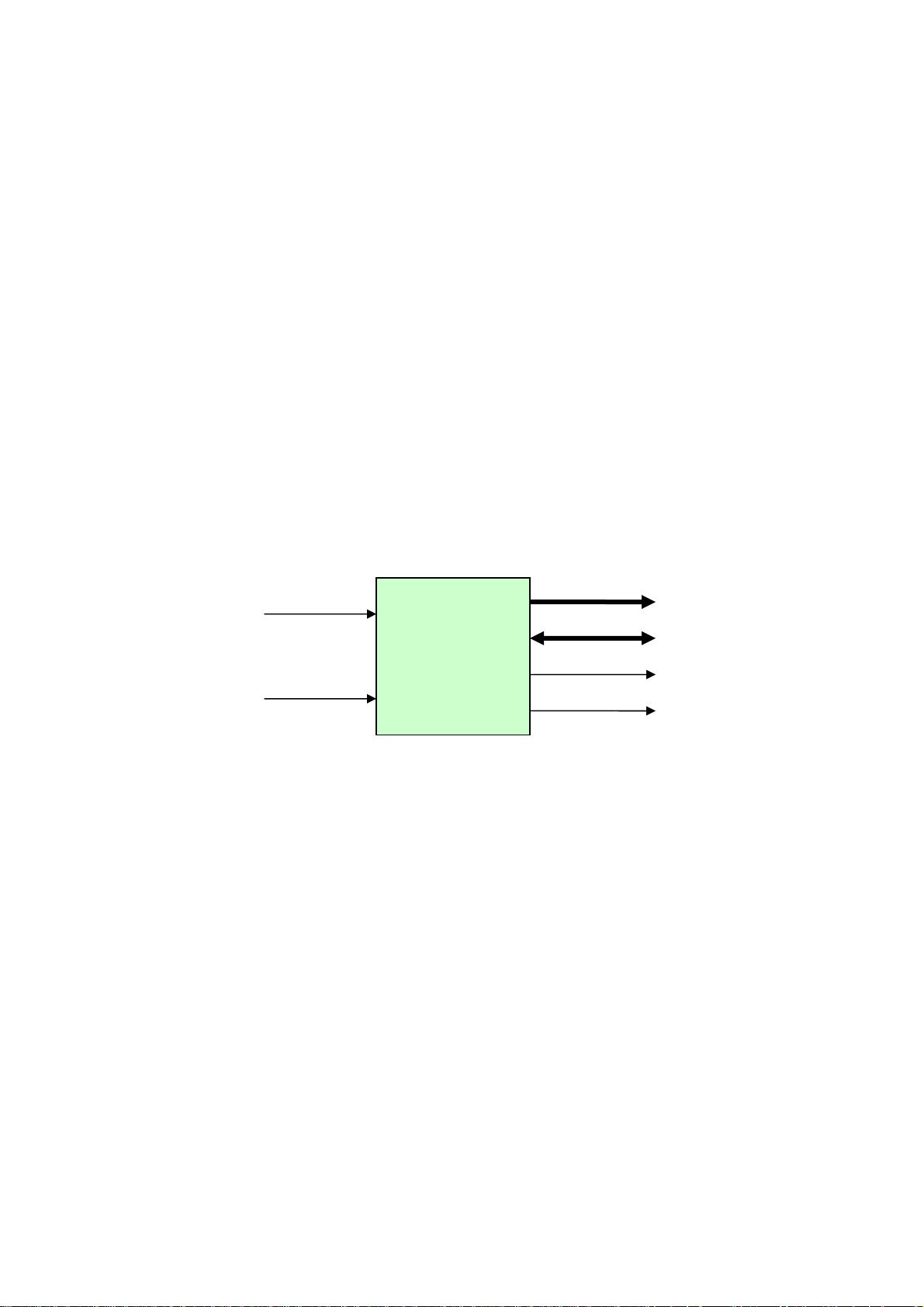

图 1.1 是 ERVS16 的抽象图

图 1.1 ERVS16 抽象图

假设系统时钟频率是 1MHz,我们将在设计中使用正缘触发时钟频率(Positive

Edge Triggered Clocking)技术。复位信号首先输入一个高电平初始化 CPU ,接

着当复位信号变为低电平时开始运行位于 0 地址的指令。

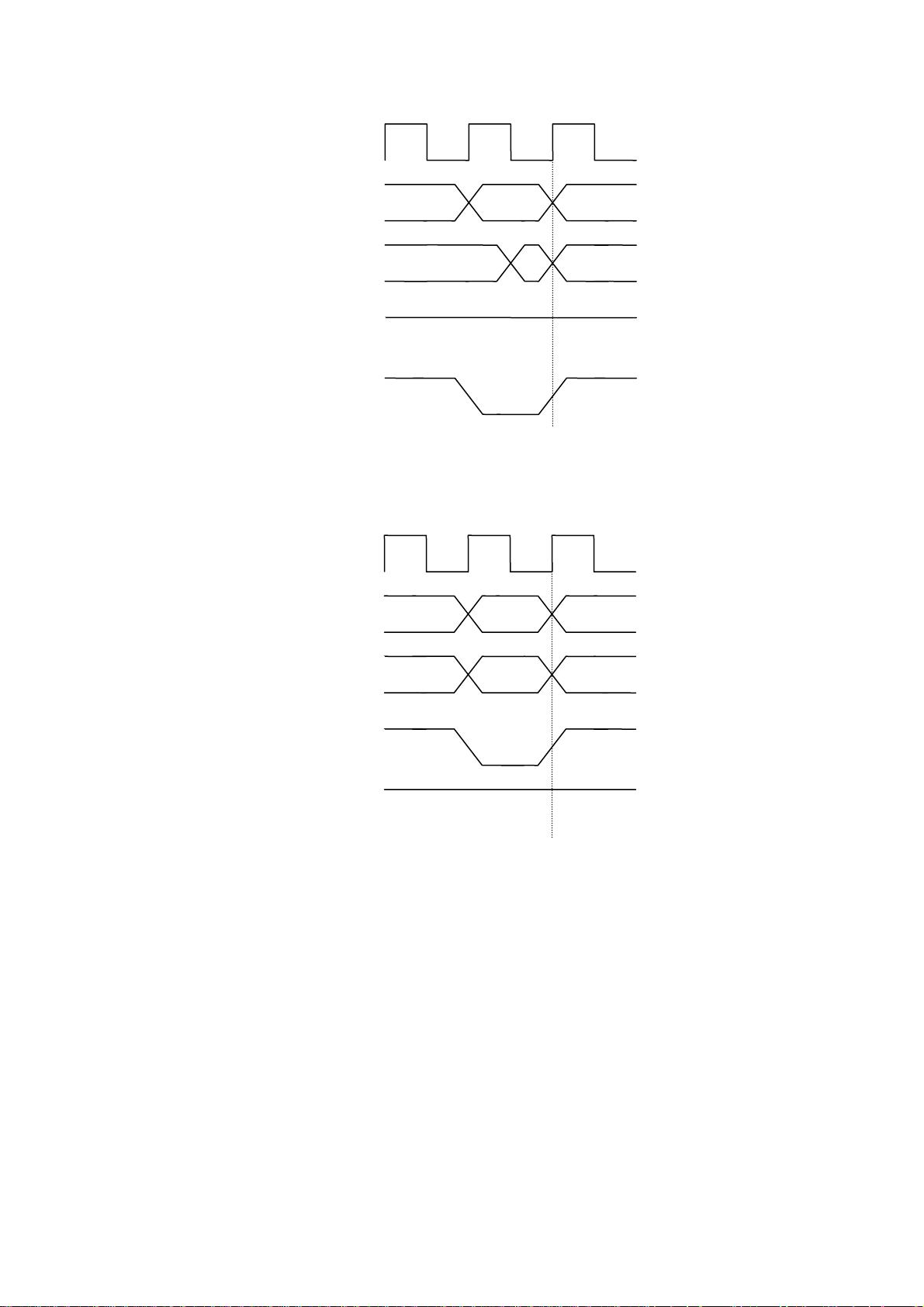

内存读/写循环时,要确保可读/可写信号是在低电平。如图 1.2 和 1.3,所有内存

读写操作都需要一个信号周期来完成。

时钟技术(Clocking Methodology)定义了信号可以被读写的时间。读写操作不

能同时进行。边缘触发时钟频率技术(Edge-triggered Clocking Methodology)正

是被用来防止这样的情况发生。边缘触发时钟频率技术是指机器存储的所有值都

只能在时钟边缘被更新。

Read_enable

write_enable

Data

Address

reset

ERVS16CPU

clk

2

图 1.2 内存读取循环时间图

图 1.3 内存写入循环时间图

2.测试环境

我们使用 XILINX development board 来测试对 ERVS16 的设计。XILINX

development board 包括如下部件:

一系列 I/O 设备(包括一系列开关(Switch)和 7 Segment Displays

RAM: 1k x 16

ROM: 1k x 16:它被用于存储测试程序。在模拟开始的时候,ROM 镜像从一

Data written into

memory here

clock

address

Data (to memory)

write_enable

read_enable

Data read into CPU

Register here

clock

address

Data (from memory)

write_enable

read_enable

3

个测试文件(Test File)中加载。这个文件的每一行都包括由空格隔开的两

个值:一个十进制的地址和一个二进制的值。比如:

1 1010100010101010

2 0101011001100110

4 0101011110101000

7 0010101011010101

5 0111000101010000

系统:包括内存和 I/O 设备的界面

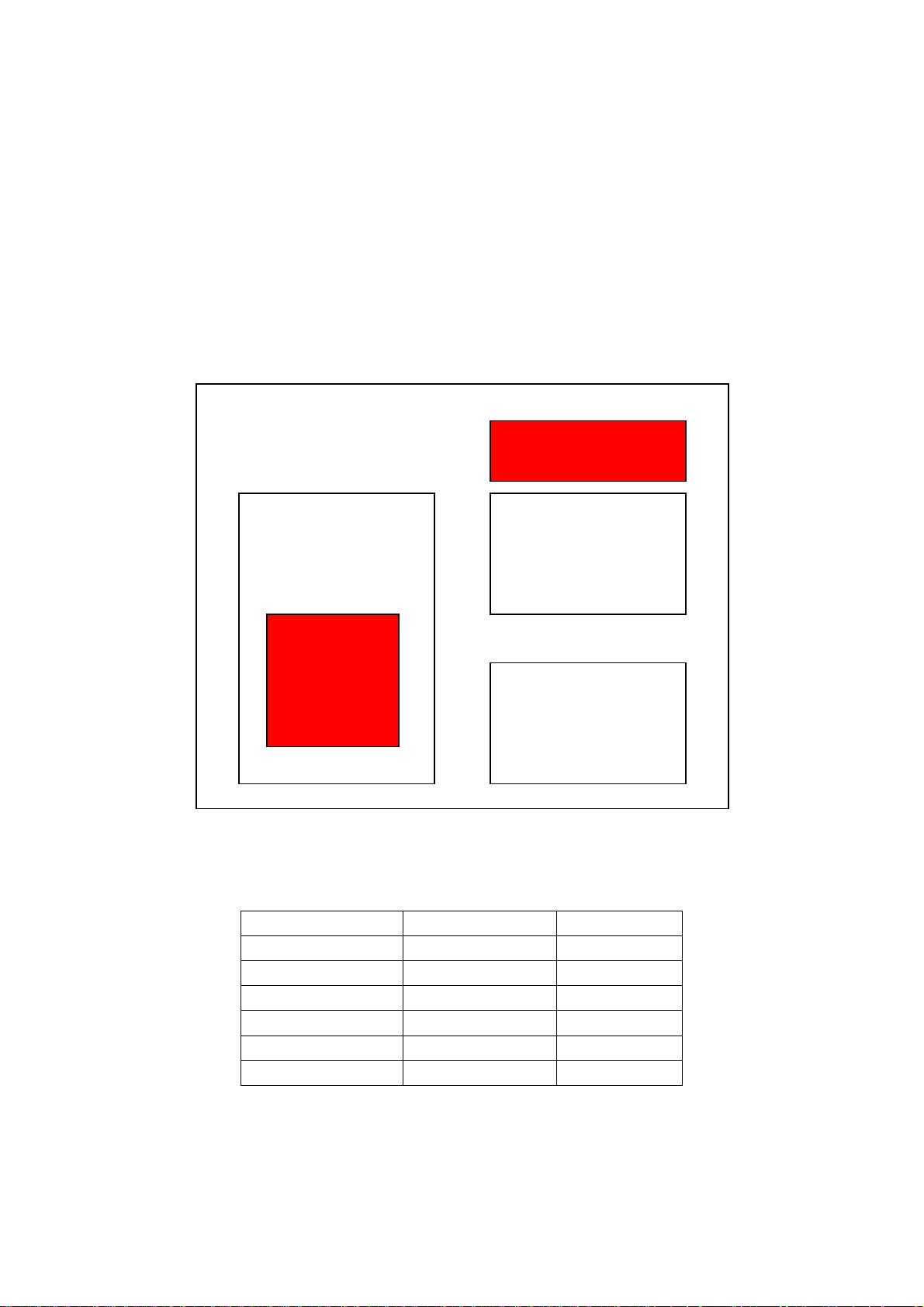

图 1.4 显示了 development board 的主要组成部分。我们只需要实现红色的部分

图 1.4 设计结构

下表显示了 development board 上所有设备的技术细节。

设备 地址范围 访问模式

ROM (1KW) 0x0000 – 0x03FF read only

RAM (1KW) 0x0400 – 0x07FF read and write

开关 0x8000 read only

7 Segment Displays 0x8001 – 0x8002 read and write

第一个串口 0xC000 – 0xC001 read and write

第二个串口 0xC002 – 0xC003 read and write

System RAM

ROM

System Clock &

other inputs

Testbench

CPU

4

2. 计划

整个计划将在四个月内完成(从 2003 年 7 月 27 日到 2003 年 11 月 27 日)。在 项

目完成之后,我们将会有设计真正 CPU 的经验。这样的经验在我们今后设计复

杂的 CPU 时会有帮助。下面是时间表:

27/7/2003 – 2/8/2003

(1) 确定支持的指令集及其格式

(2) CPU 的寄存器级元件图,包括程序计数器(Program counter),存储指令的内

存(Instruction memory),存储数据的内存(Data memory),寄存器(Registers),

算术和逻辑单元(ALU),以及如何连接它们;

(3) 用有限状态机(Finite State Machine,FSM)列出所有信号和状态的组合

3/8/2003 – 9/8/2003

(1) Multicycle diagram;

(2) ALU 支持所有指令集

10/8/2003 – 16/8/2003

(1) 用 VHDL 实现图 4.1 的大多数部分