没有合适的资源?快使用搜索试试~ 我知道了~

嵌入式运算器实验报告参考模板.pdf

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 123 浏览量

2022-07-14

06:37:27

上传

评论

收藏 425KB PDF 举报

温馨提示

嵌入式运算器实验报告是学习和理解嵌入式系统中运算器工作原理的重要实践环节。这个实验主要目的是深入理解简单运算器的数据传输路径,验证运算功能发生器的组合功能,以及掌握算术逻辑运算的基本操作,包括加、减、与等。实验中使用的设备是一个基于74LS181功能的8位ALU(算术逻辑单元),通过VHDL硬件描述语言编程实现。 在实验中,首先要理解ALU的数据通路,它由8位输入A和B,4位模式选择S,以及控制信号M和进位位CN组成。ALU的功能由S的16种不同组合决定,由4位2进制计数器LPM_COUNTER产生的时钟Sclk驱动。M信号用于选择算术运算(M=0)或逻辑运算(M=1),CN则指示运算是否有低位进位。 实验步骤包括在Quartus II环境下设计ALU元件,编写ALU181.VHD文件,并将其转化为可调用的原理图元件。接着,通过图形方式建立顶层文件,将所需元件从基本元件库中调入并连线,确保输入输出引脚正确设置。实验者需要按照表格2-1输入数据A和B,设置模式S、M和Cy,以验证ALU的算术和逻辑运算功能。 实验任务要求通过数据选择开关设置A和B的值,例如将55H和AAH分别置入A和B寄存器。通过改变模式S和进位位CN,观察ALU执行不同运算的结果。例如,设置S为9代表加法操作,当CN为0时,执行55H+AAH,结果显示为0FFH;当CN为1时,执行带进位的加法,结果为100H。 整个实验过程旨在强化理论知识与实践操作的结合,帮助学生熟悉嵌入式运算器的内部运作机制,增强硬件描述语言的编程能力,并能实际操作和验证ALU的各种运算功能。这对于未来在嵌入式系统设计和开发中的应用具有重要意义。

资源推荐

资源详情

资源评论

嵌入式运算器实验报告

实验二 运算器组成实验

1.算术逻辑运算实验

一.实验目的

1. 了解简单运算器的数据传输通路。

2. 验证运算功能发生器的组合功能。

3. 掌握算术逻辑运算加、减、与的工作原理。

4. 验证实验台运算的 8 位加、减、与、直通功能。

5. 按给定数据,完成几种指定的算术和逻辑运算。

二.实验内容

1.实验原理

算术逻辑单元 ALU 的数据通路如图 2-1 所示。其中运算器 ALU181 根据 74LS181 的功

能用 VHDL 硬件描述语言编辑而成,构成 8 位字长的 ALU。参加运算的两个 8 位数据分别

为 A[7..0]和 B[7..0],运算模式由 S[3..0]的 16 种组合决定,而 S[3..0]的值由 4 位 2 进制计数

器 LPM_COUNTER 产生,计数时钟是Sclk(图 2-1);此外,设M=0,选择算术运算,M=1

为逻辑运算,C

N

为低位的进位位;F[7..0]为输出结果,C

O

为运算后的输出进位位。两个 8

位数据由总线 IN[7..0]分别通过两个电平锁存器 74373 锁入,ALU 功能如表 2-1 所示。

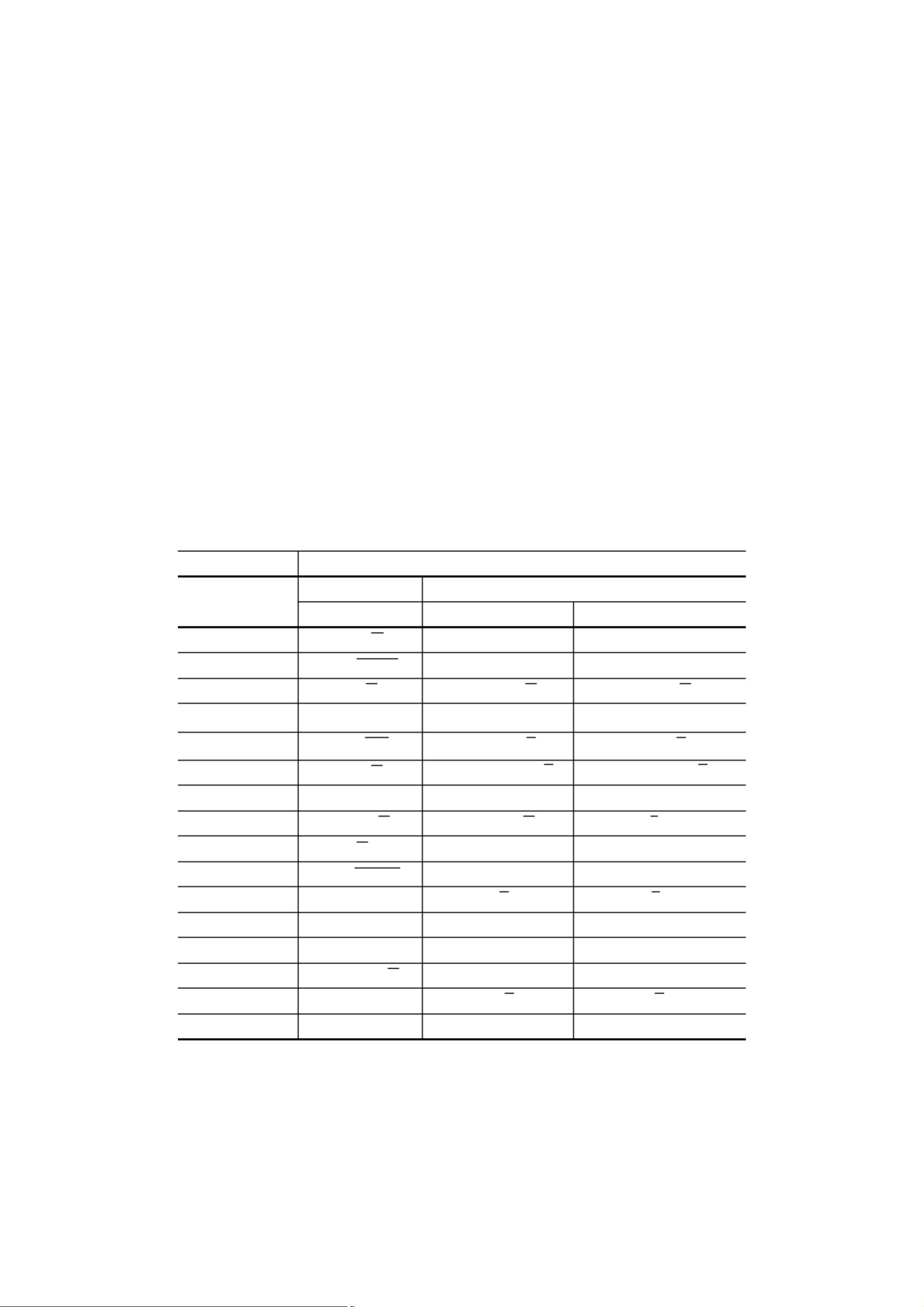

表 2-1

选择端

S3 S2 S1 S0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

M=H

逻辑功能

ALU181 的运算功能

高电平作用数据

M=L 算术操作

Cn=L(无进位) Cn=H(有进位)

F A

F A B

F A

F A B

F A加1

F ( A B)

加 1

F A B

F 0

F AB

F A B

F

减 1(2 的补码)

F A加AB

F A B

+1

F 0

F A加AB

加 1

F B

F A B

F AB

F A B

F A B

F ( A B)

加

AB

F A减B

F ( A B)

加

AB

+1

F A减B减1

F ( A B )减1

F A B

F A加AB

F A加B

F (A B )加AB

F A加AB

加 1

F A加B

加 1

F ( A B)加AB

加 1

F B

F AB

F 1

F AB

F A加A

*

F (A B)加A

F (A B )加A

F AB减1

F A加A加1

F (A B)加A

加 1

F (A B )加A

加 1

F A B

F A B

F A

F A

F A减1

注 1、* 表示每一位都移至下一更高有效位, “+”是逻辑或,“加”是算术加

注 2、在借位减法表达上,表 2-1 与标准的 74181 的真值表略有不同。

1 / 8

资源评论

a66889999

- 粉丝: 40

- 资源: 1万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功