sdram_ov5640_hdmi显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

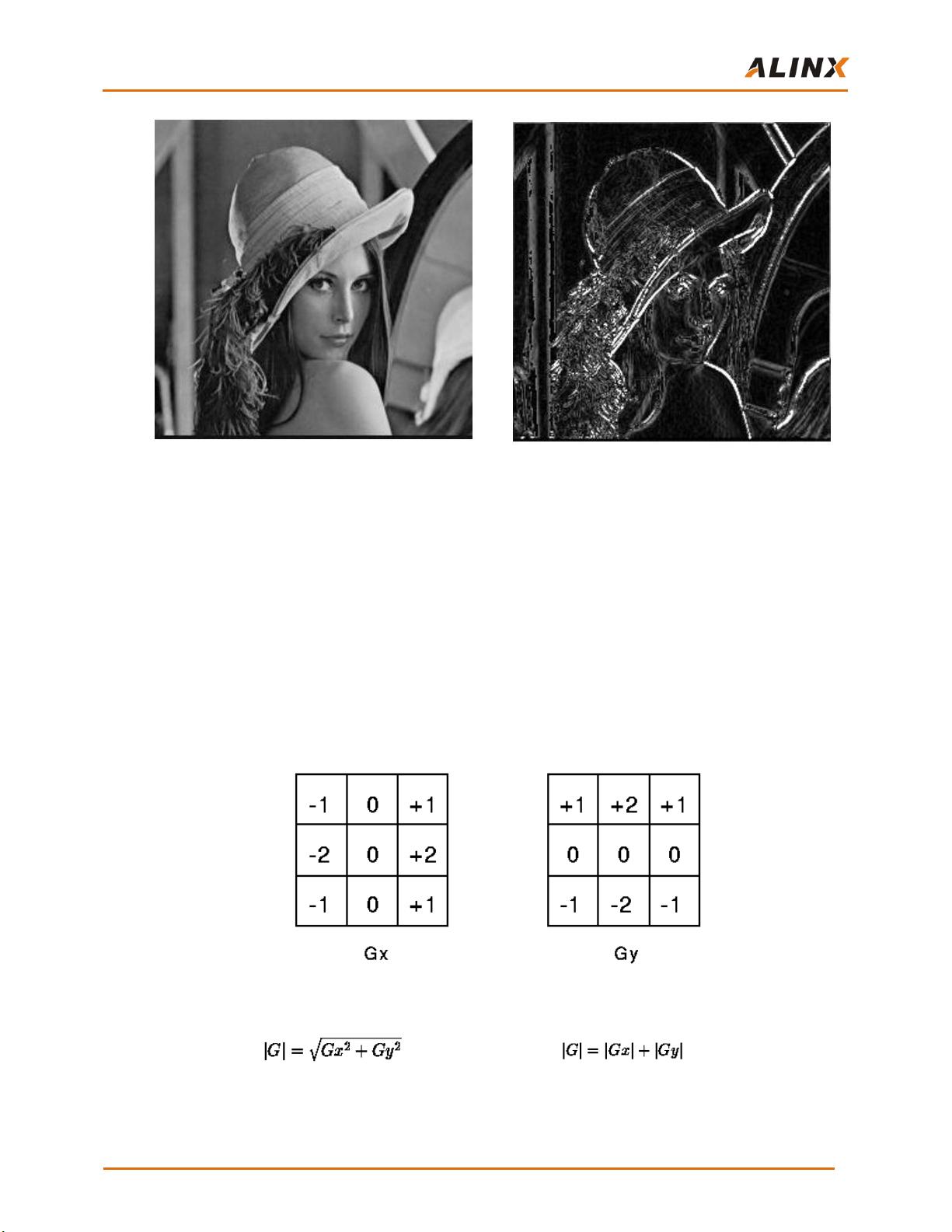

sdram_ov5640_hdmi显示SOBEL边缘检测例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档资料,FPGA为CYCLONE10LP系列中的10CL025YU256C8. 完整的Quartus工程文件,可以做为你的学习设计参考。 module top( input clk, input rst_n, inout cmos_scl, //cmos i2c clock inout cmos_sda, //cmos i2c data input cmos_vsync, //cmos vsync input cmos_href, //cmos hsync refrence,data valid input cmos_pclk, //cmos pxiel clock output cmos_xclk, //cmos externl clock input [7:0] cmos_db, //cmos data //hdmi output output tmds_clk_p, output tmds_clk_n, output[2:0] tmds_data_p, //rgb output[2:0] tmds_data_n, //rgb output sdram_clk, //sdram clock output sdram_cke, //sdram clock enable output sdram_cs_n, //sdram chip select output sdram_we_n, //sdram write enable output sdram_cas_n, //sdram column address strobe output sdram_ras_n, //sdram row address strobe output[1:0] sdram_dqm, //sdram data enable output[1:0] sdram_ba, //sdram bank address output[12:0] sdram_addr, //sdram address inout[15:0] sdram_dq //sdram data ); parameter MEM_DATA_BITS = 16; //external memory user interface data width parameter ADDR_BITS = 24; //external memory user interface address width parameter BUSRT_BITS = 10

sdram_ov5640_hdmi显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档 (295个子文件)

sdram_ov5640_hdmi显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档 (295个子文件)  top.vpr.ammdb 4KB

top.vpr.ammdb 4KB top.root_partition.cmp.ammdb 4KB

top.root_partition.cmp.ammdb 4KB top.map.ammdb 129B

top.map.ammdb 129B top.map.bpm 7KB

top.map.bpm 7KB top.cmp.bpm 7KB

top.cmp.bpm 7KB ddio_out4.bsf 2KB

ddio_out4.bsf 2KB top.cmp.cdb 433KB

top.cmp.cdb 433KB top.rtlv_sg.cdb 222KB

top.rtlv_sg.cdb 222KB top.root_partition.cmp.cdb 165KB

top.root_partition.cmp.cdb 165KB top.map.cdb 134KB

top.map.cdb 134KB top.root_partition.map.cdb 133KB

top.root_partition.map.cdb 133KB top.(16).cnf.cdb 25KB

top.(16).cnf.cdb 25KB top.rtlv_sg_swap.cdb 24KB

top.rtlv_sg_swap.cdb 24KB top.(42).cnf.cdb 21KB

top.(42).cnf.cdb 21KB top.(40).cnf.cdb 17KB

top.(40).cnf.cdb 17KB top.(41).cnf.cdb 17KB

top.(41).cnf.cdb 17KB top.(21).cnf.cdb 13KB

top.(21).cnf.cdb 13KB top.(24).cnf.cdb 12KB

top.(24).cnf.cdb 12KB top.(15).cnf.cdb 12KB

top.(15).cnf.cdb 12KB top.(46).cnf.cdb 11KB

top.(46).cnf.cdb 11KB top.(13).cnf.cdb 11KB

top.(13).cnf.cdb 11KB top.(52).cnf.cdb 10KB

top.(52).cnf.cdb 10KB top.(20).cnf.cdb 10KB

top.(20).cnf.cdb 10KB top.(14).cnf.cdb 10KB

top.(14).cnf.cdb 10KB top.(0).cnf.cdb 10KB

top.(0).cnf.cdb 10KB top.(8).cnf.cdb 9KB

top.(8).cnf.cdb 9KB top.(26).cnf.cdb 8KB

top.(26).cnf.cdb 8KB top.(22).cnf.cdb 8KB

top.(22).cnf.cdb 8KB top.(29).cnf.cdb 7KB

top.(29).cnf.cdb 7KB top.(12).cnf.cdb 6KB

top.(12).cnf.cdb 6KB top.root_partition.map.reg_db.cdb 6KB

top.root_partition.map.reg_db.cdb 6KB top.(23).cnf.cdb 5KB

top.(23).cnf.cdb 5KB top.(9).cnf.cdb 4KB

top.(9).cnf.cdb 4KB top.(17).cnf.cdb 4KB

top.(17).cnf.cdb 4KB top.(32).cnf.cdb 3KB

top.(32).cnf.cdb 3KB top.(31).cnf.cdb 3KB

top.(31).cnf.cdb 3KB top.(19).cnf.cdb 3KB

top.(19).cnf.cdb 3KB top.(25).cnf.cdb 3KB

top.(25).cnf.cdb 3KB top.root_partition.map.hbdb.cdb 3KB

top.root_partition.map.hbdb.cdb 3KB top.(7).cnf.cdb 3KB

top.(7).cnf.cdb 3KB top.(33).cnf.cdb 3KB

top.(33).cnf.cdb 3KB top.map_bb.cdb 2KB

top.map_bb.cdb 2KB top.(44).cnf.cdb 2KB

top.(44).cnf.cdb 2KB top.(38).cnf.cdb 2KB

top.(38).cnf.cdb 2KB top.(36).cnf.cdb 2KB

top.(36).cnf.cdb 2KB top.(27).cnf.cdb 2KB

top.(27).cnf.cdb 2KB top.(18).cnf.cdb 2KB

top.(18).cnf.cdb 2KB top.(1).cnf.cdb 2KB

top.(1).cnf.cdb 2KB top.(4).cnf.cdb 2KB

top.(4).cnf.cdb 2KB top.(47).cnf.cdb 2KB

top.(47).cnf.cdb 2KB top.(34).cnf.cdb 2KB

top.(34).cnf.cdb 2KB top.(28).cnf.cdb 2KB

top.(28).cnf.cdb 2KB top.(53).cnf.cdb 2KB

top.(53).cnf.cdb 2KB top.(2).cnf.cdb 2KB

top.(2).cnf.cdb 2KB top.(5).cnf.cdb 2KB

top.(5).cnf.cdb 2KB top.(45).cnf.cdb 2KB

top.(45).cnf.cdb 2KB top.(43).cnf.cdb 2KB

top.(43).cnf.cdb 2KB top.(3).cnf.cdb 2KB

top.(3).cnf.cdb 2KB top.(6).cnf.cdb 2KB

top.(6).cnf.cdb 2KB top.(51).cnf.cdb 2KB

top.(51).cnf.cdb 2KB top.(10).cnf.cdb 2KB

top.(10).cnf.cdb 2KB top.(11).cnf.cdb 2KB

top.(11).cnf.cdb 2KB top.(48).cnf.cdb 1KB

top.(48).cnf.cdb 1KB top.(54).cnf.cdb 1KB

top.(54).cnf.cdb 1KB top.(39).cnf.cdb 1KB

top.(39).cnf.cdb 1KB top.(35).cnf.cdb 1KB

top.(35).cnf.cdb 1KB top.(37).cnf.cdb 1KB

top.(37).cnf.cdb 1KB top.(49).cnf.cdb 1KB

top.(49).cnf.cdb 1KB top.(55).cnf.cdb 1KB

top.(55).cnf.cdb 1KB top.(30).cnf.cdb 1KB

top.(30).cnf.cdb 1KB top.(50).cnf.cdb 953B

top.(50).cnf.cdb 953B top.(56).cnf.cdb 939B

top.(56).cnf.cdb 939B ddio_out4.cmp 1KB

ddio_out4.cmp 1KB top.db_info 140B

top.db_info 140B top.db_info 140B

top.db_info 140B top.tiscmp.slow_1200mv_85c.ddb 838KB

top.tiscmp.slow_1200mv_85c.ddb 838KB top.tiscmp.slow_1200mv_0c.ddb 835KB

top.tiscmp.slow_1200mv_0c.ddb 835KB top.tiscmp.fast_1200mv_0c.ddb 826KB

top.tiscmp.fast_1200mv_0c.ddb 826KB top.tiscmp.fastest_slow_1200mv_85c.ddb 198KB

top.tiscmp.fastest_slow_1200mv_85c.ddb 198KB top.tiscmp.fastest_slow_1200mv_0c.ddb 198KB

top.tiscmp.fastest_slow_1200mv_0c.ddb 198KB top.asm_labs.ddb 50KB

top.asm_labs.ddb 50KB top.tis_db_list.ddb 302B

top.tis_db_list.ddb 302B top.root_partition.cmp.dfp 33B

top.root_partition.cmp.dfp 33B top.done 26B

top.done 26B top.root_partition.map.dpi 12KB

top.root_partition.map.dpi 12KB top.root_partition.map.hbdb.hb_info 51B

top.root_partition.map.hbdb.hb_info 51B top.pre_map.hdb 98KB

top.pre_map.hdb 98KB top.root_partition.cmp.hdb 91KB

top.root_partition.cmp.hdb 91KB top.rtlv.hdb 87KB

top.rtlv.hdb 87KB top.cmp.hdb 86KB

top.cmp.hdb 86KB top.rrp.hdb 86KB

top.rrp.hdb 86KB top.map.hdb 85KB

top.map.hdb 85KB top.root_partition.map.hbdb.hdb 84KB

top.root_partition.map.hbdb.hdb 84KB top.root_partition.map.hdb 82KB

top.root_partition.map.hdb 82KB top.map_bb.hdb 24KB

top.map_bb.hdb 24KB top.(24).cnf.hdb 6KB

top.(24).cnf.hdb 6KB top.(21).cnf.hdb 5KB

top.(21).cnf.hdb 5KB top.(42).cnf.hdb 5KB

top.(42).cnf.hdb 5KB top.(0).cnf.hdb 4KB

top.(0).cnf.hdb 4KB top.(26).cnf.hdb 4KB

top.(26).cnf.hdb 4KB- 1

- 2

- 3

qq_531528582022-07-01感谢大佬分享的资源,对我启发很大,给了我新的灵感。

qq_531528582022-07-01感谢大佬分享的资源,对我启发很大,给了我新的灵感。 、、、、、、、、、、、、、、、?2024-03-03资源值得借鉴的内容很多,那就浅学一下吧,值得下载!

、、、、、、、、、、、、、、、?2024-03-03资源值得借鉴的内容很多,那就浅学一下吧,值得下载! L1021882024-08-26资源是宝藏资源,实用也是真的实用,感谢大佬分享~

L1021882024-08-26资源是宝藏资源,实用也是真的实用,感谢大佬分享~

- 粉丝: 128

- 资源: 4767

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 毕设和企业适用springboot社交电商类及跨平台协作平台源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及云端储物管理系统源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及远程医疗平台源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及在线系统源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及企业数字化转型平台源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及人工智能医疗平台源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及人力资源管理平台源码+论文+视频.zip

- 毕设和企业适用springboot全渠道电商平台类及汽车信息管理平台源码+论文+视频.zip

- 毕设和企业适用springboot全渠道电商平台类及食品安全追溯平台源码+论文+视频.zip

- 毕设和企业适用springboot全渠道电商平台类及人工智能客服平台源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及在线药品管理平台源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及智慧医疗管理平台源码+论文+视频.zip

- 毕设和企业适用springboot人工智能类及智能农场管理系统源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及食品安全追溯平台源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及数据智能化平台源码+论文+视频.zip

- 毕设和企业适用springboot社交电商类及在线教育互动平台源码+论文+视频.zip

信息提交成功

信息提交成功