OV5640摄像头+SDRAM显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

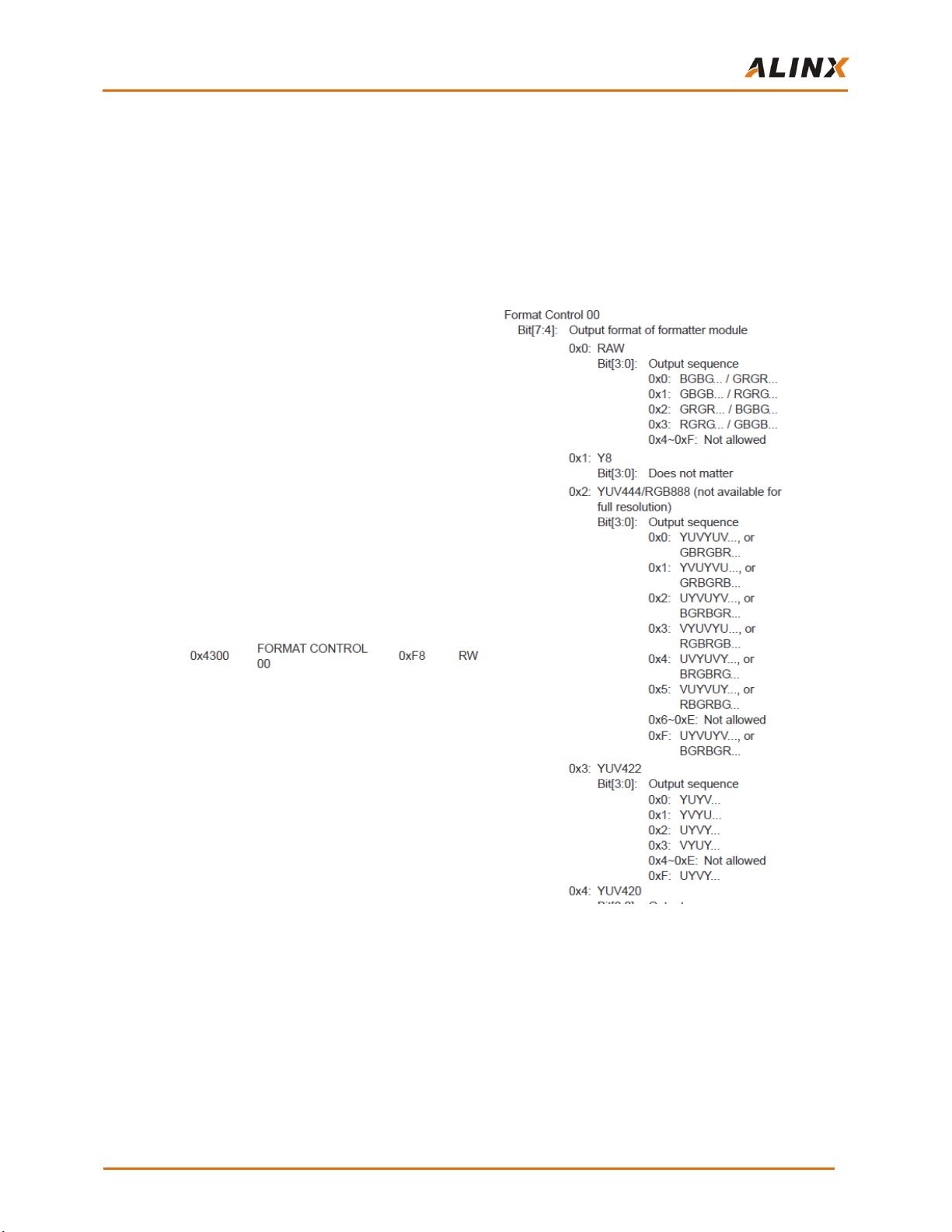

OV5640摄像头+SDRAM显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档资料,FPGA为CYCLONE10LP系列中的10CL025YU256C8. 完整的Quartus工程文件,可以做为你的学习设计参考。 采用 500 万像素的 OV5640 摄像头模组(模块型号:AN5640)为大家显示更高分辨率 的视频画面。OV5640 摄像头模组最大支持 QSXGA (2592x1944)的拍照功能,支持 1080P、720P、 VGA、QVGA 视频图像输出。本实验将 OV5640 配置为 RGB565 输出,先将视频数据写入外部存储 器,再从外部存储器读取送到 VGA、LCD 等显示模块。 module top( input clk, input rst_n, inout cmos_scl, //cmos i2c clock inout cmos_sda, //cmos i2c data input cmos_vsync, //cmos vsync input cmos_href, //cmos hsync refrence,data valid input cmos_pclk, //cmos pxiel clock output cmos_xclk, //cmos externl clock input [7:0] cmos_db, //cmos data //output cmos_rst_n, //cmos reset //output cmos_pwdn, //cmos power down //hdmi output output tmds_clk_p, output tmds_clk_n, output[2:0] tmds_data_p, //rgb output[2:0] tmds_data_n, //rgb output sdram_clk, //sdram clock output sdram_cke, //sdram clock enable output sdram_cs_n, //sdram chip select output sdram_we_n, //sdram write enable output sdram_cas_n, //sdram column address strobe output sdram_ras_n, //sdram row address strobe output[1:0] sdram_dqm, //sdram data enable output[1:0] sdram_ba, //sdram bank address output[12:0] sdram_addr, //sdram address inout[15:0] sdram_dq //sdram data );

OV5640摄像头+SDRAM显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档 (880个子文件)

OV5640摄像头+SDRAM显示例程Cyclone10 FPGA Verilog源码Quartus17.1工程文件+文档 (880个子文件)  top.vpr.ammdb 5KB

top.vpr.ammdb 5KB top.autos_3e921.cmp.ammdb 3KB

top.autos_3e921.cmp.ammdb 3KB top.vpr.ammdb 3KB

top.vpr.ammdb 3KB top.root_partition.cmp.ammdb 3KB

top.root_partition.cmp.ammdb 3KB top.root_partition.cmp.ammdb 3KB

top.root_partition.cmp.ammdb 3KB top.root_partition.cmp.ammdb 3KB

top.root_partition.cmp.ammdb 3KB top.vpr.ammdb 3KB

top.vpr.ammdb 3KB top.autoh_e40e1.cmp.ammdb 602B

top.autoh_e40e1.cmp.ammdb 602B top.map.ammdb 129B

top.map.ammdb 129B top.map.ammdb 129B

top.map.ammdb 129B top.map.ammdb 129B

top.map.ammdb 129B top.map.bpm 18KB

top.map.bpm 18KB top.cmp.bpm 17KB

top.cmp.bpm 17KB top.map.bpm 5KB

top.map.bpm 5KB top.cmp.bpm 5KB

top.cmp.bpm 5KB top.map.bpm 4KB

top.map.bpm 4KB top.cmp.bpm 4KB

top.cmp.bpm 4KB top.cmp.cdb 505KB

top.cmp.cdb 505KB top.cmp.cdb 402KB

top.cmp.cdb 402KB top.cmp.cdb 280KB

top.cmp.cdb 280KB top.rtlv_sg.cdb 186KB

top.rtlv_sg.cdb 186KB top.rtlv_sg.cdb 172KB

top.rtlv_sg.cdb 172KB top.rtlv_sg.cdb 169KB

top.rtlv_sg.cdb 169KB top.root_partition.cmp.cdb 157KB

top.root_partition.cmp.cdb 157KB top.map.cdb 153KB

top.map.cdb 153KB top.map.cdb 128KB

top.map.cdb 128KB top.root_partition.map.cdb 128KB

top.root_partition.map.cdb 128KB top.root_partition.cmp.cdb 120KB

top.root_partition.cmp.cdb 120KB top.root_partition.cmp.cdb 112KB

top.root_partition.cmp.cdb 112KB top.root_partition.map.cdb 94KB

top.root_partition.map.cdb 94KB top.map.cdb 90KB

top.map.cdb 90KB top.root_partition.map.cdb 90KB

top.root_partition.map.cdb 90KB top.autos_3e921.cmp.cdb 74KB

top.autos_3e921.cmp.cdb 74KB top.autos_3e921.map.cdb 53KB

top.autos_3e921.map.cdb 53KB top.(36).cnf.cdb 27KB

top.(36).cnf.cdb 27KB top.(11).cnf.cdb 25KB

top.(11).cnf.cdb 25KB top.(12).cnf.cdb 21KB

top.(12).cnf.cdb 21KB top.(11).cnf.cdb 21KB

top.(11).cnf.cdb 21KB top.(32).cnf.cdb 21KB

top.(32).cnf.cdb 21KB top.(33).cnf.cdb 21KB

top.(33).cnf.cdb 21KB top.(3).cnf.cdb 21KB

top.(3).cnf.cdb 21KB top.rtlv_sg_swap.cdb 18KB

top.rtlv_sg_swap.cdb 18KB top.autoh_e40e1.cmp.cdb 17KB

top.autoh_e40e1.cmp.cdb 17KB top.rtlv_sg_swap.cdb 17KB

top.rtlv_sg_swap.cdb 17KB top.(31).cnf.cdb 17KB

top.(31).cnf.cdb 17KB top.(30).cnf.cdb 17KB

top.(30).cnf.cdb 17KB top.(30).cnf.cdb 17KB

top.(30).cnf.cdb 17KB top.(40).cnf.cdb 17KB

top.(40).cnf.cdb 17KB top.(31).cnf.cdb 17KB

top.(31).cnf.cdb 17KB top.(32).cnf.cdb 17KB

top.(32).cnf.cdb 17KB top.(41).cnf.cdb 17KB

top.(41).cnf.cdb 17KB top.rtlv_sg_swap.cdb 16KB

top.rtlv_sg_swap.cdb 16KB top.(83).cnf.cdb 15KB

top.(83).cnf.cdb 15KB top.autoh_e40e1.map.cdb 14KB

top.autoh_e40e1.map.cdb 14KB top.(40).cnf.cdb 12KB

top.(40).cnf.cdb 12KB top.(11).cnf.cdb 12KB

top.(11).cnf.cdb 12KB top.(10).cnf.cdb 12KB

top.(10).cnf.cdb 12KB top.(10).cnf.cdb 12KB

top.(10).cnf.cdb 12KB top.(34).cnf.cdb 11KB

top.(34).cnf.cdb 11KB top.(8).cnf.cdb 11KB

top.(8).cnf.cdb 11KB top.(9).cnf.cdb 11KB

top.(9).cnf.cdb 11KB top.(8).cnf.cdb 11KB

top.(8).cnf.cdb 11KB top.(45).cnf.cdb 11KB

top.(45).cnf.cdb 11KB top.(15).cnf.cdb 10KB

top.(15).cnf.cdb 10KB top.(15).cnf.cdb 10KB

top.(15).cnf.cdb 10KB top.(10).cnf.cdb 10KB

top.(10).cnf.cdb 10KB top.(9).cnf.cdb 10KB

top.(9).cnf.cdb 10KB top.(9).cnf.cdb 10KB

top.(9).cnf.cdb 10KB top.(16).cnf.cdb 10KB

top.(16).cnf.cdb 10KB top.(34).cnf.cdb 9KB

top.(34).cnf.cdb 9KB top.(0).cnf.cdb 9KB

top.(0).cnf.cdb 9KB top.(0).cnf.cdb 9KB

top.(0).cnf.cdb 9KB top.(32).cnf.cdb 8KB

top.(32).cnf.cdb 8KB top.(17).cnf.cdb 8KB

top.(17).cnf.cdb 8KB top.(16).cnf.cdb 8KB

top.(16).cnf.cdb 8KB top.(0).cnf.cdb 8KB

top.(0).cnf.cdb 8KB top.(20).cnf.cdb 7KB

top.(20).cnf.cdb 7KB top.(43).cnf.cdb 7KB

top.(43).cnf.cdb 7KB top.(19).cnf.cdb 7KB

top.(19).cnf.cdb 7KB top.(19).cnf.cdb 7KB

top.(19).cnf.cdb 7KB top.(35).cnf.cdb 7KB

top.(35).cnf.cdb 7KB top.(41).cnf.cdb 7KB

top.(41).cnf.cdb 7KB top.(8).cnf.cdb 6KB

top.(8).cnf.cdb 6KB top.(7).cnf.cdb 6KB

top.(7).cnf.cdb 6KB top.(7).cnf.cdb 6KB

top.(7).cnf.cdb 6KB top.(60).cnf.cdb 6KB

top.(60).cnf.cdb 6KB top.(54).cnf.cdb 5KB

top.(54).cnf.cdb 5KB top.(85).cnf.cdb 5KB

top.(85).cnf.cdb 5KB top.root_partition.map.reg_db.cdb 5KB

top.root_partition.map.reg_db.cdb 5KB top.(79).cnf.cdb 5KB

top.(79).cnf.cdb 5KB top.(35).cnf.cdb 4KB

top.(35).cnf.cdb 4KB top.(37).cnf.cdb 4KB

top.(37).cnf.cdb 4KB top.(39).cnf.cdb 4KB

top.(39).cnf.cdb 4KB top.(69).cnf.cdb 4KB

top.(69).cnf.cdb 4KB top.(49).cnf.cdb 4KB

top.(49).cnf.cdb 4KB top.(48).cnf.cdb 4KB

top.(48).cnf.cdb 4KB top.(61).cnf.cdb 4KB

top.(61).cnf.cdb 4KB top.(68).cnf.cdb 4KB

top.(68).cnf.cdb 4KB top.(74).cnf.cdb 4KB

top.(74).cnf.cdb 4KB top.(13).cnf.cdb 4KB

top.(13).cnf.cdb 4KB- 1

- 2

- 3

- 4

- 5

- 6

- 9

- 粉丝: 88

- 资源: 5818

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功

- 1

- 2

前往页