没有合适的资源?快使用搜索试试~ 我知道了~

pg153-axi-quad-spi.pdf

需积分: 0 1 下载量 116 浏览量

2023-11-04

23:39:31

上传

评论

收藏 2.08MB PDF 举报

温馨提示

试读

110页

pg153-axi-quad-spi.pdf

资源推荐

资源详情

资源评论

LogiCORE IP AXI

Quad SPI v3.1

Product Guide for Vivado

Design Suite

PG153 December 18, 2013

AXI Quad SPI v3.1 www.xilinx.com 2

PG153 December 18, 2013

Table of Contents

IP Facts

Chapter 1: Overview

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Unsupported Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Specification Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Protocol Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Chapter 4: Customizing and Generating the Core

Vivado Integrated Design Environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Output Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Chapter 5: Constraining the Core

Chapter 6: Simulation

Chapter 7: Synthesis and Implementation

AXI Quad SPI v3.1 www.xilinx.com 3

PG153 December 18, 2013

Chapter 8: Example Design

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Implementing the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Testing the Example Design on a KC705 Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Chapter 9: Test Bench

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Simulating the Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Appendix A: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Appendix C: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Notice of Disclaimer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Send Feedback

AXI Quad SPI v3.1 www.xilinx.com 4

PG153 December 18, 2013 Product Specification

Introduction

The LogiCORE™ IP AXI Quad Serial Peripheral Interface

(SPI) core connects the AXI4 interface to those SPI slave

devices that support the Standard, Dual or Quad SPI

protocol instruction set. This core provides a serial

interface to SPI slave devices. The Dual/Quad SPI is an

enhancement to the Standard SPI protocol (described in

the Motorola M68HC11 data sheet) and provides a simple

method for data exchange between a master and a slave.

Features

• Configurable AXI4 interface; when configured with an

AXI4-Lite interface the core is backward compatible

with version 1.00 of the core (Legacy mode)

• Configurable AXI4 interface for burst mode operation

for Data Receive Register (DRR) and Data Transmit

Register (DTR) FIFO

• Configurable eXecute In Place (XIP) mode of

operation

• Connects as a 32-bit slave on either AXI4-Lite or AXI4

memory mapped interface

• Configurable SPI modes:

°

Standard SPI mode

°

Dual SPI mode

°

Quad SPI mode

• Standard SPI interfaces:

°

IO0 (MOSI) - Standard SPI mode

°

IO1 (MISO) - Standard SPI mode

°

SCK - Standard and Dual SPI mode

°

x SS - Standard and Dual SPI mode

• In Quad SPI mode supports six signal interfaces: IO0,

IO1, IO2, IO3, SCK and SS

• Up to 32 configurable SPI slaves

• Programmable SPI clock phase and polarity

• Configurable FIFO depth (16 or 256 element deep in

Dual/Quad/Standard SPI mode) and fixed FIFO depth

of 64 in XIP mode

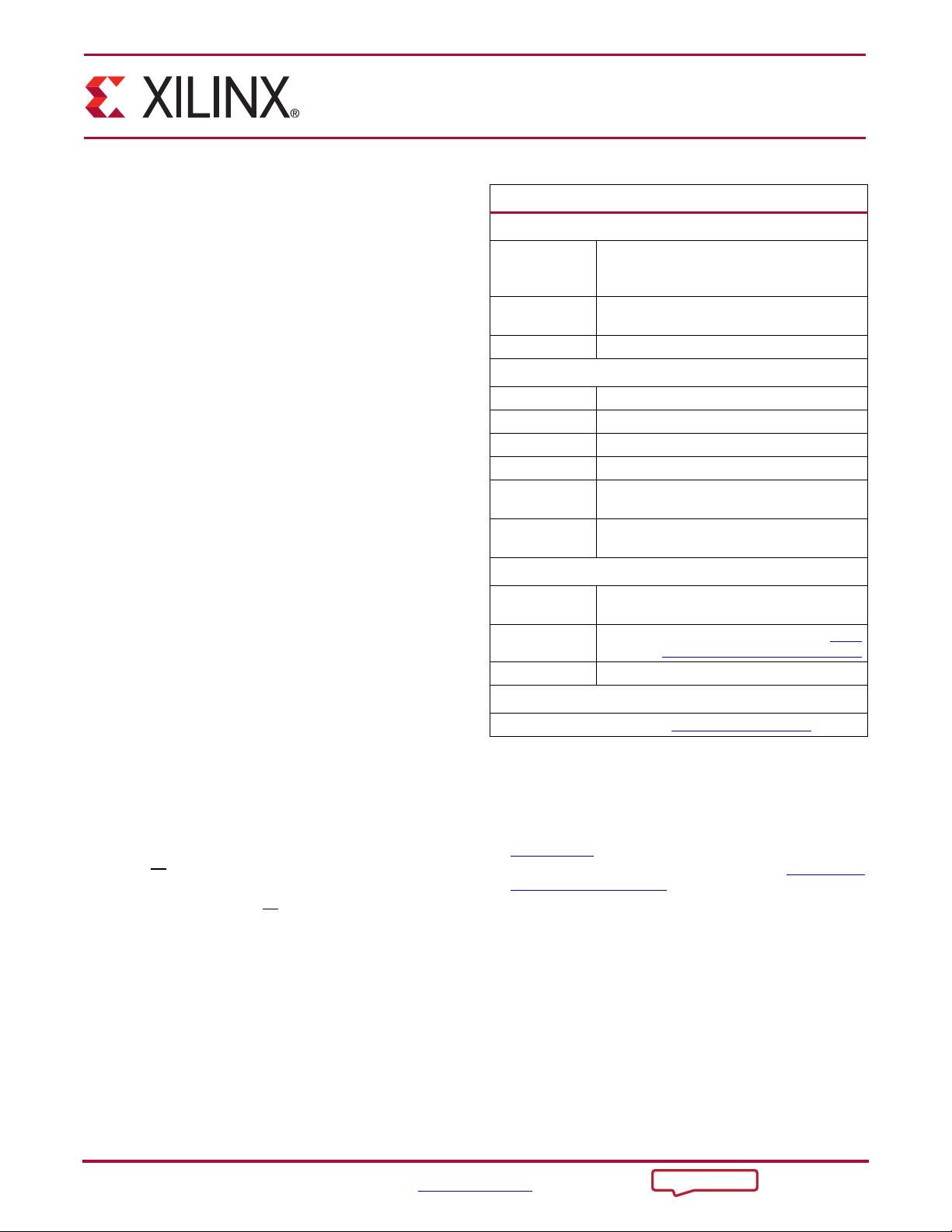

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

UltraScale™ Architecture,

Zynq®-7000 All Programmable SoC,

7 Series FPGAs

Supported User

Interfaces

AXI4, AXI4-Lite

Resources See Ta bl e 2-3 through Table 2-5

Provided with Core

Design Files RTL

Example Design VHDL

Test B enc h VHDL

Constraints File XDC

Simulation

Model

Not Provided

Supported

S/W Driver

(2)

Standalone and Linux

Tested Design Flows

(3)

Design Entry

Vivado® Design Suite

Vivado IP integrator

Simulation

For a list of supported simulators, see the Xilinx

Design Tools: Release Notes Guide

Synthesis Vivado synthesis

Support

Provided by Xilinx @ www.xilinx.com/support

Notes:

1. For a complete list of supported devices, see Vivado IP

catalog.

2. Standalone driver details can be found in the SDK directory

(<install_directory>/doc/usenglish/xilinx_drivers.htm). Linux

OS and driver support information is available from

w

iki.xilinx.com.

3. For the supported versions of the tools, see the Xilinx Design

Tools: Release Notes Guide.

Send Feedback

AXI Quad SPI v3.1 www.xilinx.com 5

PG153 December 18, 2013

Chapter 1

Overview

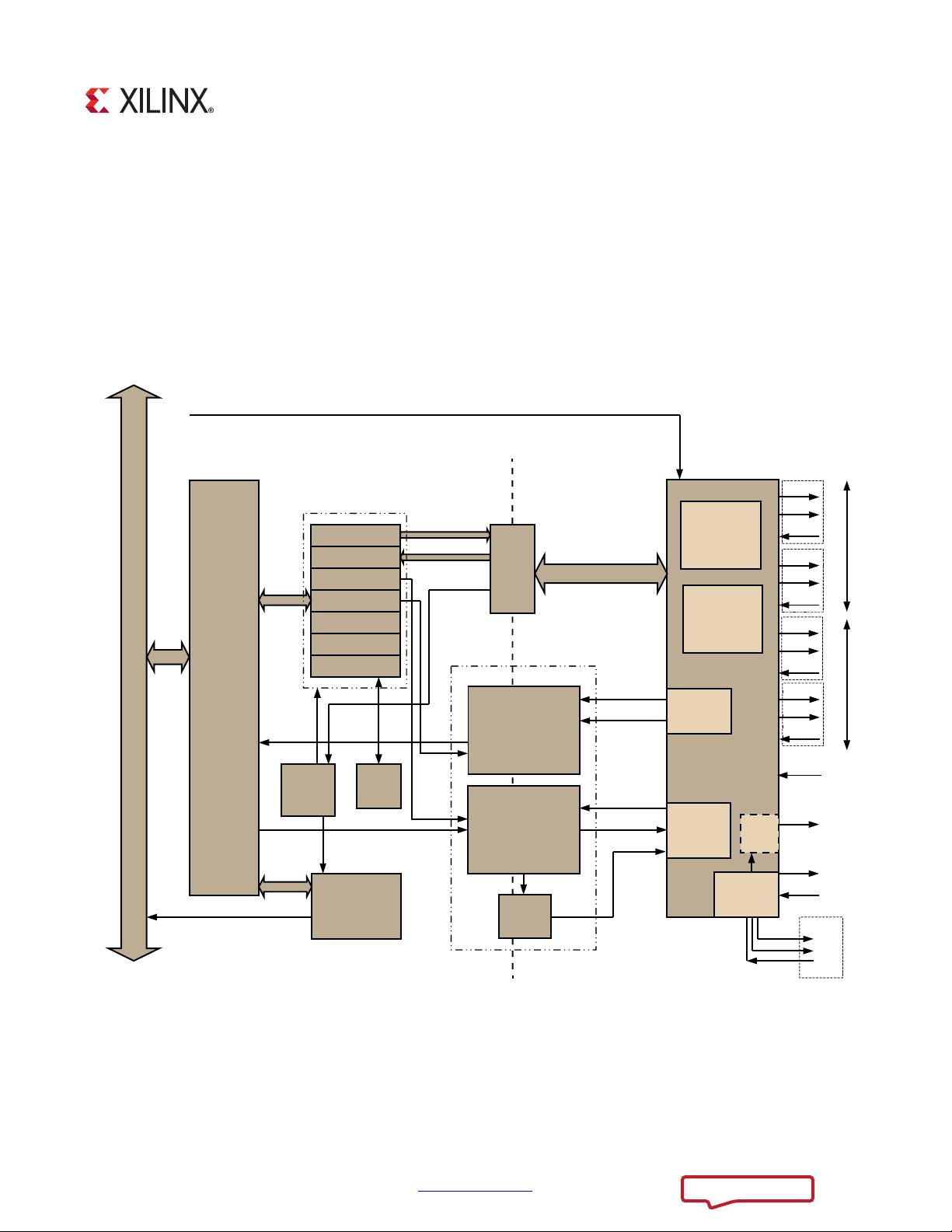

The top-level block diagram for the AXI Quad SPI core when configured with the AXI4-Lite

interface option is shown in Figure 1-1.

X-Ref Target - Figure 1-1

Figure 1-1: AXI Quad SPI Core Top-Level Block Diagram

)0)#

)NTERFACE

48&)&/

28&)&/

2D%NABLE

4X$ATA

7R%NABLE

2X$ATA

)NTERRUPT#ONTROLLER

)0)%2

)0)32

$')%2

2X/##2EG

4X/##2EG

30)332

30)$22

30)$42

30)32

30)#2

/##

#OUNTER

#$#

"LOCK

2EGISTER-ODULE

4X

AND

2X

#OUNTER

30)4RANSFER

$ONE

30)3%,-/$&

30)8FER$ONE

34!2450

"LOCK

#-$#OMPARE

AND

"EHAVIOR

3IGNALS

SCK?O

SCK?T

SCK?I

IO?O

IO?T

IO?I

IO?O

IO?T

IO?I

IO?O

IO?T

IO?I

IO?O

IO?T

IO?I

SPISEL

EXT?SPI?CLK

30)#LK

'ENERATOR

30)

2ECEIVE

$ATA,OGIC

30)

4RANSMIT

$ATA,OGIC

30)-ODE

,OGIC

30)-ODE

AND,OGIC

!8)#,+

$OMAIN

30)#,+

$OMAIN

BUSIP?DATA$42

IPBUS?DATA

$22

SS?O

SS?T

SS?I

!8)

/NLYIN1UAD30)-ODE 3TD$UAL1UAD30)-ODE

8

Send Feedback

剩余109页未读,继续阅读

资源评论

zxiang_8888

- 粉丝: 12

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功