AXI Interconnect v2.1

LogiCORE IP Product Guide

Vivado Design Suite

PG059 December 20, 2017

AXI Interconnect Product Guide v2.1 2

PG059 December 20, 2017 www.xilinx.com

Table of Contents

IP Facts

Chapter 1: Overview

AXI Infrastructure Cores . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

AXI Interconnect Core Limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Licensing and Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Chapter 2: Product Specification

Use Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Maximum Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Chapter 3: Designing with the Core

AXI Interconnect Core Functionality. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Design Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Clocking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

Send Feedback

AXI Interconnect Product Guide v2.1 3

PG059 December 20, 2017 www.xilinx.com

Chapter 5: Example Design

Appendix A: Upgrading

Migration from CORE Generator System AXI Interconnect v1.x Core . . . . . . . . . . . . . . . . . . . . . . 160

Migration from XPS AXI Interconnect v1.x Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Appendix B: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Debug Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Appendix C: Definitions, Acronyms, and Abbreviations

Appendix D: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Send Feedback

AXI Interconnect Product Guide v2.1 4

PG059 December 20, 2017 www.xilinx.com Product Specification

Introduction

The Xilinx® LogiCORE™ IP AXI Interconnect

core connects one or more AXI

memory-mapped master devices to one or

more memory-mapped slave devices.

Note:

The AXI Interconnect core is intended for

memory-mapped transfers only. For AXI4-Stream

transfers, see the AXI4-Stream Infrastructure IP Suite

LogiCORE IP Product Guide (PG085) [Ref 1].

Features

The AXI Interconnect core is comprised of

multiple LogiCORE IP instances (infrastructure

cores). Each of the AXI4 memory-mapped

infrastructure cores that comprise the AXI

Interconnect core are fully described in this

document. The following features apply to the

AXI Interconnect core in general and to all

infrastructure cores described in this document

unless otherwise noted:

• AXI protocol compliant. Can be configured

to support AXI3, AXI4, and AXI4-Lite

protocols

• Interface data widths:

°

AXI4 and AXI3: 32, 64, 128, 256, 512, or

1,024 bits

°

AXI4-Lite: 32 or 64 bits

• Address width: Up to 64 bits

• USER width (per channel): Up to 1,024 bits

• ID width: Up to 32 bits

• Support for Read-only and Write-only

masters and slaves, resulting in reduced

resource utilization

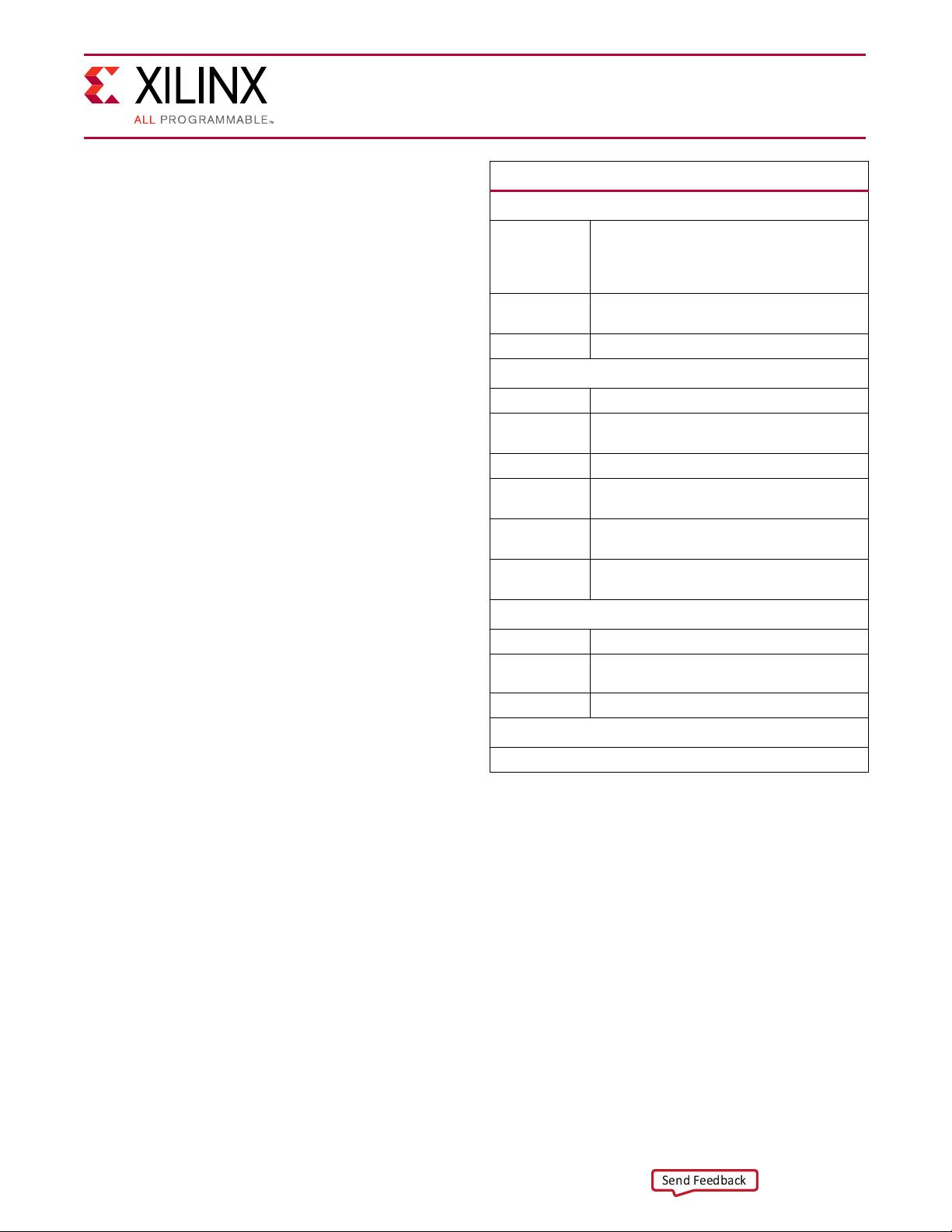

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

UltraScale+™,

UltraScale™,

7 Series FPGAs

Zynq®-7000

Supported

User Interfaces

AXI4, AXI4-Lite, AXI3

Resources See Tab le 2-16 through Tab le 2-2 6.

Provided with Core

Design Files Verilog and VHDL

Example

Design

Not Provided

Test Bench Not Provided

Constraints

File

Xilinx Design Constraints (XDC)

Simulation

Model

Not Provided

Supported

S/W Driver

N/A

Tested Design Flows

(2)

Design Entry Vivado® Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

Send Feedback

AXI Interconnect Product Guide v2.1 5

PG059 December 20, 2017 www.xilinx.com

Chapter 1

Overview

The AXI Interconnect core can only be added to a Vivado® IP integrator block design in the

Vivado Design Suite. The Interconnect IP core represents a hierarchical design block

containing multiple LogiCORE™ IP instances (infrastructure cores) that become configured

and connected during your system design session. Each of the infrastructure cores can also

be added directly to a block design (outside of the AXI Interconnect core) or selected

directly from the Vivado IP Catalog and configured for use in an HDL design.

The AXI Interconnect core allows any mixture of AXI master and slave devices to be

connected to it, which can vary from one another in terms of data width, clock domain and

AXI sub-protocol (AXI4, AXI3, or AXI4-Lite). When the interface characteristics of any

connected master or slave device differ from those of the crossbar switch inside the

interconnect, the appropriate infrastructure cores are automatically inferred and connected

within the interconnect to perform the necessary conversions.

AXI Infrastructure Cores

The following IP cores, described in this document, can be included within each instance of

the AXI Interconnect core, depending on the configuration of AXI Interconnect core and its

connectivity in the IP integrator block design:

• AXI Crossbar connects one or more similar AXI memory-mapped masters to one or

more similar memory-mapped slaves.

• AXI Data Width Converter connects one AXI memory-mapped master to one AXI

memory-mapped slave having a wider or narrower datapath.

• AXI Clock Converter connects one AXI memory-mapped master to one AXI

memory-mapped slave operating in a different clock domain.

• AXI Protocol Converter connects one AXI4, AXI3 or AXI4-Lite master to one AXI slave

of a different AXI memory-mapped protocol.

• AXI Data FIFO connects one AXI memory-mapped master to one AXI memory-mapped

slave through a set of FIFO buffers.

• AXI Register Slice connects one AXI memory-mapped master to one AXI

memory-mapped slave through a set of pipeline registers, typically to break a critical

timing path.

• AXI MMU provides address range decoding and remapping services for AXI

Interconnect.

Send Feedback

评论0