没有合适的资源?快使用搜索试试~ 我知道了~

SAMSUNG-K7A801800B.pdf

需积分: 5 0 下载量 56 浏览量

2021-04-29

16:32:07

上传

评论

收藏 402KB PDF 举报

温馨提示

试读

18页

SAMSUNG-K7A801800B.pdf

资源详情

资源评论

资源推荐

K7A801800B

256Kx36 & 512Kx18 Synchronous SRAM

- 1 -

Rev 3.0

Nov. 2003

K7A803600B

Document Title

256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

Revision History

Rev. No.

0.0

0.1

0.2

0.3

1.0

2.0

2.1

3.0

Remark

Preliminary

Preliminary

Preliminary

Preliminary

Final

Final

Final

Final

History

Initial draft

1. Delete pass- through

1. Add x32 org part and industrial temperature part

1. change scan order(1) form 4T to 6T at 119BGA(x18)

1. Final spec release

2. Change I

SB2 form 50mA to 60mA

Change ordering information( remove 225MHz at SPB)

1. Delete 119BGA package

1. Remove x32 organization

Draft Date

May. 18 . 2001

June. 26. 2001

Aug. 11. 2001

Aug. 28. 2001

Nov. 16. 2001

April. 01. 2002

April. 04. 2003

Nov. 17. 2003

K7A801800B

256Kx36 & 512Kx18 Synchronous SRAM

- 2 -

Rev 3.0

Nov. 2003

K7A803600B

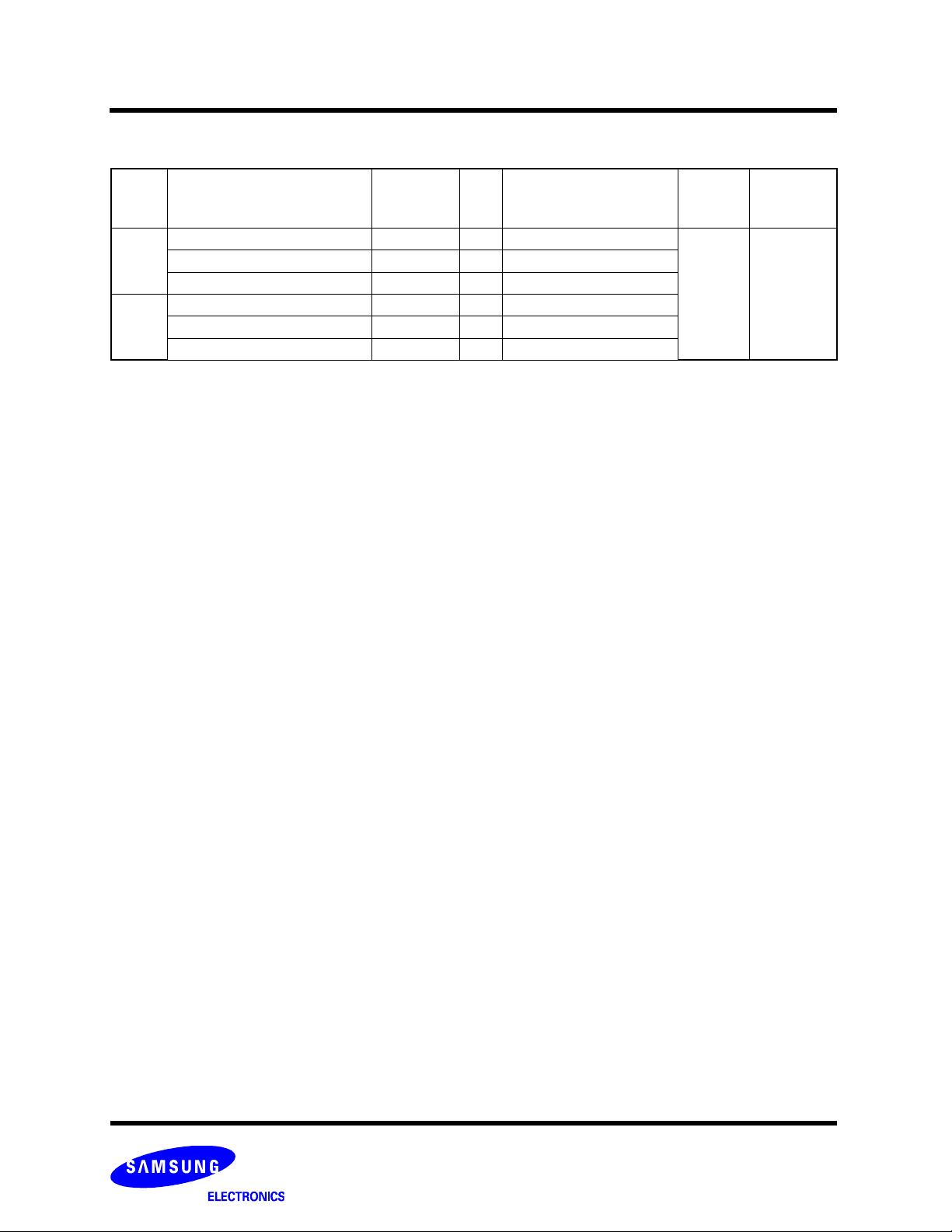

8Mb SB/SPB Synchronous SRAM Ordering Information

Org. Part Number Mode VDD

Speed

FT ; Access Time(ns)

Pipelined ; Cycle Time(MHz)

PKG Temp

512Kx18

K7B801825B-QC(I)65/75 SB 3.3 6.5/7.5 ns

Q:

100TQFP

C:

Commercial

Temperature

Range

I:

Industrial

Temperature

Range

K7A801800B-QC(I)16/14 SPB(2E1D) 3.3 167/138 MHz

K7A801809B-QC(I)25 SPB(2E1D) 3.3 250 MHz

256Kx36

K7B803625B-QC(I)65/75 SB 3.3 6.5/7.5 ns

K7A803600B-QC(I)16/14 SPB(2E1D) 3.3 167/138 MHz

K7A803609B-QC(I)25 SPB(2E1D) 3.3 250 MHz

K7A801800B

256Kx36 & 512Kx18 Synchronous SRAM

- 3 -

Rev 3.0

Nov. 2003

K7A803600B

256Kx36 & 512Kx18-bit Synchronous Pipelined Burst SRAM

The K7A803600B and K7A801800B are 9,437,184-bit Syn-

chronous Static Random Access Memory designed for high

performance second level cache of Pentium and Power PC

based System.

It is organized as 256K(512K) words of 36(18) bits and inte-

grates address and control registers, a 2-bit burst address

counter and added some new functions for high perfor-

mance cache RAM applications; GW

, BW, LBO, ZZ. Write

cycles are internally self-timed and synchronous.

Full bus-width write is done by GW

, and each byte write is

performed by the combination of WE

x and BW when GW is

high. And with CS

1 high, ADSP is blocked to control signals.

Burst cycle can be initiated with either the address status

processor(ADSP

) or address status cache controller(ADSC)

inputs. Subsequent burst addresses are generated inter-

nally in the system¢s burst sequence and are controlled by

the burst address advance(ADV

) input.

LBO

pin is DC operated and determines burst sequence(lin-

ear or interleaved).

ZZ pin controls Power Down State and reduces Stand-by

current regardless of CLK.

The K7A803600B and K7A801800B are fabricated using

SAMSUNG¢s high performance CMOS technology and is

available in a 100pin TQFP and Multiple power and ground

pins are utilized to minimize ground bounce.

GENERAL DESCRIPTIONFEATURES

• Synchronous Operation.

• 2 Stage Pipelined operation with 4 Burst.

• On-Chip Address Counter.

• Self-Timed Write Cycle.

• On-Chip Address and Control Registers.

• 3.3V+0.165V/-0.165V Power Supply.

• I/O Supply Voltage 3.3V+0.165V/-0.165V for 3.3V I/O

or 2.5V+0.4V/-0.125V for 2.5V I/O

• 5V Tolerant Inputs Except I/O Pins.

• Byte Writable Function.

• Global Write Enable Controls a full bus-width write.

• Power Down State via ZZ Signal.

• LBO

Pin allows a choice of either a interleaved burst or a linear

burst.

• Three Chip Enables for simple depth expansion with No Data

Contention only for TQFP ; 2cycle Enable, 1cycle Disable.

• Asynchronous Output Enable Control.

• ADSP

, ADSC, ADV Burst Control Pins.

• TTL-Level Three-State Output.

• 100-TQFP-1420A

• Operating in commeical and industrial temperature range.

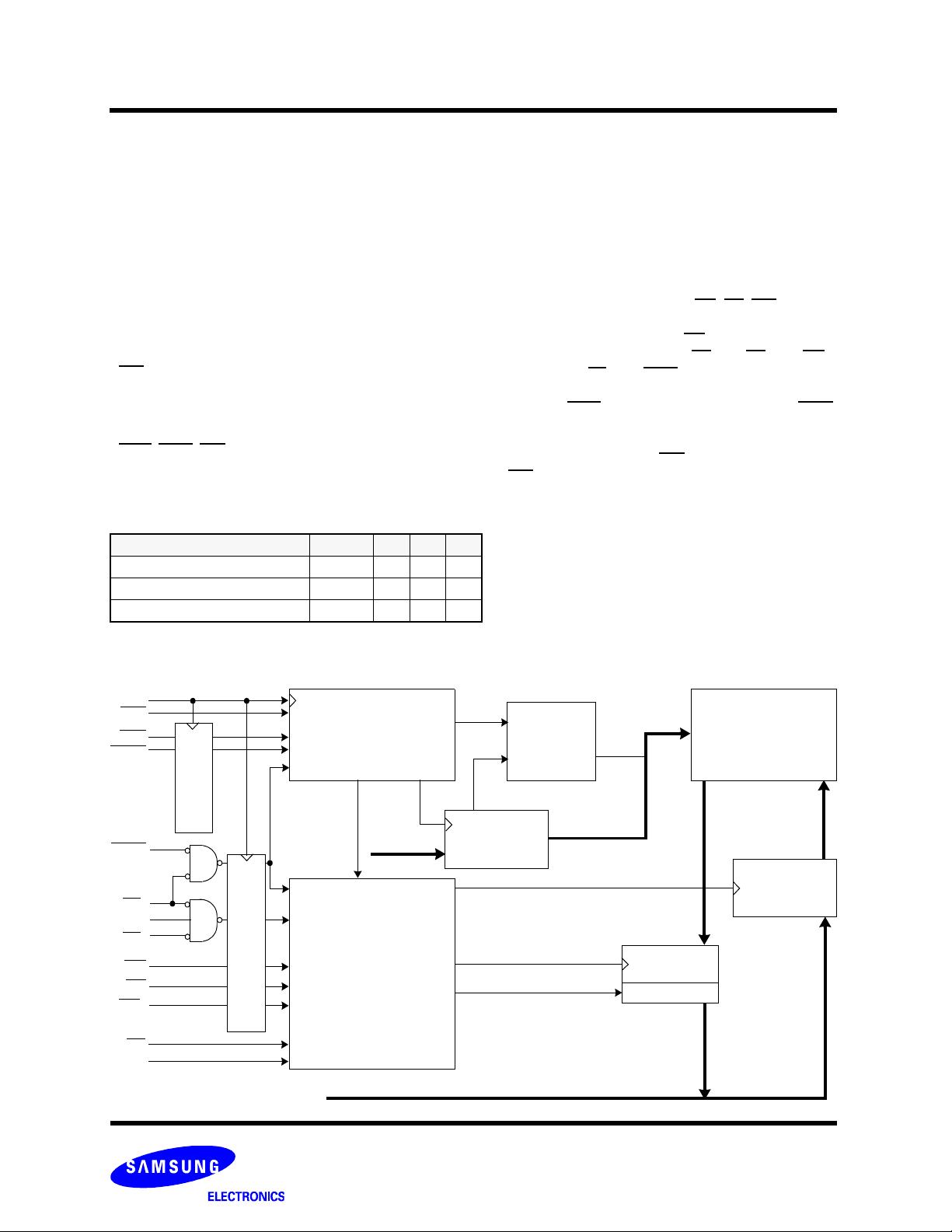

FAST ACCESS TIMES

PARAMETER Symbol -16 -14 Unit

Cycle Time tCYC 6.0 7.2 ns

Clock Access Time tCD 3.5 3.8 ns

Output Enable Access Time tOE 3.5 3.8 ns

LOGIC BLOCK DIAGRAM

CLK

LBO

ADV

ADSC

ADSP

CS

1

CS

2

CS

2

GW

BW

WEx

OE

ZZ

DQa0 ~ DQd7 or DQa0 ~ DQb7

BURST CONTROL

LOGIC

BURST

256Kx36 , 512Kx18

ADDRESS

CONTROL

OUTPUT

DATA-IN

ADDRESS

COUNTER

MEMORY

ARRAY

REGISTER

REGISTER

BUFFER

LOGIC

CONTROL

REGISTER

CONTROL

REGISTER

A

′

0

~A

′

1

A

0

~A

1

or A

2

~A

18

or A

0

~A

18

REGISTER

DQPa ~ DQPd

A

0

~A

17

A

2

~A

17

(x=a,b,c,d or a,b)

DQPa,DQPb

剩余17页未读,继续阅读

LC灵灵

- 粉丝: 1

- 资源: 261

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0