Contents

FIFO Intel

®

FPGA IP User Guide......................................................................................... 3

Configuration Methods.................................................................................................. 3

Specifications.............................................................................................................. 4

Verilog HDL Prototype..........................................................................................4

VHDL Component Declaration............................................................................... 4

VHDL LIBRARY-USE Declaration............................................................................ 4

FIFO Signals.......................................................................................................4

FIFO Parameter Settings...................................................................................... 8

FIFO Functional Timing Requirements........................................................................... 11

SCFIFO ALMOST_EMPTY Functional Timing.................................................................... 12

FIFO Output Status Flag and Latency............................................................................ 13

FIFO Metastability Protection and Related Options...........................................................15

FIFO Synchronous Clear and Asynchronous Clear Effect...................................................17

Recovery and Removal Timing Violation Warnings when Compiling a DCFIFO.............18

SCFIFO and DCFIFO Show-Ahead Mode......................................................................... 19

Different Input and Output Width................................................................................. 20

DCFIFO Timing Constraint Setting.................................................................................21

Embedded Timing Constraint.............................................................................. 21

User Configurable Timing Constraint.................................................................... 22

Coding Example for Manual Instantiation....................................................................... 25

Design Example......................................................................................................... 26

Gray-Code Counter Transfer at the Clock Domain Crossing...............................................30

Guidelines for Embedded Memory ECC Feature...............................................................31

FIFO Intel FPGA IP User Guide Archives.........................................................................32

Document Revision History for the FIFO Intel FPGA IP User Guide..................................... 33

Contents

FIFO Intel

®

FPGA IP User Guide

Send Feedback

2

FIFO Intel

®

FPGA IP User Guide

Intel

®

provides FIFO Intel FPGA IP core through the parameterizable single-clock FIFO

(SCFIFO) and dual-clock FIFO (DCFIFO) functions. The FIFO functions are mostly

applied in data buffering applications that comply with the first-in-first-out data flow in

synchronous or asynchronous clock domains.

The specific names of the FIFO functions are as follows:

• SCFIFO: single-clock FIFO

• DCFIFO: dual-clock FIFO (supports same port widths for input and output data)

• DCFIFO_MIXED_WIDTHS: dual-clock FIFO (supports different port widths for input

and output data)

Note: The term “DCFIFO” refers to both the DCFIFO and DCFIFO_MIXED_WIDTHS functions,

unless specified.

Related Information

• Introduction to Intel FPGA IP Cores

Provides general information about all Intel FPGA IP cores, including

parameterizing, generating, upgrading, and simulating IP cores.

• Creating Version-Independent IP and Platform Designer Simulation Scripts

Creates simulation scripts that do not require manual updates for software or

IP version upgrades.

• Project Management Best Practices

Guidelines for efficient management and portability of your project and IP files.

• FIFO Intel FPGA IP User Guide Archives on page 32

Provides a list of user guides for previous versions of the FIFO Intel FPGA IP

core.

Configuration Methods

Table 1. Configuration Methods

You can configure and build the FIFO Intel FPGA IP core with methods shown in the following table.

Method

Description

Using the FIFO parameter editor. Intel recommends using this method to build your FIFO

Intel FPGA IP core. It is an efficient way to configure and

build the FIFO Intel FPGA IP core. The FIFO parameter

editor provides options that you can easily use to configure

the FIFO Intel FPGA IP core.

continued...

UG-MFNALT_FIFO | 2020.12.14

Send Feedback

Intel Corporation. All rights reserved. Agilex, Altera, Arria, Cyclone, Enpirion, Intel, the Intel logo, MAX, Nios,

Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or

other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in

accordance with Intel's standard warranty, but reserves the right to make changes to any products and services

at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any

information, product, or service described herein except as expressly agreed to in writing by Intel. Intel

customers are advised to obtain the latest version of device specifications before relying on any published

information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Method Description

You can access the FIFO Intel FPGA IP core parameter

editor in Basic Functions ➤ On Chip Memory ➤ FIFO of

the IP catalog.

(1)

Manually instantiating the FIFO Intel FPGA IP core. Use this method only if you are an expert user. This method

requires that you know the detailed specifications of the IP

core. You must ensure that the input and output ports used,

and the parameter values assigned are valid for the FIFO

Intel FPGA IP core you instantiate for your target device.

Related Information

Introduction to Intel FPGA IP Cores

Provides general information about the Intel Quartus

®

Prime Parameter Editor

Specifications

Verilog HDL Prototype

You can locate the Verilog HDL prototype in the Verilog Design File (.v) altera_mf.v

in the <Intel Quartus

®

Prime installation directory>\eda\sim_lib

directory.

VHDL Component Declaration

The VHDL component declaration is located in the <Intel Quartus Prime

installation directory>\libraries\vhdl\altera_mf

\altera_mf_components.vhd

VHDL LIBRARY-USE Declaration

The VHDL LIBRARY-USE declaration is not required if you use the VHDL Component

Declaration.

LIBRARY altera_mf;

USE altera_mf.altera_mf_components.all;

FIFO Signals

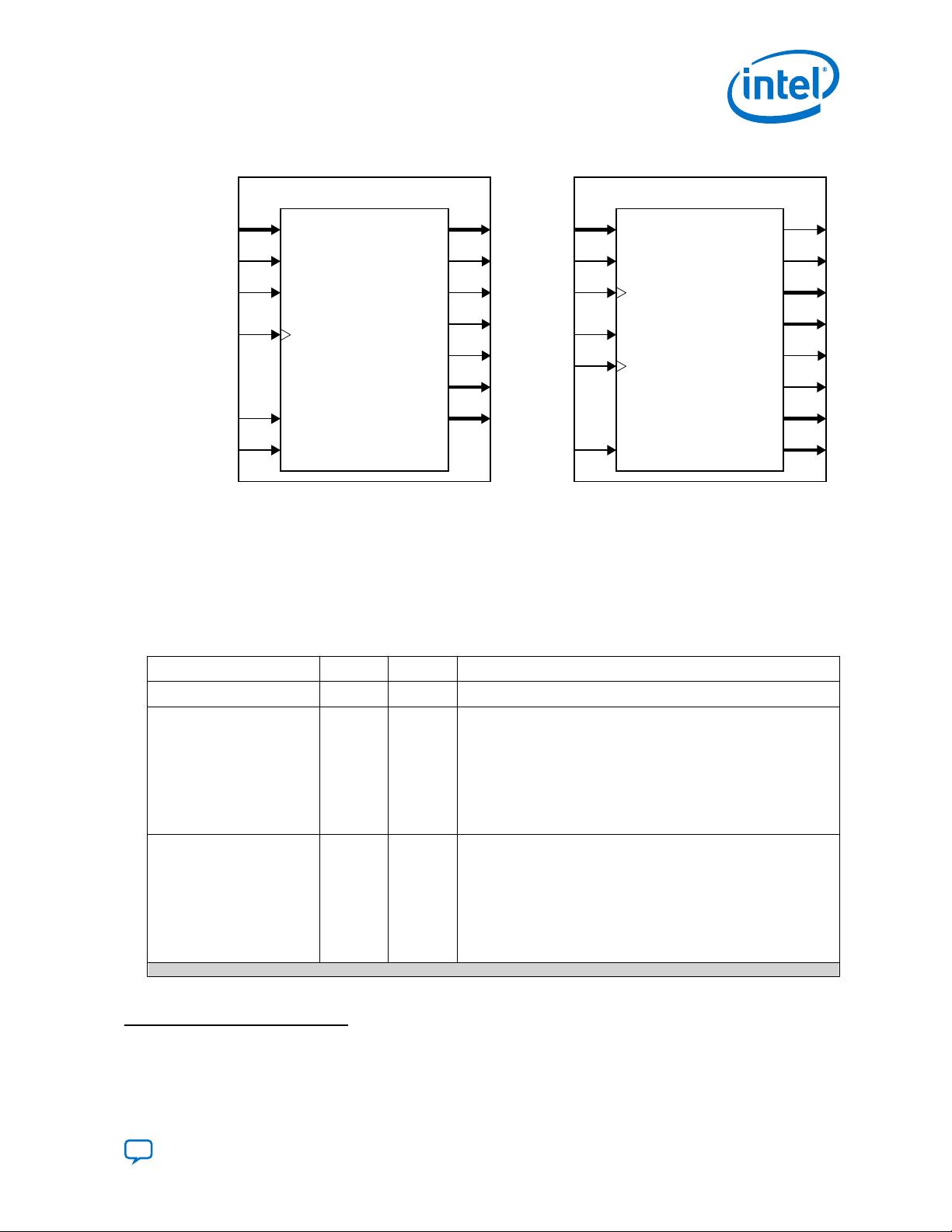

This section provides diagrams of the SCFIFO and DCFIFO blocks of the FIFO Intel

FPGA IP core to help in visualizing their input and output ports. This section also

describes each port in detail to help in understanding their usages, functionality, or

any restrictions. For better illustrations, some descriptions might refer you to a specific

section in this user guide.

(1)

Do not use dcfifo or scfifo as the entity name for your FIFO Platform Designer system.

FIFO Intel

®

FPGA IP User Guide

UG-MFNALT_FIFO | 2020.12.14

FIFO Intel

®

FPGA IP User Guide

Send Feedback

4

Figure 1. SCFIFO and DCFIFO Input and Output Signals

SCFIFO

data[7..0]

wrreq

rdreq

sclr

aclr

clock

almost_full

almost_empty

usedw[7..0]

empty

full

q[7..0]

DCFIFO

data[7..0]

wrreq

rdreq

wrempty

aclr

rdempty

rdusedw[8..0]

wrclk

wrusedw[8..0]

q[7..0]

rdfull

wrfull

rdclk

eccstatus[1:0]

eccstatus[1:0]

For the SCFIFO block, the read and write signals are synchronized to the same clock;

for the DCFIFO block, the read and write signals are synchronized to the rdclk and

wrclk clocks respectively. The prefixes wr and rd represent the signals that are

synchronized by the wrclk and rdclk clocks respectively.

Table 2. Input and Output Ports Description

This table lists the signals of the FIFO Intel FPGA IP core. The term “series” refers to all the device families of a

particular device. For example, “Stratix

®

series” refers to the Stratix IV and Stratix V, unless specified

otherwise.

Port

Type Required Description

clock

(2)

Input Yes Positive-edge-triggered clock.

wrclk

(3)

Input Yes Positive-edge-triggered clock.

Use to synchronize the following ports:

•

data

•

wrreq

•

wrfull

•

wrempty

•

wrusedw

rdclk

(3)

Input Yes Positive-edge-triggered clock.

Use to synchronize the following ports:

•

q

•

rdreq

•

rdfull

•

rdempty

•

rdusedw

continued...

(2)

Only applicable for the SCFIFO function.

(3)

Applicable for both of the DCFIFO functions.

FIFO Intel

®

FPGA IP User Guide

UG-MFNALT_FIFO | 2020.12.14

Send Feedback

FIFO Intel

®

FPGA IP User Guide

5

评论0