没有合适的资源?快使用搜索试试~ 我知道了~

数字集成电路使用Verilog HDL编写数字跑表程序

资源推荐

资源详情

资源评论

物理与信息工程学院

数字集成电路设计报告

设计一: 基于

Verilog HDL

的基本数字逻辑设计

设计二: 基于

Verilog HDL

的数字跑表设计

专业: 班级:

姓名: 学号:

指导老师:

2013 年 6 月制

设计一:基于

Verilog HDL

的基本数字逻辑设计

一、 设计目的

1、 熟悉 Xilinx ISE Design Suite 12.3 软件的使用

2、 掌握 Verilog 语言的进行简单的编程

3、 学会使用 Isim 或者 Modelsim 进行功能仿真和时序仿真,并检验正确

性

二、 设计原理(包括步骤)

本次实验设计的功能每过一秒,LED 灯循环移位,由于实验板上所提供的时钟

频率为 100MHZ,所以首先需要将时钟分频,从而得到所需要的时钟频率 1HZ,

在此基础上,使用 Verilog 语言进行设计.

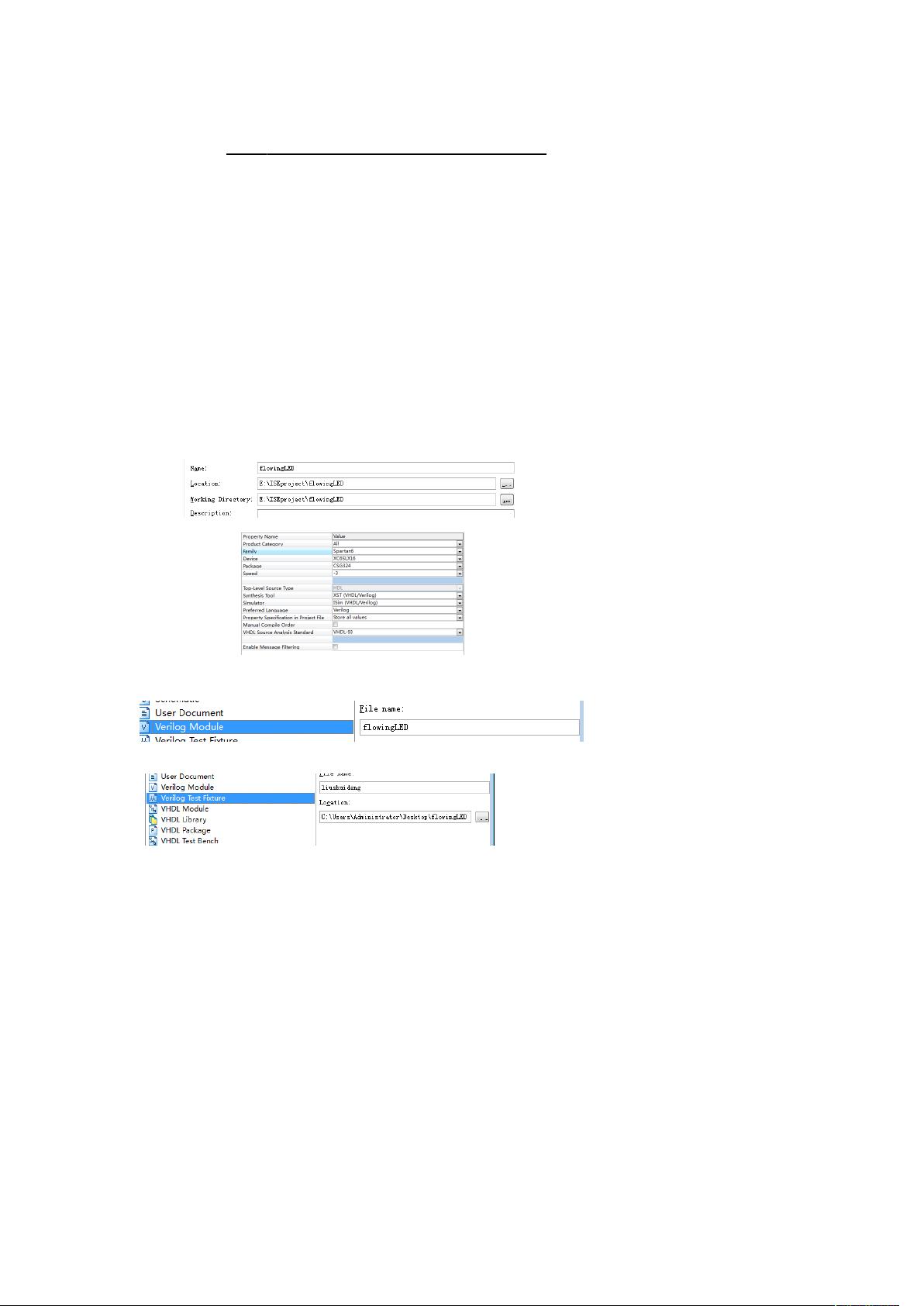

首先需要新建一个工程,点击菜单栏里面的 file 中的 new source,会弹出下面窗

口, 输入所需要建的工程名字,点击 next

,将配置改为 ,点击 next,之后点击 finish,就创建了一个

工程,然后在工程窗口右击选择 new source 添加 Verilog module,

,点击 next,就可以写设计

文件了。编写测首先测试文件时首先选择 simulation,

就可以写仿真文件了。

三、 设计成果

1、模块划分

1、设计模块

2、仿真模块

2、模块设计

1、设计程序

module flowingLED(

input clk,

input reset,

output reg[7:0] led

);

reg [26:0]counter;

reg flag;//计数器

always @(posedge clk or posedge reset)

begin

if(reset)

begin

counter <= 0;

flag<=0;//归零

end

else if(counter == 27'h1000)

begin

counter <= 0;

flag<=1;

end

else

begin

counter <= counter + 27'h1;//循环计数

flag<=0;

end

end

always @(posedge clk or posedge reset)

begin

if(reset)

led <= 8'b00000001;//置初值

else if(flag==1)

begin

led <= {led[0],led[7:1]};//实现循环移位。。

end

end

endmodule

2、仿真程序

module liushuideng;

reg clk;

reg reset;

wire [7:0] led;

flowingLED uut (

.clk(clk),

.reset(reset),

.led(led)

);

剩余10页未读,继续阅读

资源评论

昭晖君2021-06-04打不开这个

昭晖君2021-06-04打不开这个

blackrose_0726

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功