Zynq-7000 EPP

Packaging and Pinout

Advance Product Specification

UG865 (v1.0) May 8, 2012

Zynq-7000 EPP Packaging Guide www.xilinx.com 2

UG865 (v1.0) May 8, 2012

Notice of Disclaimer

The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES

AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY,

NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including

negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with,

the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage

(including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such

damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct

any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce,

modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions

of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm

; IP cores may be subject to warranty and support

terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application

requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps

.

Automotive Applications Disclaimer

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE

PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A

FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE

REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL

INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

This document contains advance information and is subject to change without notice.

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included

herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

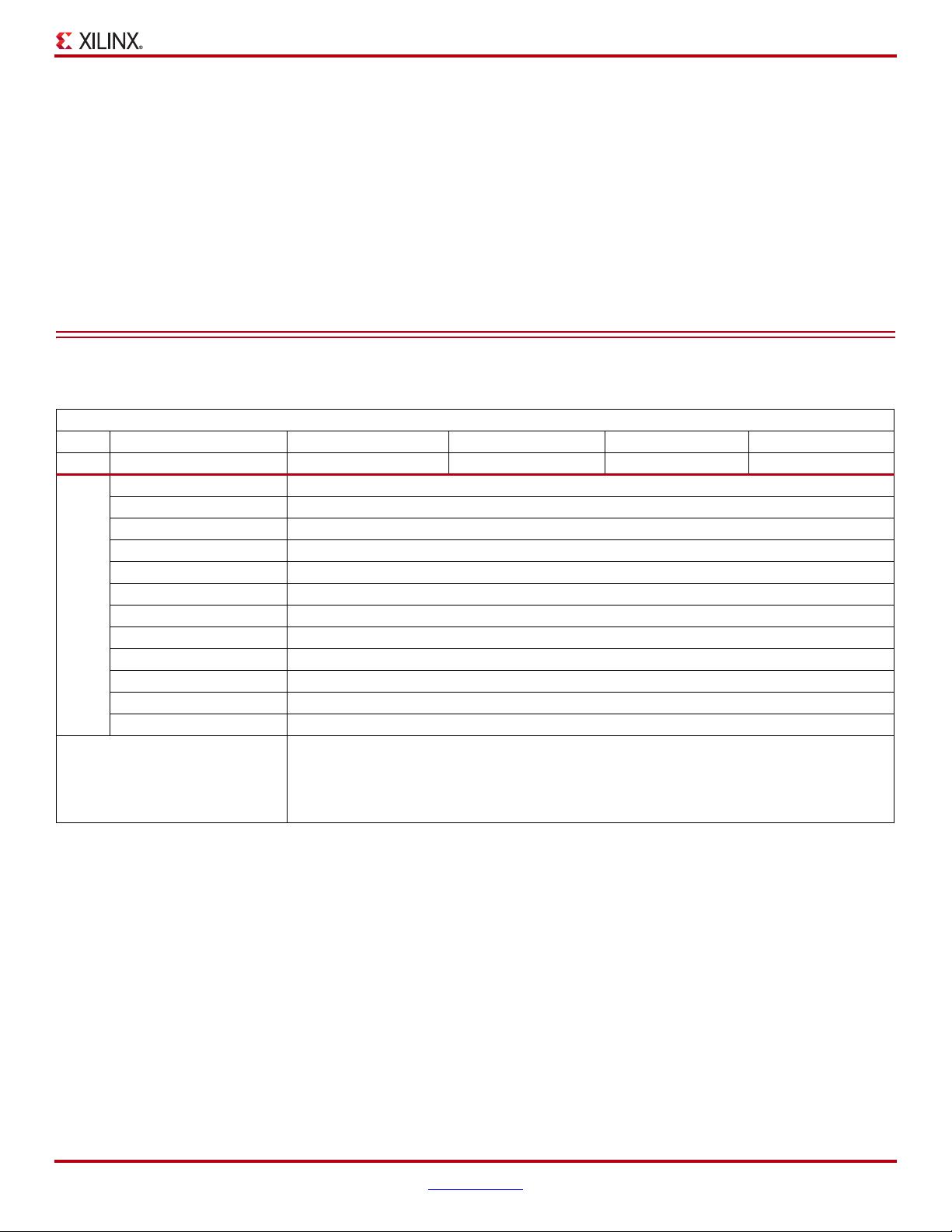

Revision History

The following table shows the revision history for this document.

Date Version Revision

05/08/12 1.0

Initial Xilinx release.

Zynq-7000 EPP Packaging Guide www.xilinx.com 3

UG865 (v1.0) May 8, 2012

Table of Contents

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Chapter 1: Package Overview

Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

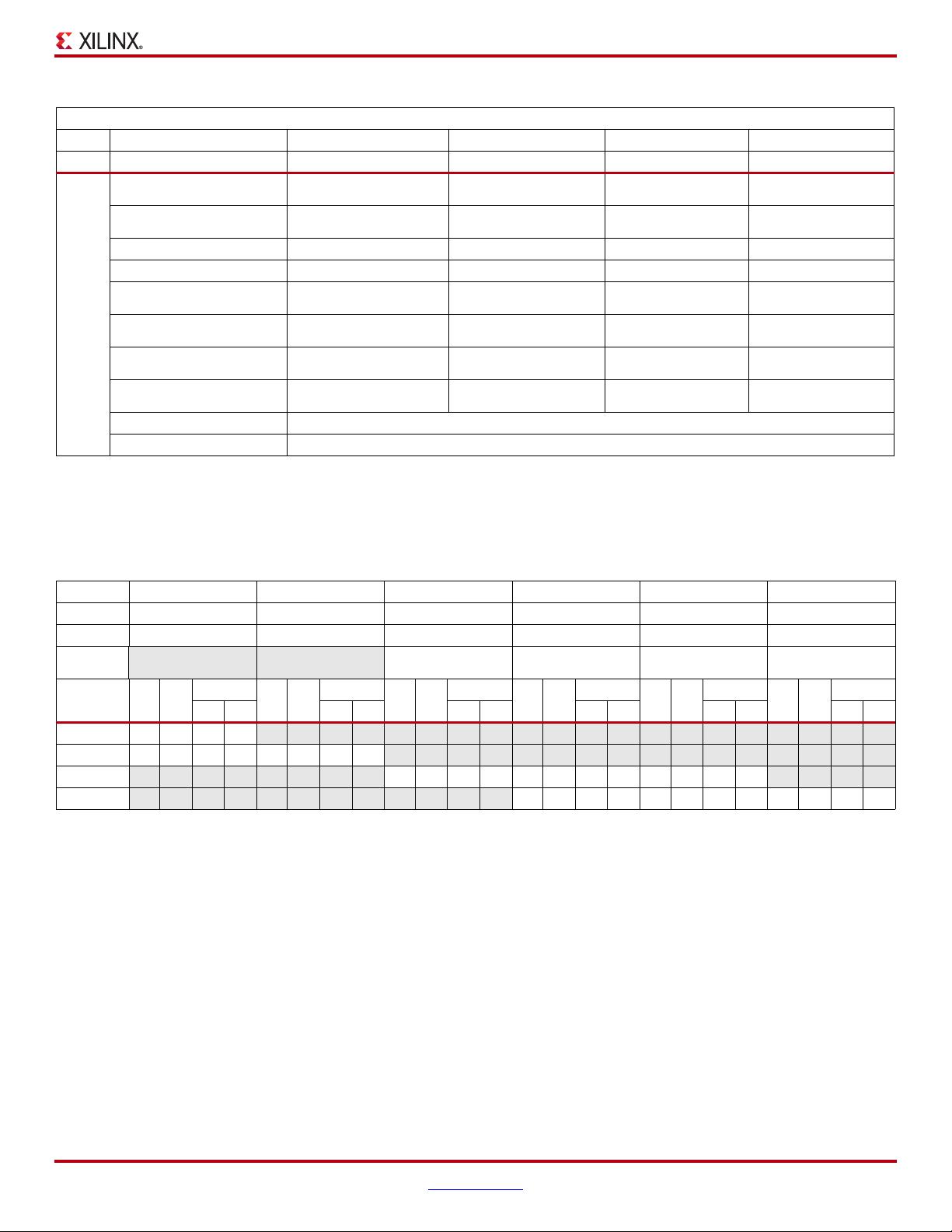

Device/Package Combinations and Maximum I/Os . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Pin Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Pin Compatibility Between Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

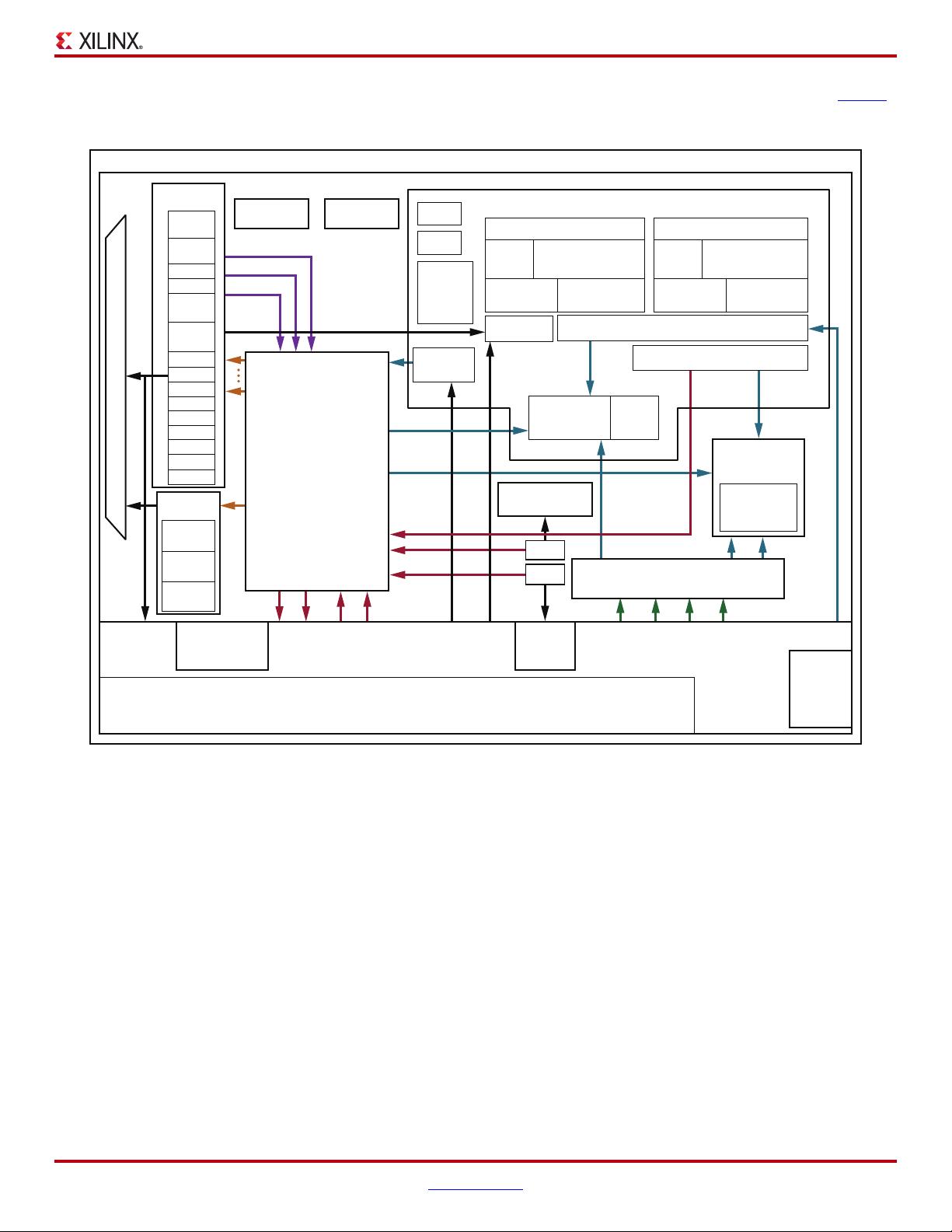

Die Level Bank Numbering Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Chapter 2: Zynq-7000 EPP Package Files

About ASCII Package Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

ASCII Pinout Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Chapter 3: Device Diagrams

Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Zynq-7000 EPP Device Diagrams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Chapter 4: Mechanical Drawings

Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

CLG400 Wire-Bond Chip-Scale BGA (XC7Z010 and XC7Z020)(0.8 mm Pitch) . . . . . . . . . . . . . . . . . . 49

CLG484 Wire-Bond Chip-Scale BGA (XC7Z020)

(0.8 mm Pitch) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Chapter 5: Thermal Specifications

Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Thermal Management Strategy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Some Thermal Management Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Support for Compact Thermal Models (CTM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Soldering Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

References for Chapter 5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Zynq-7000 EPP Packaging Guide www.xilinx.com 4

UG865 (v1.0) May 8, 2012

Chapter 6: Package Marking

Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Appendix A: Recommended PCB Design Rules

BGA Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Appendix B: Heat Sink Guidelines for Lidless Flip-Chip Packages

Heat Sink Attachments for Lidless FCBGA (FB/FBG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Types of Heat Sink Attachments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Reasons for Thermal Interface Material. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Thermal Material Handling Guidelines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Appendix C: Additional Resources

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Solution Centers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Zynq-7000 EPP Packaging Guide www.xilinx.com 5

UG865 (v1.0) May 8, 2012

Chapter 1

Package Overview

Summary

This chapter covers the following topics:

• Introduction

• Device/Package Combinations and Maximum I/Os

• Pin Definitions

• Pin Compatibility Between Packages

• Die Level Bank Numbering Overview

Introduction

This section describes the pinouts for the Zynq™-7000 Extensible Processing Platform (EPP)

available in 0.8 mm pitch wire bond and various 1.0 mm pitch flip-chip and fine-pitch BGA

packages.

Package inductance is minimized as a result of optimal placement and even distribution as

well as an optimal number of Power and GND pins.

All packages are available as Pb-free (additional G in package name) with selected packages

including a Pb-only option.

All of the Zynq-7000 EPP devices supported in a particular package are pinout compatible.

Pins that are not available in a device but are not available in smaller device with a

compatible package are listed as “No Connects”.

The Zynq-7000 EPP contains a large number of fixed and flexible I/O. The Zynq-7000 EPP

has a constant 130 pins dedicated to memory interfaces (DDR I/O), multiplexed peripherals

(MIO), and control. Programmable logic provides additional pins for SelectIO™ resources

(SIO) and multi-gigabit serial transceivers (GTX) that scale by device as well as f ixed pins for

configuration and analog-to-digital conversion (XADC). SIO can be used to extend the MIO

to further leverage the fixed peripherals of the processing system (PS).

- 1

- 2

- 3

- 4

- 5

- 6

前往页