TMS320C6414, TMS320C6415, TMS320C6416

FIXED-POINT DIGITAL SIGNAL PROCESSORS

SPRS146N − FEBRUARY 2001 − REVISED MAY 2005

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443

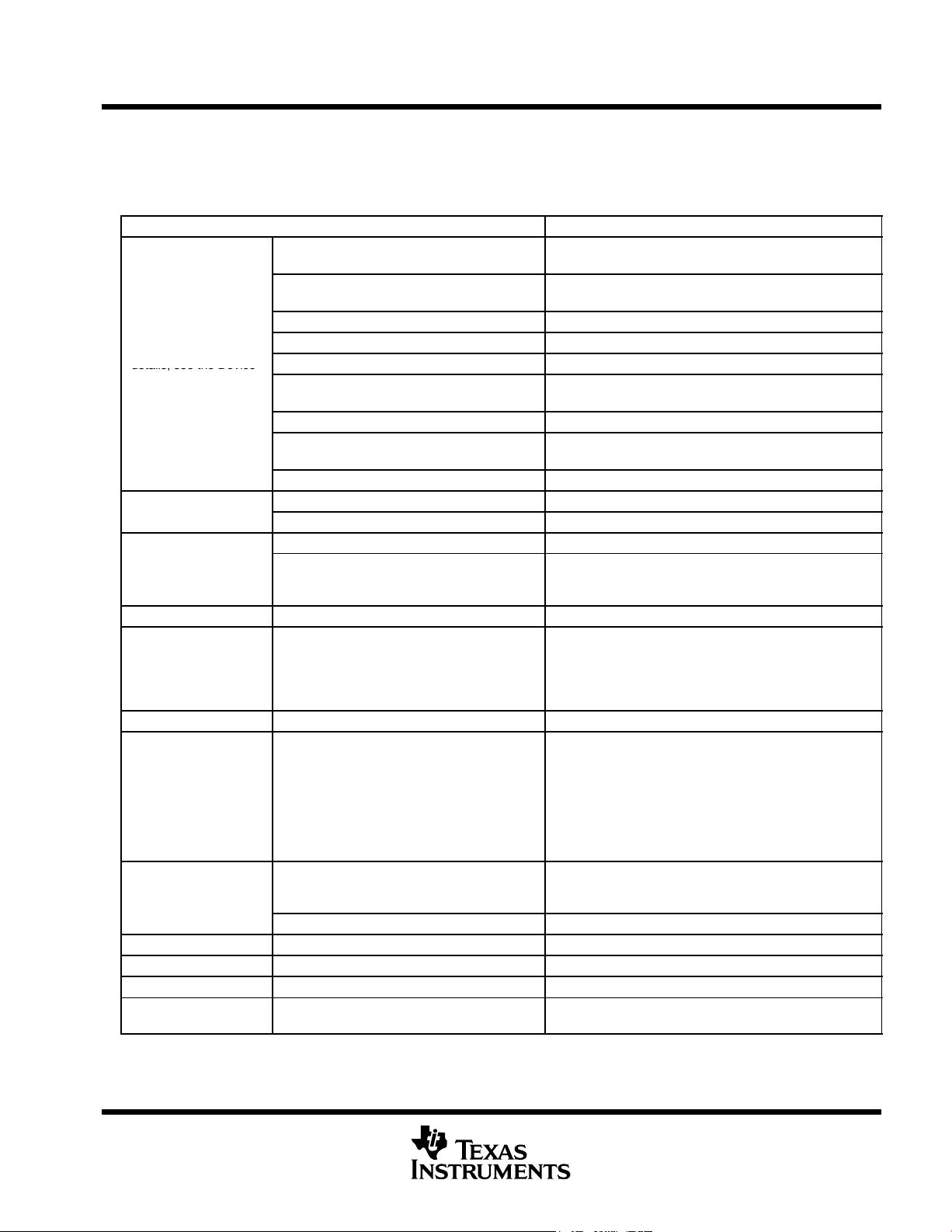

Highest-Performance Fixed-Point Digital

Signal Processors (DSPs)

− 2-, 1.67-, 1.39-ns Instruction Cycle Time

− 500-, 600-, 720-MHz Clock Rate

− Eight 32-Bit Instructions/Cycle

− Twenty-Eight Operations/Cycle

− 4000, 4800, 5760 MIPS

− Fully Software-Compatible With C62x™

− C6414/15/16 Devices Pin-Compatible

VelociTI.2™ Extensions to VelociTI™

Advanced Very-Long-Instruction-Word

(VLIW) TMS320C64x™ DSP Core

− Eight Highly Independent Functional

Units With VelociTI.2™ Extensions:

− Six ALUs (32-/40-Bit), Each Supports

Single 32-Bit, Dual 16-Bit, or Quad

8-Bit Arithmetic per Clock Cycle

− Two Multipliers Support

Four 16 x 16-Bit Multiplies

(32-Bit Results) per Clock Cycle or

Eight 8 x 8-Bit Multiplies

(16-Bit Results) per Clock Cycle

− Non-Aligned Load-Store Architecture

− 64 32-Bit General-Purpose Registers

− Instruction Packing Reduces Code Size

− All Instructions Conditional

Instruction Set Features

− Byte-Addressable (8-/16-/32-/64-Bit Data)

− 8-Bit Overflow Protection

− Bit-Field Extract, Set, Clear

− Normalization, Saturation, Bit-Counting

− VelociTI.2™ Increased Orthogonality

Viterbi Decoder Coprocessor (VCP) [C6416]

− Supports Over 600 7.95-Kbps AMR

− Programmable Code Parameters

Turbo Decoder Coprocessor (TCP) [C6416]

− Supports up to 7 2-Mbps or

43 384-Kbps 3GPP (6 Iterations)

− Programmable Turbo Code and

Decoding Parameters

L1/L2 Memory Architecture

− 128K-Bit (16K-Byte) L1P Program Cache

(Direct Mapped)

− 128K-Bit (16K-Byte) L1D Data Cache

(2-Way Set-Associative)

− 8M-Bit (1024K-Byte) L2 Unified Mapped

RAM/Cache (Flexible Allocation)

Two External Memory Interfaces (EMIFs)

− One 64-Bit (EMIFA), One 16-Bit (EMIFB)

− Glueless Interface to Asynchronous

Memories (SRAM and EPROM) and

Synchronous Memories (SDRAM,

SBSRAM, ZBT SRAM, and FIFO)

− 1280M-Byte Total Addressable External

Memory Space

Enhanced Direct-Memory-Access (EDMA)

Controller (64 Independent Channels)

Host-Port Interface (HPI)

− User-Configurable Bus Width (32-/16-Bit)

32-Bit/33-MHz, 3.3-V PCI Master/Slave

Interface Conforms to PCI Specification 2.2

[C6415/C6416 ]

− Three PCI Bus Address Registers:

Prefetchable Memory

Non-Prefetchable Memory I/O

− Four-Wire Serial EEPROM Interface

− PCI Interrupt Request Under DSP

Program Control

− DSP Interrupt Via PCI I/O Cycle

Three Multichannel Buffered Serial Ports

− Direct I/F to T1/E1, MVIP, SCSA Framers

− Up to 256 Channels Each

− ST-Bus-Switching-, AC97-Compatible

− Serial Peripheral Interface (SPI)

Compatible (Motorola™)

Three 32-Bit General-Purpose Timers

Universal Test and Operations PHY

Interface for ATM (UTOPIA) [C6415/C6416]

− UTOPIA Level 2 Slave ATM Controller

− 8-Bit Transmit and Receive Operations

up to 50 MHz per Direction

− User-Defined Cell Format up to 64 Bytes

Sixteen General-Purpose I/O (GPIO) Pins

Flexible PLL Clock Generator

IEEE-1149.1 (JTAG

†

)

Boundary-Scan-Compatible

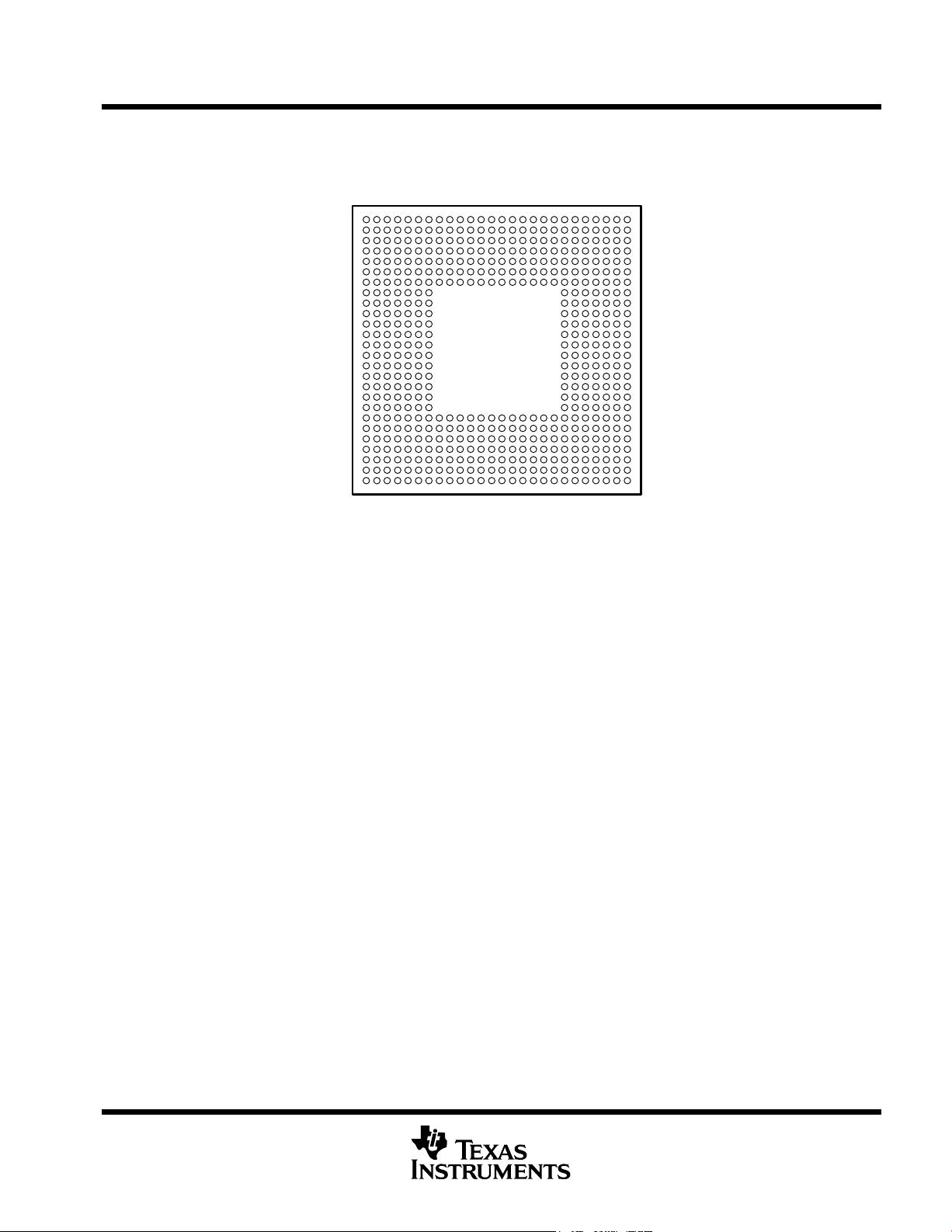

532-Pin Ball Grid Array (BGA) Package

(GLZ, ZLZ and CLZ Suffixes), 0.8-mm Ball

Pitch

0.13-µm/6-Level Cu Metal Process (CMOS)

3.3-V I/Os, 1.2-V/1.25-V Internal (500 MHz)

3.3-V I/Os, 1.4-V Internal (600 and 720 MHz)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright © 2005 Texas Instruments Incorporated

C62x, VelociTI.2, VelociTI, and TMS320C64x are trademarks of Texas Instruments.

Motorola is a trademark of Motorola, Inc.

†

IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功