利用纯硬件计算CRC-CCITT算法

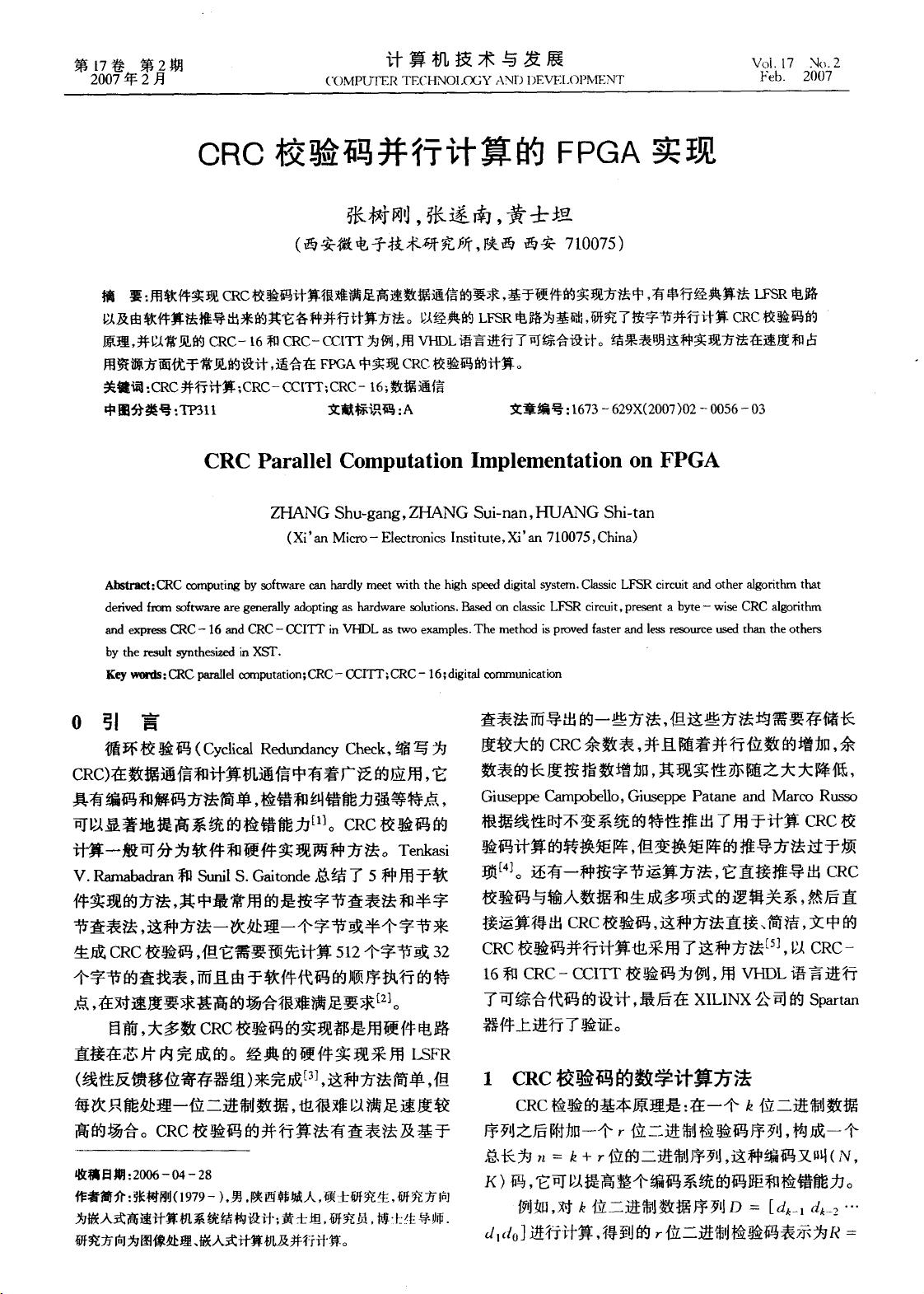

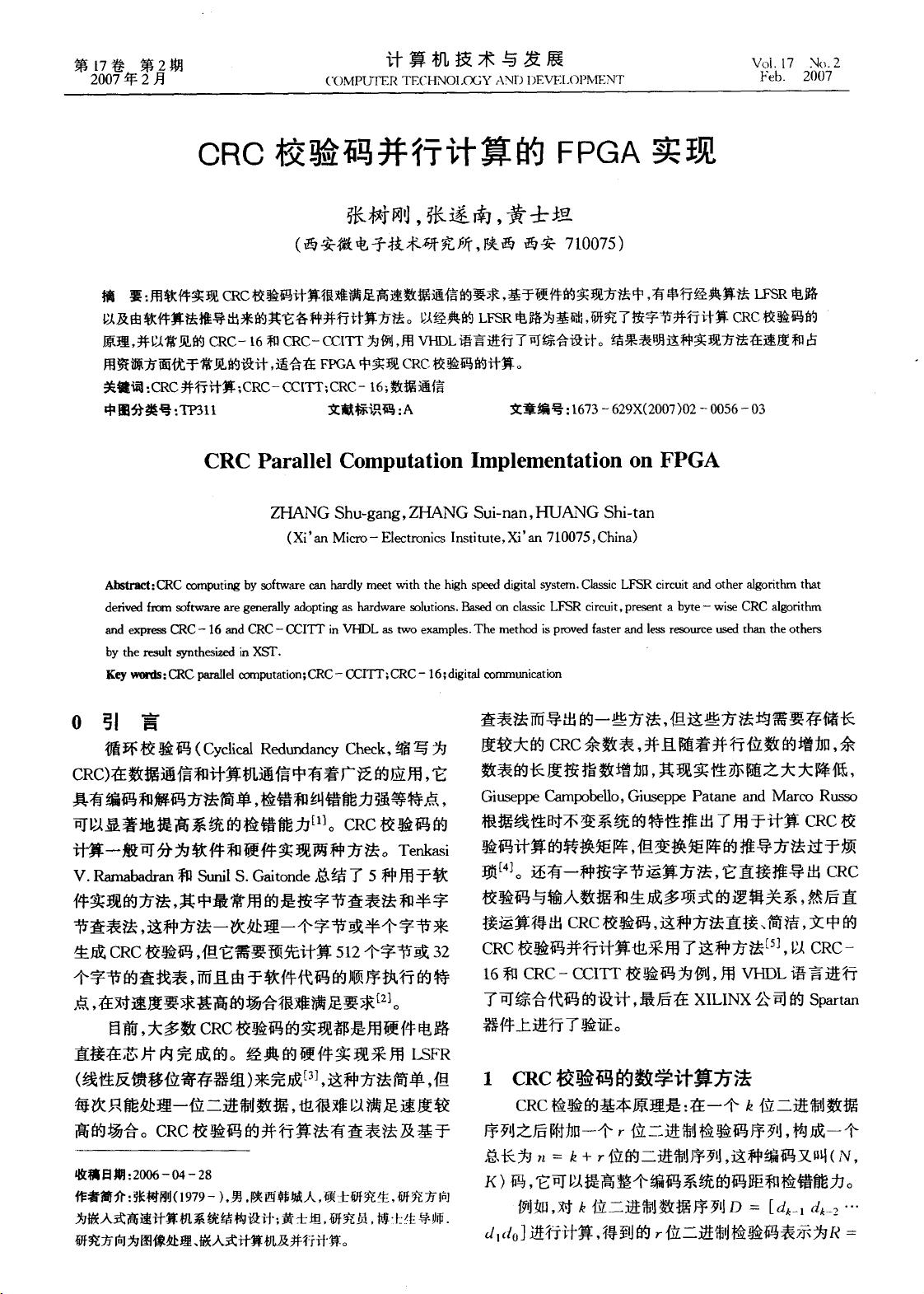

CRC(Cyclic Redundancy Check,循环冗余校验)是一种广泛用于数据传输错误检测的校验码技术,尤其在通信、存储和计算机网络等领域。CRC-CCITT,也称为XModem或Kermit CRC,是CRC算法的一个具体实例,它使用16位的校验码,具有较高的检错能力。本项目主要关注如何利用硬件,特别是FPGA(Field-Programmable Gate Array)来实现CRC-CCITT算法。 在FPGA/CPLD(Complex Programmable Logic Device)设计中,Verilog HDL(Hardware Description Language,硬件描述语言)是一种常用的语言,它允许开发者用类似于编程的方式描述数字系统的逻辑行为。在这个项目中,Verilog HDL被用来实现CRC-CCITT的硬件逻辑。 CRC计算的核心是基于一个特定的生成多项式。CRC-CCITT通常使用16位的生成多项式G(x) = x^16 + x^12 + x^5 + 1,这个多项式在二进制表示下为1100001000100001。在Verilog HDL代码中,会定义这个多项式,并用它来计算输入数据的CRC值。 在描述CRC计算的Verilog模块中,关键部分包括移位寄存器和异或门。当新的8位数据输入到硬件接口时,这些数据会被加载到移位寄存器中,并与生成多项式进行异或操作。每次接收到一个新的数据脉冲,移位寄存器中的数据会左移一位,最右侧的空位由生成多项式的最高位填充。这个过程会持续16次,对应生成多项式的位宽。移位寄存器的当前状态就是CRC-CCITT校验码。 为了连续处理多个字节数据,Verilog设计通常会包含一个状态机。状态机控制着数据的接收、移位和计算过程,确保在正确的时间对每个字节执行正确的操作。例如,它可以有“等待数据”、“接收数据”、“计算CRC”和“准备接收新数据”等状态。 在Quartus软件中,这个Verilog设计会经过综合和布局布线步骤,最终生成适配特定FPGA芯片的配置文件。用户可以通过Quartus的仿真工具对设计进行验证,确保其在不同输入数据条件下正确计算CRC值。完成验证后,配置文件可以下载到FPGA中,实现硬件级别的CRC计算,提供高效且实时的错误检测能力。 这个项目展示了如何利用Verilog HDL在FPGA上实现CRC-CCITT算法,通过硬件加速提高数据校验的速度和效率。这样的实现对于需要快速错误检测的系统,如高速通信链路或者嵌入式系统,具有显著的价值。文件名"FPGA_CRC"可能包含的就是这个完整的Verilog设计工程,包括源代码、编译脚本、测试平台和其他相关文档,用于指导用户理解和复现这个CRC硬件模块。

利用纯硬件计算CRC-CCITT算法 (161个子文件)

利用纯硬件计算CRC-CCITT算法 (161个子文件)  _info 2KB

_info 2KB _info 569B

_info 569B _info 521B

_info 521B _vmake 26B

_vmake 26B _vmake 26B

_vmake 26B _vmake 26B

_vmake 26B CCITT.root_partition.cmp.ammdb 357B

CCITT.root_partition.cmp.ammdb 357B CCITT.vpr.ammdb 317B

CCITT.vpr.ammdb 317B CCITT.map.ammdb 123B

CCITT.map.ammdb 123B CCITT.v.bak 1KB

CCITT.v.bak 1KB CCITT_run_msim_rtl_verilog.do.bak 235B

CCITT_run_msim_rtl_verilog.do.bak 235B CCITT_run_msim_rtl_verilog.do.bak1 235B

CCITT_run_msim_rtl_verilog.do.bak1 235B CCITT_run_msim_rtl_verilog.do.bak10 235B

CCITT_run_msim_rtl_verilog.do.bak10 235B CCITT_run_msim_rtl_verilog.do.bak11 617B

CCITT_run_msim_rtl_verilog.do.bak11 617B CCITT_run_msim_rtl_verilog.do.bak2 235B

CCITT_run_msim_rtl_verilog.do.bak2 235B CCITT_run_msim_rtl_verilog.do.bak3 235B

CCITT_run_msim_rtl_verilog.do.bak3 235B CCITT_run_msim_rtl_verilog.do.bak4 235B

CCITT_run_msim_rtl_verilog.do.bak4 235B CCITT_run_msim_rtl_verilog.do.bak5 235B

CCITT_run_msim_rtl_verilog.do.bak5 235B CCITT_run_msim_rtl_verilog.do.bak6 235B

CCITT_run_msim_rtl_verilog.do.bak6 235B CCITT_run_msim_rtl_verilog.do.bak7 313B

CCITT_run_msim_rtl_verilog.do.bak7 313B CCITT_run_msim_rtl_verilog.do.bak8 313B

CCITT_run_msim_rtl_verilog.do.bak8 313B CCITT_run_msim_rtl_verilog.do.bak9 235B

CCITT_run_msim_rtl_verilog.do.bak9 235B CCITT.cmp.cdb 7KB

CCITT.cmp.cdb 7KB CCITT.root_partition.cmp.cdb 5KB

CCITT.root_partition.cmp.cdb 5KB CCITT.root_partition.map.cdb 4KB

CCITT.root_partition.map.cdb 4KB CCITT.map.cdb 3KB

CCITT.map.cdb 3KB CCITT.sgdiff.cdb 3KB

CCITT.sgdiff.cdb 3KB CCITT.(0).cnf.cdb 2KB

CCITT.(0).cnf.cdb 2KB CCITT.rtlv_sg.cdb 2KB

CCITT.rtlv_sg.cdb 2KB CCITT.root_partition.map.hbdb.cdb 1KB

CCITT.root_partition.map.hbdb.cdb 1KB CCITT.root_partition.map.reg_db.cdb 195B

CCITT.root_partition.map.reg_db.cdb 195B CCITT.rtlv_sg_swap.cdb 181B

CCITT.rtlv_sg_swap.cdb 181B _primary.dat 24KB

_primary.dat 24KB _primary.dat 7KB

_primary.dat 7KB _primary.dat 3KB

_primary.dat 3KB logic_util_heursitic.dat 2KB

logic_util_heursitic.dat 2KB _primary.dat 1KB

_primary.dat 1KB _primary.dat 1KB

_primary.dat 1KB _primary.dat 559B

_primary.dat 559B CCITT.db_info 140B

CCITT.db_info 140B CCITT.db_info 140B

CCITT.db_info 140B _primary.dbs 26KB

_primary.dbs 26KB _primary.dbs 4KB

_primary.dbs 4KB _primary.dbs 3KB

_primary.dbs 3KB _primary.dbs 1KB

_primary.dbs 1KB _primary.dbs 1KB

_primary.dbs 1KB _primary.dbs 704B

_primary.dbs 704B CCITT.cmp2.ddb 42KB

CCITT.cmp2.ddb 42KB CCITT.cmp0.ddb 24KB

CCITT.cmp0.ddb 24KB CCITT.asm_labs.ddb 1KB

CCITT.asm_labs.ddb 1KB CCITT.pti_db_list.ddb 177B

CCITT.pti_db_list.ddb 177B CCITT.tis_db_list.ddb 177B

CCITT.tis_db_list.ddb 177B CCITT.root_partition.cmp.dfp 33B

CCITT.root_partition.cmp.dfp 33B Waveform.vwf.do 1KB

Waveform.vwf.do 1KB wave.do 752B

wave.do 752B CCITT_run_msim_rtl_verilog.do 617B

CCITT_run_msim_rtl_verilog.do 617B CCITT_run_msim_gate_verilog.do 170B

CCITT_run_msim_gate_verilog.do 170B CRC的串行及并行实现原理.doc 73KB

CRC的串行及并行实现原理.doc 73KB CCITT.done 26B

CCITT.done 26B CCITT.root_partition.map.dpi 689B

CCITT.root_partition.map.dpi 689B CRC_Calc+v0.1.exe 1012KB

CRC_Calc+v0.1.exe 1012KB CCITT.root_partition.map.hbdb.hb_info 46B

CCITT.root_partition.map.hbdb.hb_info 46B CCITT.cmp.hdb 10KB

CCITT.cmp.hdb 10KB CCITT.root_partition.cmp.hdb 10KB

CCITT.root_partition.cmp.hdb 10KB CCITT.sgdiff.hdb 10KB

CCITT.sgdiff.hdb 10KB CCITT.pre_map.hdb 10KB

CCITT.pre_map.hdb 10KB CCITT.rtlv.hdb 10KB

CCITT.rtlv.hdb 10KB CCITT.map.hdb 10KB

CCITT.map.hdb 10KB CCITT.root_partition.map.hdb 10KB

CCITT.root_partition.map.hdb 10KB CCITT.root_partition.map.hbdb.hdb 10KB

CCITT.root_partition.map.hbdb.hdb 10KB CCITT.(0).cnf.hdb 1005B

CCITT.(0).cnf.hdb 1005B CCITT.hier_info 2KB

CCITT.hier_info 2KB CCITT.hif 422B

CCITT.hif 422B CCITT.lpc.html 372B

CCITT.lpc.html 372B CCITT.cmp.idb 2KB

CCITT.cmp.idb 2KB modelsim.ini 11KB

modelsim.ini 11KB CCITT.ipinfo 163B

CCITT.ipinfo 163B CCITT.jdi 224B

CCITT.jdi 224B CCITT.map.kpt 1024B

CCITT.map.kpt 1024B CCITT.root_partition.map.kpt 637B

CCITT.root_partition.map.kpt 637B CCITT.cmp_merge.kpt 209B

CCITT.cmp_merge.kpt 209B CCITT.root_partition.cmp.kpt 205B

CCITT.root_partition.cmp.kpt 205B CCITT.cmp.kpt 204B

CCITT.cmp.kpt 204B CCITT.cmp.logdb 4B

CCITT.cmp.logdb 4B CCITT.map.logdb 4B

CCITT.map.logdb 4B CCITT.root_partition.cmp.logdb 4B

CCITT.root_partition.cmp.logdb 4B CRC.mpf 14KB

CRC.mpf 14KB msim_transcript 2KB

msim_transcript 2KB CRC.cr.mti 2B

CRC.cr.mti 2B CRC校验码并行计算的FPGA实现.PDF 232KB

CRC校验码并行计算的FPGA实现.PDF 232KB CCITT.pin 15KB

CCITT.pin 15KB CCITT.pof 15KB

CCITT.pof 15KB verilog.prw 3KB

verilog.prw 3KB verilog.prw 2KB

verilog.prw 2KB verilog.prw 1KB

verilog.prw 1KB verilog.prw 691B

verilog.prw 691B verilog.prw 644B

verilog.prw 644B verilog.prw 340B

verilog.prw 340B verilog.psm 125KB

verilog.psm 125KB verilog.psm 62KB

verilog.psm 62KB- 1

- 2

- 粉丝: 0

- 资源: 8

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 数据分析-02-淘宝用户行为分析(包含代码和数据)

- (1160222)线性代数试卷

- 毕业设计基于Python+机器学习的股票预测和分析项目源码+文档说明.zip

- 机械设计TB66004A电机驱动器模型step非常好的设计图纸100%好用.zip

- (26144420)线性代数试题库11套题.doc

- BERNESE所需的DE405.EPH文件

- 数据分析-03-上海餐饮情况分析(包含代码和数据)

- modbust调试助手

- (179942656)JavaWeb实验二 JSP表单开发及访问数据库【源代码+注释】

- 基于pytorch的股票预测和分析项目源码+文档说明.zip

- (1729410)jsp数据库编程指南

- (14659434)数码管动态显示

- (25363252)新颖的单片机实现测温电路

- 数据分析-04-百货商场用户画像描述与价值分析(包含代码和数据)

- Python毕业设计-基于pytorch的股票预测和分析项目源码+文档说明.zip

- (2627236)学生成绩管理信息系统

信息提交成功

信息提交成功

评论0