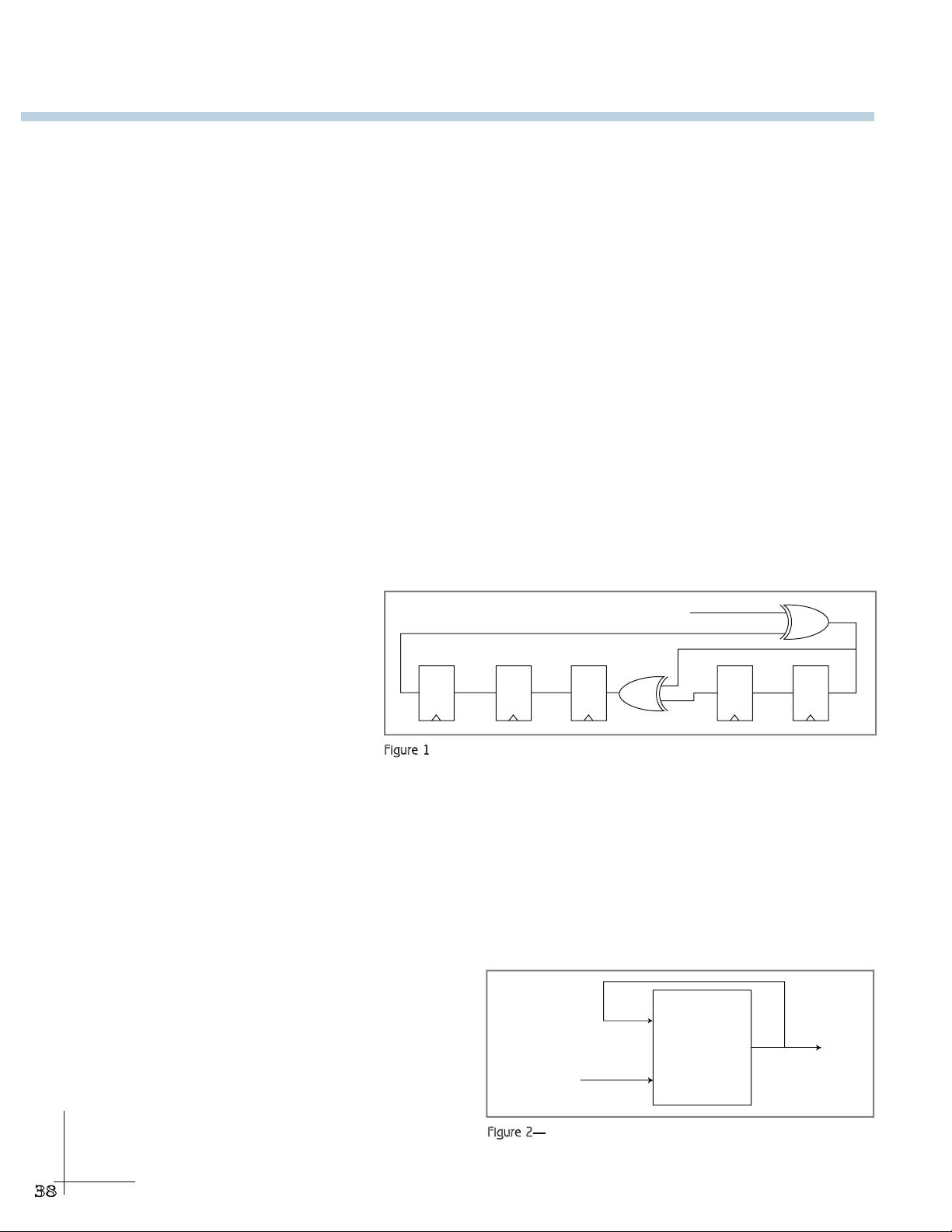

本文详细探讨了循环冗余校验(Cyclic Redundancy Check,简称CRC)电路的实现方法,尤其侧重于并行CRC生成码的Verilog或VHDL代码实现。对于电子与计算机工程师而言,CRC是一种十分常见的错误检测算法,广泛应用于现代通信协议中。虽然许多工程师熟悉CRC的基本概念,比如它作为一种用于通信协议中检测比特错误的机制,以及它是模2长除法运算的余数,但只有少数人能够充分理解CRC的工作原理,并能根据任意CRC生成多项式来构建定制的并行CRC电路。 CRC的核心是由生成多项式定义的属性,这些属性包括生成多项式的长度和系数。协议规格通常会以十六进制或多项式形式定义CRC。在深入探讨并行CRC生成方法之前,让我们先对CRC进行一番概述。 CRC是一种利用数学理论来检测数据传输或存储中可能出现的错误的算法。其基本思想是将数据视为一个大的二进制数,将这个数除以一个预定的“生成多项式”,得到的余数就是CRC校验码。在发送数据时,将这个校验码附加到数据末尾一同发送。接收方在收到数据后,用同样的生成多项式去除接收到的整个数据,如果余数为零,则认为传输过程中没有错误发生。 在实际电路中,CRC通常使用线性反馈移位寄存器(Linear Feedback Shift Register,简称LFSR)来实现。LFSR由一系列触发器和异或门组成,通过适当地设计反馈逻辑,可构建一个根据特定生成多项式进行操作的CRC电路。 并行CRC的实现方法相比于串行实现,能显著提高处理速度,尤其在数据宽度较大时。Evgeni Stavinov在文章中所提的方法允许工程师快速生成适用于任意多项式和数据宽度的并行CRC代码,这为定制化硬件设计或对现有设计进行优化提供了便利。 在讲解并行CRC的生成方法之前,文章中提到了一些实用工具和常见CRC多项式的例子。尽管这些工具可以为特定的多项式自动生成代码,但了解背后的工作原理对于实现定制化电路或对现有设计进行优化尤为有益。Evgeni Stavinov强调,理解CRC的工作原理是每位实践逻辑设计工程师应该掌握的知识。 为了说明并行CRC生成电路的构建,Evgeni Stavinov以USB协议中使用的CRC5实现为例,展示了一个使用生成多项式G(x)=x^5 + x^2 + 1的LFSR电路。这个例子对于理解并行CRC电路设计的细节尤为重要,因为它展示了如何将理论转化为实际电路设计。 从教学的角度来看,本文适合初学者,尤其是那些已经熟悉CRC基础概念但尚未深入了解其实现原理的工程师。通过本文,读者不仅能学习到如何根据任意的生成多项式设计并行CRC电路,而且还能对现有设计进行优化,甚至开发自己的设计工具。 总而言之,本文提供了一种实用的方法,使得工程师可以快速生成适用于任意多项式和数据宽度的并行CRC代码。它不仅涵盖了并行CRC生成码的生成技术,还简要介绍了其他有趣的方法,并提供了关于CRC主题的更多信息。对于电子与计算机工程师来说,深入理解CRC的原理并掌握并行CRC电路的实现技术,无论是在学术研究还是在工业界,都是一项重要技能。

- 粉丝: 1

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功