没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

23页

我们将演示如何转换 PCI Express (PCIe) 5.0 的电气规范文档并生成等效的 IBIS-AMI 模型来表示重要的电气信号行为。 发射器上的关键信号行为是 3 阶前馈均衡 (FFE)。在接收器上,关键规范行为是连续时间线性均衡器 (CTLE)、决策反馈均衡器 (DFE) 和时钟数据恢复 (CDR)。 将显示从发送器参考的规范抖动到单独的发送器和接收器组件的转换。 IBIS-AMI 模型将在端到端通道仿真中设置,以演示系统级性能及其与规范假设的匹配情况。

资源推荐

资源详情

资源评论

Information Classification: General

DesignCon 2021

Specification-based IBIS-AMI

model PCIe 5.0 32GT/s

Todd Bermensolo, Keysight Technologies

todd.bermensolo@keysight.com

Adam Gregory, Samtec

adam.gregory@samtec.com

Hansel Desmond Dsilva, Achronix Semiconductor Corporation

hanseldsilva@achronix.com

Michael Mirmak, IBIS Enthusiast

michael@mirmak.com

Information Classification: General

Abstract

We will demonstrate how to convert electrical specification documents for PCI Express

(PCIe) 5.0 and generate an equivalent IBIS-AMI model to represent the significant

electrical signaling behaviors. Key signaling behaviors on transmitter is the 3-tap feed-

forward equalization (FFE). On receiver, the key specification behaviors are continuous-

time linear equalizer (CTLE), decision-feedback equalizer (DFE) and clock-data recovery

(CDR). The conversion from specification jitter referenced at transmitter to separate

transmitter & receiver components will be shown. The IBIS-AMI model will be setup in

end-to-end channel simulation to demonstrate the system-level performance and how it

matches with specification assumptions.

Author(s) Biography

Todd Bermensolo is an Application Engineer at Keysight Technologies, in their

Customer Success Acceleration service team. Prior experience at Intel Corporation in the

Enterprise Platform Signal Integrity team. He received his BS degree in EE from

University of Idaho in 1998 and his MS degree in EE from University of Illinois in 2005.

Hansel Desmond Dsilva is a Staff Signal Integrity Engineer at Achronix Semiconductor

Corporation. He received a Master of Science degree (with thesis) in Electrical

Engineering from San Diego State University in 2015 and a Bachelor of Engineering

degree in Electronics and Telecommunication Engineering from Don Bosco Institute of

Technology, Mumbai (Bombay) University in 2013. He believes in innovating through

collaboration and never shies from listening to another’s thought process in challenging

his own.

Adam Gregory is a Signal Integrity Engineer at Samtec. He is involved in modeling and

analysis of high-speed differential signaling channels. He received a BSEE and MSEE at

the University of South Carolina.

Michael Mirmak is a Platform Applications Engineer with Intel’s Data Center Group,

supporting signal integrity (SI) modeling and analysis. He has been involved with SI

since 1996. He is a past chair of the IBIS Open Forum, the organization that manages the

I/O Buffer Information Specification and the Touchstone specification.

Information Classification: General

Background

With mainstream interface specifications in the 5th generation, the challenges have never

been greater for implementing standards like PCIe 5.0 [1] at 32 GT/s. Form factors in

datacenters and high-performance computing are unchanged but supporting same

platform topologies at faster data rates demands more design complexity with smaller

margins. Translating electrical specification documents to system-level simulations is

not easy and requires combinations of models for silicon, interconnect and jitter

assessment. Behavioral modeling standards like IBIS-AMI [2] provides an interoperable

format to capture specification assumptions for silicon that allows platform developers to

get a first look at their system-level simulations before silicon vendor IP models are

available, or to compare those silicon vendor IP models to electrical specifications.

Utilizing IBIS-AMI model format to support a top-down, behavioral design

methodology, the static electrical specification documents can be converted to executable

behavioral models for end-to-end system level simulation. First, the hundreds of pages in

electrical specification will be narrowed down to the relevant material for IBIS-AMI

modeling. Next, the key transmitter (Tx), receiver (Rx) and jitter components will be

captured. For Tx in PCIe 5.0, there is the 3-tap feed-forward equalizer (FFE). For Rx in

PCIe 5.0, there are continuous-time linear equalizer (CTLE), decision-feedback equalizer

(DFE) and clock-data recovery (CDR). To optimize the Rx equalization, the system

pulse response is used to minimize post-cursor ISI strength to near zero value (while

staying positive). PCIe 5.0 jitter referenced at Tx, which will be separated into Tx & Rx

components to support IBIS-AMI simulation analysis flow.

The result will be Tx & Rx IBIS-AMI models that can support low bit error ratio (BER)

simulation analysis. Equalization values and channel conditions are varied to show

performance vs. specification limits. The results are a simulation-based approach to

utilize electrical specification details. Insights can be gained in platform-level simulation

results before vendor-based models are available.

PCIe 5.0 Specification Overview

PCI Express a high performance, general purpose I/O interconnect. The 5

th

generation,

or PCIe 5.0, operates at a signal transfer rate of 32 GT/s. To support backward

compatibility, it shares many similarities to with prior generations like same connector

pinout, Tx EQ presets, Tx Voltage and Jitter parameters and same approach to Tx and Rx

testing. Some key updates moving to PCIe 5.0 are updated Rx characteristics to support

32 GT/s such as CTLE frequency tables, 3-tap DFE and CDR frequency behavior. The

informative insertion loss budget is -36 dB at 16 GHz.

Overview of simulation with IBIS-AMI

The IBIS standard was first released in 1993 through the IBIS Open Forum. The core

functionality focused on analog electrical modeling of Tx, Rx and packages. With IBIS

Version 5.0 in 2008, the algorithmic modeling interface (AMI) support was added which

expanded the modeling capability to include discrete time processing behaviors or

Information Classification: General

algorithmic modeling. Examples of types of AMI modeling are transmitter equalization,

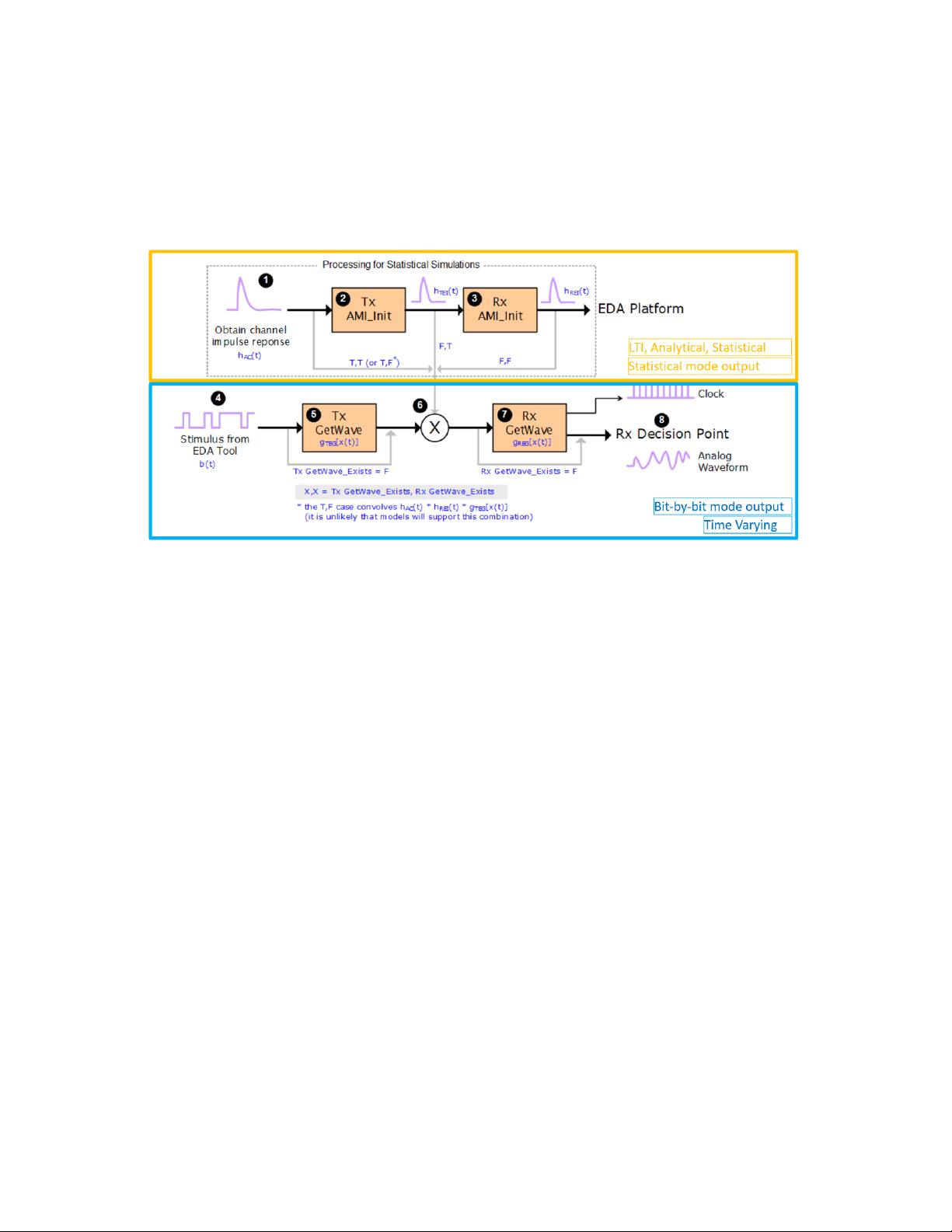

receiver equalization and clock recovery circuits. There are two fundamental simulation

flows supported by IBIS-AMI: a statistical simulation flow for models with LTI

equalization algorithms; and a time-domain flow which permits nonlinear or time-variant

equalization characteristics [3]. See Figure 1 for reference flow.

Figure 1. The IBIS-AMI statistical and time-domain reference flow [3]

IBIS-AMI Models: eesof_pcie5_tx/rx_adapt

The following is a description of the PCIe 5.0 specification-based IBIS-AMI models.

The Tx IBIS-AMI is an LTI model (Init_Returns_Impulse=True). Tx input parameters

are transmitter jitter components (Tx_Rj, Tx_Dj, Tx_DCD) and the 10 Tx EQ presets as

defined by specification (tx_preset).

The Rx IBIS-AMI is a NTV model (GetWave_Exists=True). Rx input parameters are

Ignore bits (In bit-by-bit mode, defines how many bits to use for Rx adaption phase

before eye-margin data is captured), receiver jitter components (Rx_Rj, Rx_Dj,

Rx_DCD) and equalization controls for CTLE and DFE:

• rx_ctle_adapt_enable. Set to 1 for Rx CTLE adaptation. Set to 0 for manual

control.

• rx_ctle_dcgain. DC Gain parameter for CTLE. As defined by spec, can vary from

-5dB to -15dB in 1dB increments. Used only when rx_ctle_adapt_enable=0

(adaptation disabled).

Also available from Rx IBIS-AMI model is output parameters that provide visibility into

the CTLE and DFE automatic adaptation:

• rx_dfe_tap1_limit. View dfe tap1 limit measurement as it complies with h1/h0 <

0.8 spec requirement.

• rx_dfe_tapN_value. View DFE coefficients as they adapt during the simulation.

• rx_ctle_dcgain_value. View CTLE DC Gain value, either final adaptation or

what was manually selected.

Information Classification: General

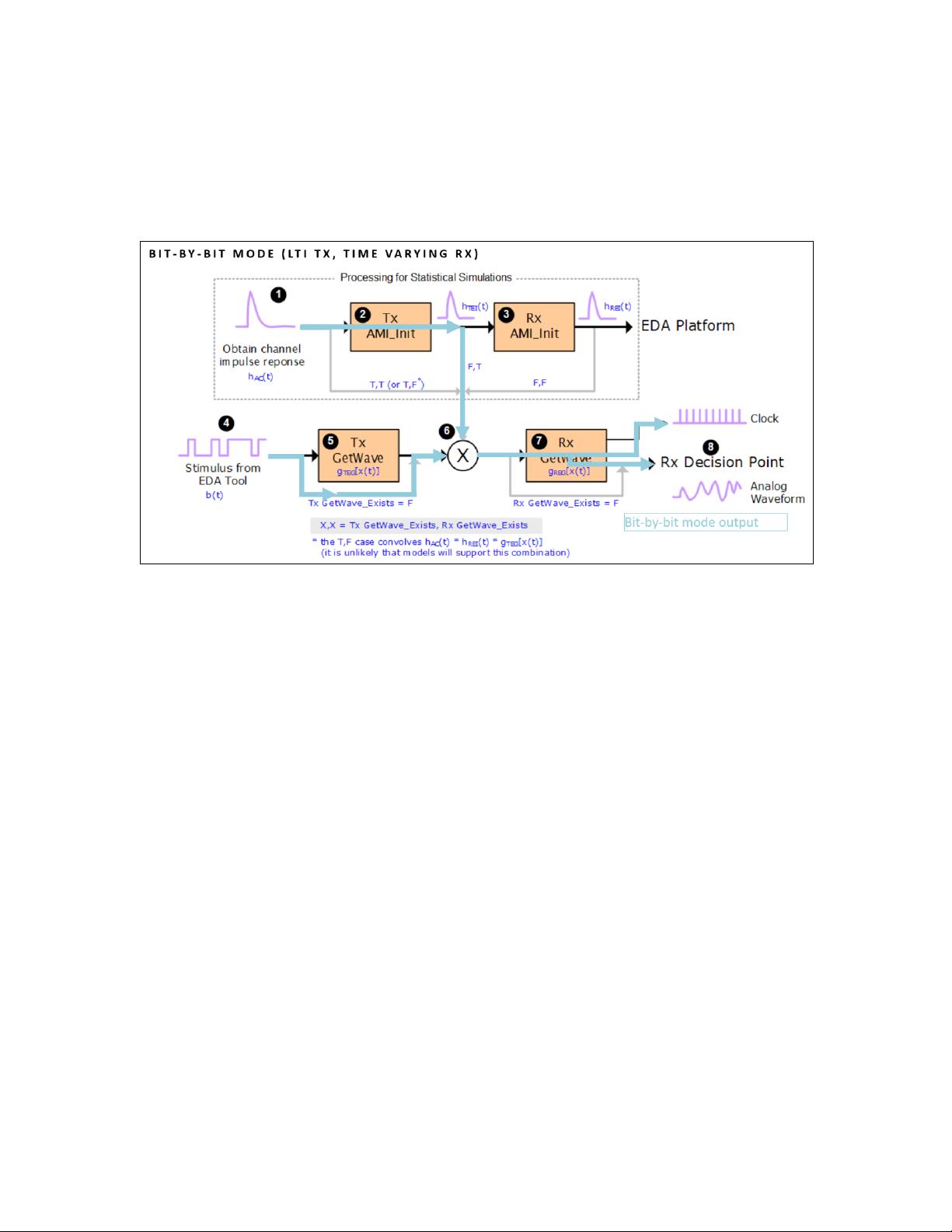

As a performance benchmark, running a Tx IBIS-AMI connected to S-parameter channel

in followed by Rx IBIS-AMI in a single CPU laptop runs 100k bits in 50 seconds. See

Figure 2 for simulation for when Tx is LTI and Rx is NTV. The highlights paths show

how AMI_Init processing is used for Tx and AMI_Getwave for Rx.

Figure 2. The PCIe 5.0 IBIS-AMI Tx and Rx simulation flow.

PCIe 5.0 Collateral Used for IBIS-AMI Model

The PCIe 5.0 electrical base specification is a 1299-page document [1]. Out of that

material, only 30-50 pages are pertinent for AMI model building. As I list out the

electrical signaling collateral used for AMI modeling, I’ll reference page numbers to

PCIe 5.0 base electrical specification document to allow for more in-depth review of the

material.

Tx EQ behavior vs spec

1) Using PCI Express Base Spec Revision 5.0, Version 1.0 - PCI-SIG (page 1005)

剩余22页未读,继续阅读

资源评论

glowlaw2023-07-27通过对最新PCIe5.0规范的介绍和解读,该文件使读者能够跟上行业发展的最新趋势,并掌握相关技术。

glowlaw2023-07-27通过对最新PCIe5.0规范的介绍和解读,该文件使读者能够跟上行业发展的最新趋势,并掌握相关技术。 雨后的印2023-07-27该文件提供了实用的技术指南和建议,帮助读者解决了在使用过程中常见的困惑和问题。

雨后的印2023-07-27该文件提供了实用的技术指南和建议,帮助读者解决了在使用过程中常见的困惑和问题。 林书尼2023-07-27该文件用简洁的语言解释了IBIS-AMI模型的原理和应用,让读者能够轻松理解并快速上手。

林书尼2023-07-27该文件用简洁的语言解释了IBIS-AMI模型的原理和应用,让读者能够轻松理解并快速上手。 仙夜子2023-07-27这份文件详细介绍了基于PCIe5.0规范的IBIS-AMI模型,让读者深入了解并掌握相关知识。

仙夜子2023-07-27这份文件详细介绍了基于PCIe5.0规范的IBIS-AMI模型,让读者深入了解并掌握相关知识。 稚气筱筱2023-07-27作者在文中给出了实际案例,展示了该模型在实际工程中的应用,使读者能够更好地理解其实际价值。

稚气筱筱2023-07-27作者在文中给出了实际案例,展示了该模型在实际工程中的应用,使读者能够更好地理解其实际价值。

小孟boy

- 粉丝: 4718

- 资源: 29

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功