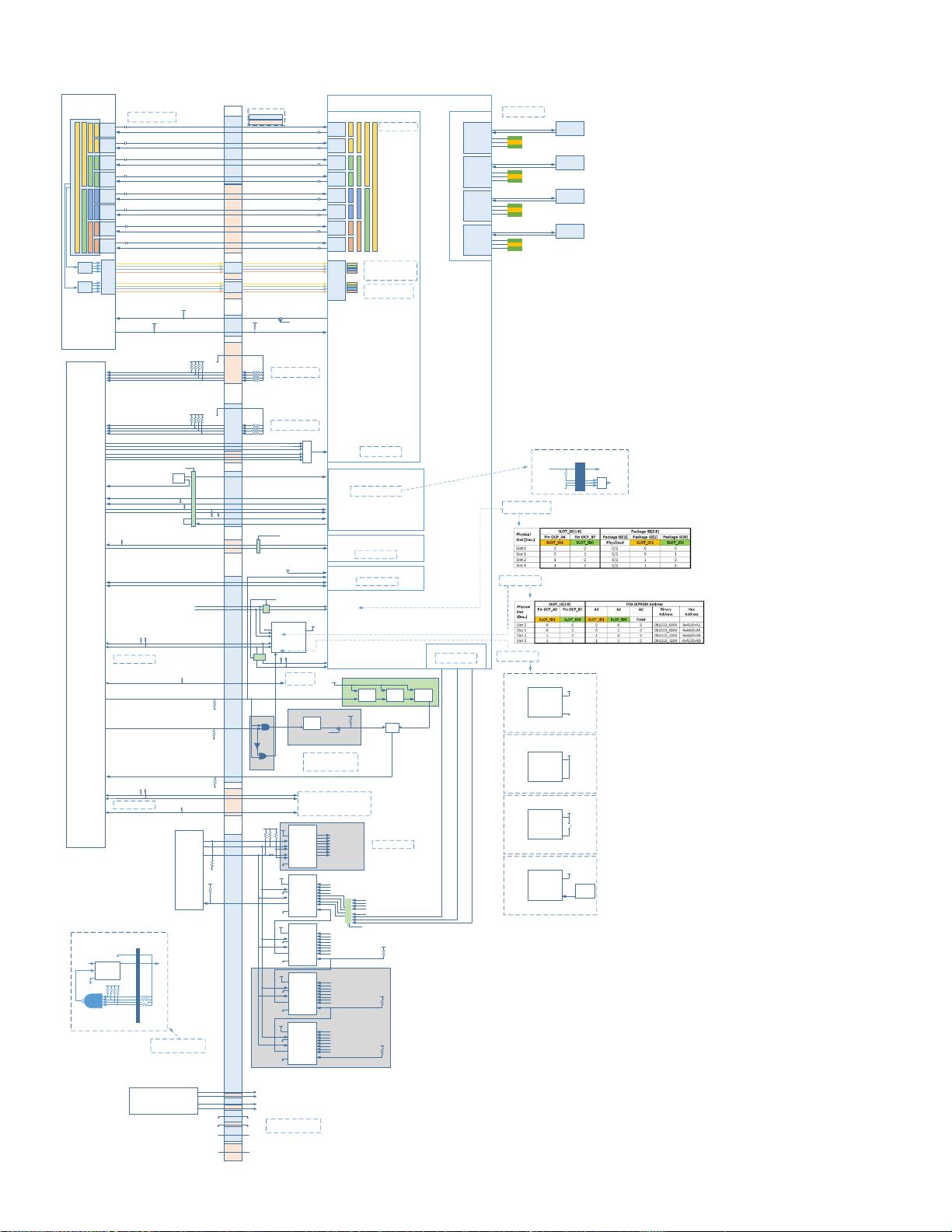

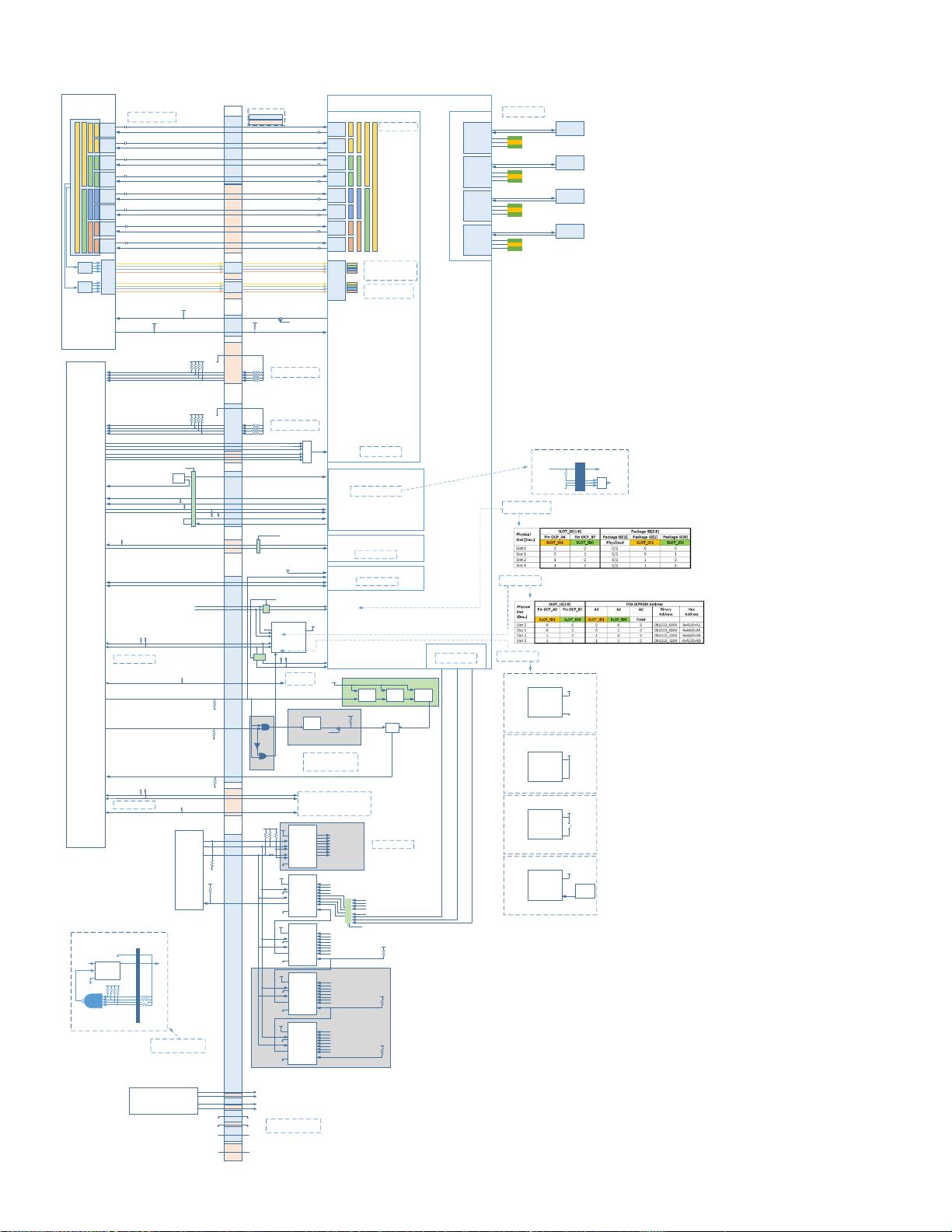

PCIe [12:15]

PCIe [4:7]

AUX/Single Power Domain

System Power Supply

Platform I/O Hub /

BMC (Example)

Networking Silicon

PCIe [8:11]

PORT 1

WAKE#

EP Bifurcation Control

Pin(s)

CLK_IN

ARB_OUT

CRS_DV

RXD[0:1]

TX_EN

TXD[0:1]

PACKAGE_ID[0] = SLOT_ID0

PACKAGE_ID[1] = SLOT_ID1

PACKAGE_ID[2] = 0b0

V

BUS

USB_DATp

V

BUS

Detection

PCIe [0:3]

PCIe [4:7]

PCIe [8:11]

PCIe [12:15]

REFCLK0 – EP0

REFCLK1 – EP1

REFCLK2 – EP2

REFCLK3 – EP3

PERST0 – EP0

PERST1 – EP1

PERST2 – EP2

PERST3 – EP3

8 x4 case: four REFCLKs

4 x8 case: four REFCLKs

2 x16 case: two REFCLKs

1 x32 case: one REFCLK

Refer to Section 3.6 for REFCLK assignment details.

EP #0 – 1 x4EP #1 – 1 x4

EP #2 – 1 x4EP #3 – 1 x4

EP #0 - 1 x8EP #1 - 1 x8

EP #0 - 1 x16

Link 2

Link 3

Link 0

Link 1

Link 2

Link 3

Link 0

Link 1

Secondary

Primary

OCP NIC 3.0 LFF - Single Host Implementation Example (single, dual, quad, octal link)

REFCLK0

REFCLK1

REFCLK2

REFCLK3

PERST0

PERST1

PERST2

PERST3

AUX_PWR_GOOD

(Internal)

WAKE_N

PWRBRK0#

Comb.

Gate

Logic

BIF0#

BIF1#

BIF2#

50MHz

Clock

RBT_CLK_IN

REF_CLK

CRS_DV

RXD[0:1]

TX_EN

TXD[0:1]

RBT_CRS_DV

RBT_RXD[0:1]

RBT_TX_EN

RBT_TXD[0:1]

RBT_ARB_OUT

RBT_ARB_IN

FET Switch

ARB_IN

BIF Pin Option (Static Configuration)

BIF0#

BIF1#

BIF2#

Comb.

Gate

Logic

AUX_PWR_EN

To power topology

Primary/Secondary

Connector

FRU EEPROM

“AUX Power Good” (local signal)

Isolator

SMCLK

SMDAT

A0

A1

A2

+3.3V (NIC)

SLOT_ID0 = 0

SLOT_ID1 = 0

See pin descriptions for

SLOT_ID[1:0] encoding values.

SMCLK

SMDAT

SLOT_ID0

SLOT_ID1

+3.3V_EDGE

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

+3.3V_EDGE

SMRST*

To SMBus devices with

RST* pin (e.g. I/O

Expander)

Optional MAIN Power Domain

SVR #1 SVR #2

PG PG

VINVIN

AUX_PWR_EN

SVR #3

PG

VIN

+3.3V_EDGE

10k

Ohm

+12V_EDGE

EN EN EN

SVR #4

PG

VIN

MAIN_PWR_EN

EN

Optional. Implementation dependent on endpoint silicon.

VOUT VOUT VOUT

VOUT

100k

Ohm

+3.3V_EDGE

COMB.

Logic

10k

Ohm

Optional logic for

Programming

Mode

N-FET

Powered from

+3.3V_EDGE

MAIN_PWR_EN

AUX_PWR_EN

MAIN_PWR_EN

NIC_PWR_GOOD

RBT_ISOLATE#

+3.3V_

EDGE

Host PLD

DATA_OUT

CLK (12.5MHz)

74LV594 #0

QA

QB

QC

QD

QE

QF

QG

QH

QH’

VCC

SER

SRCLK

SRCLRn

RCLK

RCLRn

GND

74LV165 #0

A

B

C

D

E

F

G

H

SER

VCC

CLK

CLK_INH

SH/LDn

QH

QH’

GND

+3.3V_EDGE

LINK_SPDA_P0#

LINK_SPDB_P0#

ACT_P0#

LINK_SPDA_P1#

LINK_SPDB_P1#

ACT_P1#

LINK_SPDA_P2#

LINK_SPDB_P2#

DATA_IN

LD_N

74LV165 #1

A

B

C

D

E

F

G

H

SER

VCC

CLK

CLK_INH

SH/LDn

QH

QH’

GND

PRSNTB[0]# (Mirrored from Primary Connector)

PRSNTB[1]# (Mirrored from Primary Connector)

PRSNTB[2]# (Mirrored from Primary Connector)

PRSNTB[3]# (Mirrored from Primary Connector)

74LV165 #2

A

B

C

D

E

F

G

H

SER

VCC

CLK

CLK_INH

SH/LDn

QH

QH’

GND

ACT_P2#

LINK_SPDA_P3#

LINK_SPDB_P3#

ACT_P3#

LINK_SPDA_P4#

LINK_SPDB_P4#

ACT_P4#

LINK_SPDA_P5#

+3.3V_EDGE

1k

Ohm

1k

Ohm

+3.3V_EDGE

Inverter

+3.3V_EDGE

+3.3V_EDGE

74LV165 #3

A

B

C

D

E

F

G

H

SER

VCC

CLK

CLK_INH

SH/LDn

QH

QH’

GND

LINK_SPDB_P5#

ACT_P5#

LINK_SPDA_P6#

LINK_SPDB_P6#

ACT_P6#

LINK_SPDA_P7#

LINK_SPDB_P7#

ACT_P7#

Implement a 1kOhm pull up to 3.3Vaux

for the last shift register on the bus.

Implement a 1kOhm pull up to 3.3Vaux

for the last shift register on the bus.

Implement a 1kOhm pull up to 3.3Vaux

for the last shift register on the bus.

Optional depending on line side port count

10k

Ohm

+3.3V_EDGE

+3.3V_EDGE

1k

Ohm

+3.3V_EDGE

1k

Ohm

+3.3V_EDGE

Reserved future use

Reserved future use

Reserved future use

Reserved future use

Reserved future use

Reserved future use

Reserved future use

Reserved future use

1k

Ohm

DATA_OUT

CLK

DATA_IN

LD_N

BIF0#

BIF2#

BIF1#

PWRBRK0#

SMCLK

SMDAT

SMRST*

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

NIC_PWR_GOOD

PRSNTA#

PET[0:3]

PER[0:3]

PET[4:7]

PET[8:11]

PET[12:15]

PER[4:7]

PER[8:11]

PER[12:15]

+3.3V_EDGE

+3.3V_EDGE

4.7 - 10k

Ohm

95k

Ohm

USB_DATn

USB_DATp

USB_DATn

USB_DATp

USB_DATn

+5.0V (NIC)

+3.3V_EDGE

SMCLK

SMDAT

+12V_EDGE

+3.3V_EDGE

Note: REFCLK0 and PERST0 required for all OCP

NIC 3.0 cards. Leave REFCLK[1:5] and PERST[1:5]

as N.C. if not implemented

N.C. N.C.

RFU[1:2]

VCC

+3.3V_EDGE

+12V_EDGE

WP

+3.3V_EDGE

TX

RX

SFP

TX

RX

GREEN

Refer to Section 3.4.4 for details on arbitration.

FAN_ON_AUXTEMP_WARN_N TEMP_CRIT_N

Refer to section 3.4.3 for details on the

SMBus interface

Refer to section 3.4.2 for details on the

BIF Pin Usage. BIF implementations may

also be static (example at right)

Refer to Section 3.4.5 for details on the

Scan Chain

Refer to Section 3.4.6, 3.8, for details on the power

supply pins, and power state machine requirements.

Refer to Section 3.11 for details on the power

sequence timing requirements.

Refer to section 3.4.7 for details on the

USB 2.0 Interface

Refer to section 3.6 for details on

PCIe mapping

Refer to sections 2.2 and 3.7 for details

on line-side implementations, LEDs, and

port numbering

Single Host Root Complex

(1 x32, 2 x16,

4 x8, or 8 x4)

PCIe [28:31]

PCIe [24:27]

PCIe [20:23]

PCIe [16:19]

PCIe [0:3]

PCIe [4:7]

PCIe [8:11]

PCIe [12:15]

Host 0

RC #0 - 1 x16

RC #1 - 1 x16

RC #0 - 1 x32

RC #0 – 1 x8RC #1 – 1 x8

RC #2 – 1 x8RC #3 – 1 x8

Platform

Reset

PCIe 1:4

Clock

Buffer

REFCLK0

REFCLK1

REFCLK2

REFCLK3

PERST0

PERST1

PERST2

PERST3

Refer to Sections 3.4.4 and 4.8.1 for details on

the NC-SI over RBT Package Addressing

requirements. PACKAGE_ID[2] == 0b0 for single

device card implementations.

Refer to Section 3.9 for the power supply rail

requirements for +12V_EDGE, +3.3V_EDGE and slot

power envelopes.

Refer to Section 4.9.1 for the SMBus

Address Map and requirements for the

FRU EEPROM addressing.

FET

Switch

GREEN

Amber

LINK_SPDA_P0#

LINK_SPDB_P0#

ACT_P0#

PORT 2

TX

RX

SFP

TX

RX

GREEN

GREEN

Amber

LINK_SPDA_P1#

LINK_SPDB_P1#

ACT_P1#

PORT 3

TX

RX

SFP

TX

RX

GREEN

GREEN

Amber

LINK_SPDA_P2#

LINK_SPDB_P2#

ACT_P2#

PORT 4

TX

RX

SFP

TX

RX

GREEN

GREEN

Amber

LINK_SPDA_P3#

LINK_SPDB_P3#

ACT_P3#

Refer to Section 3.4.2, and 3.5 for details on

the PRSNTA#/PRSNTB[3:0]# implementation

10k

Ohm

WAKE_N

+3.3V_EDGE

PCIe [0:3]

PCIe Sub-System

NC-SI over RBT Sub-System

USB Sub-System

Line-Side I/O

1k

Ohm

GND

Refer to Section 4.10.2 for FRU EEPROM

Write Protection Mechanisms

LFF Primary and

Secondary Connector

PWRBRK0#

DATA_OUT shift register not implemented

in this version of the specification

“AUX Power Good”

“MAIN Power Good”

Thermal Monitoring

FRU EEPROM Implementation: Not write protected

FRU EEPROM

VCC

+3.3V_EDGE

FRU EEPROM Implementation: FRU always write protected

WP

FRU EEPROM

VCC

+3.3V_EDGE

WP

FRU EEPROM Implementation: WP controlled by mechanical jumper

or switch

FRU EEPROM

VCC

+3.3V_EDGE

WP

FRU EEPROM Implementation: WP controlled by network silicon GPIO

FRU EEPROM

VCC

+3.3V_EDGE

WP

Network

Silicon

GPIO

Refer to Section 3.4.5 for Scan chain

thermal monitoring pin requirements

100 kOhm

100 kOhm

PET[16:19]

PER[16:19]

PET[20:23]

PET[24:27]

PET[28:31]

PER[20:23]

PER[24:27]

PER[28:31]

PWRBRK1# - NC

95K

Ohm

PWRBRK0#

RC #0 – 1 x4RC #0 – 1 x4RC #1 – 1 x4RC #1 – 1 x4RC #2 – 1 x4RC #2 – 1 x4RC #3 – 1 x4 RC #3 – 1 x4

EP #0 - 1 x32

EP #1 - 1 x16

EP #2 – 1 x8EP #3 – 1 x8

EP #0 – 1 x4EP #1 – 1 x4

EP #2 – 1 x4EP #3 – 1 x4

REFCLK4 – NC

REFCLK5 – NC

PERST4 – NC

PERST5 – NC

SMRST*

UART_RX

UART_TX

+3.3V_EDGE

UART_TX

UART_RX

UART_TX

UART_RX

FET Switch

UART Sub-System

(Smart NIC use case)

Refer to section 3.4.8 for details on the

UART Interface

+3.3V_EDGE

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

PRSNTA#

Refer to Section 3.4.2, and 3.5 for details on

the PRSNTA#/PRSNTB[3:0]# implementation

1k

Ohm

BIF1#

BIF2#

BIF3#

SMCLK

SMDAT

SMRST*

SMCLK

SMDAT

N.C. N.C.

RFU[3:4]

SMBus on the Secondary Connector may be a separate bus and is

reserved for a future use case. See section 3.4.3 for more details on the

SMBus Inteface

Refer to the PCIe Base Specification for the

appropriate AC coupling cap (C

TX

) value

associated with each PCIe generation.

Hot Swap Example (optional)

+12V_EDGE

Hotswap

Controller

VIN

EN

VOUT

+12V

Enable +12V_EDGE on non-zero

PRSNTB[3:0]# value.

PRSNTA#

1k

Ohm

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

+3.3V_EDGE

Tss

Css

Connector Boundary

To SVR inputs

Refer to Section 3.10 for Hot Swap considerations

and implementation strategies

+12V_EDGE

PRSNTB0#

PRSNTB1#

PRSNTB2#

PRSNTB3#

Note: For baseboard designs with multiple Primary

Connectors, connect ARB_IN and ARB_OUT to an analog mux

to complete the NC-SI HW arbitration ring based on the

number of cards installed on the NC-SI over RBT bus.

Command-based (software) arbitration may optionally be

used for shared bus topologies. Refer to DSP0222 for details.

Primary Connector

Secondary Connector

Connector color coding

AUX_PWR_EN

4-bit 2:1 Mux

S=1 S=0

PRSNTB[0]# (Mirrored from Secondary Connector)

PRSNTB[1]# (Mirrored from Secondary Connector)

PRSNTB[2]# (Mirrored from Secondary Connector)

PRSNTB[3]# (Mirrored from Secondary Connector)

WAKE_N (Mirrored from Primary Connector)

S

BIF0#

BIF2#

BIF1#

AUX_PWR_GOOD (Internal)

+3.3V_EDGE

Refer to section 3.4.3 for details on the

SMBus interface

+3.3V_EDGE

+12V_EDGE

+12V_EDGE

+12V_EDGE

+12V_EDGE

+3.3V_EDGE

+3.3V_EDGE

+3.3V_EDGE

GND

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功