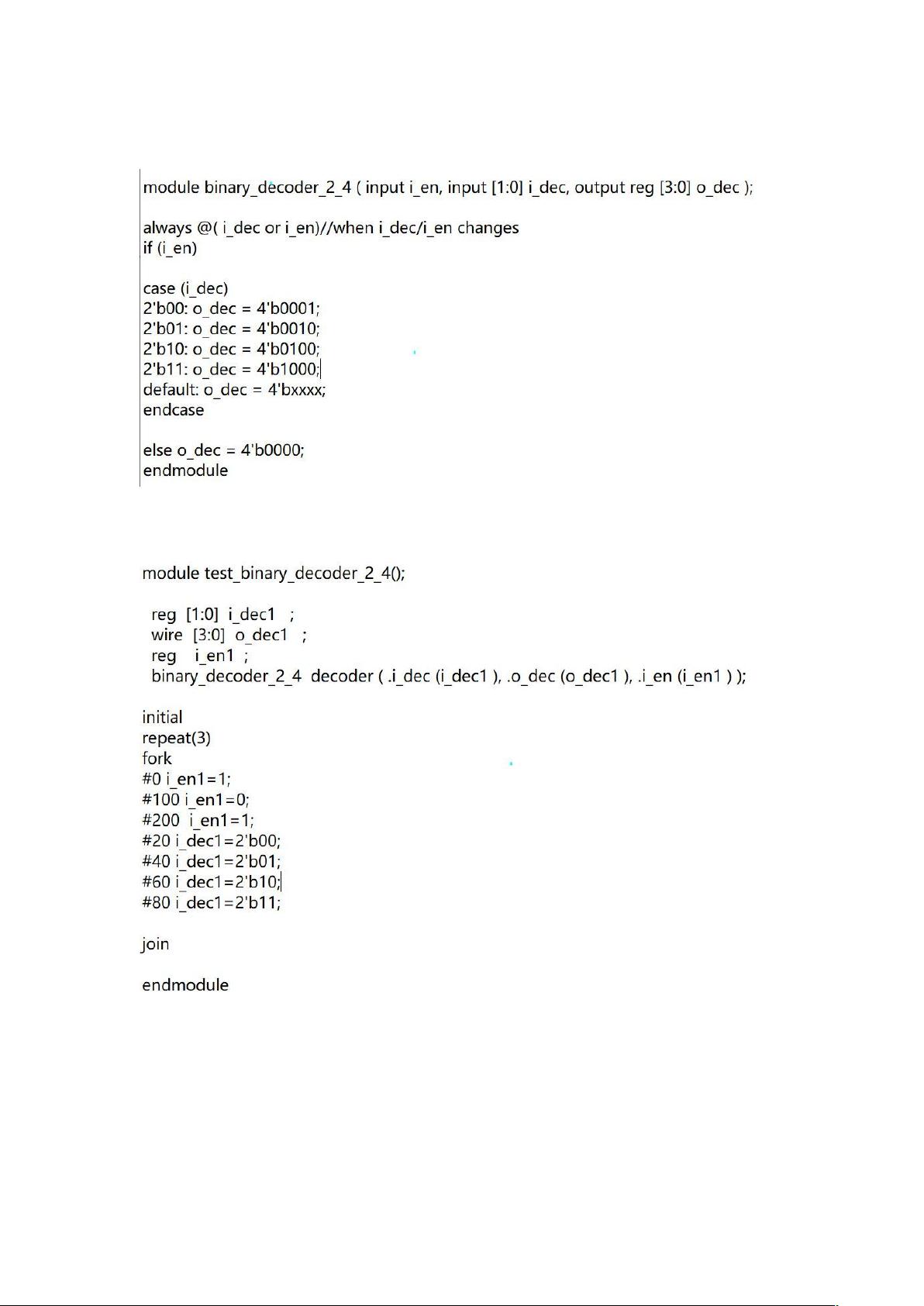

本文介绍了2-4译码器的modelsim实现,文档中包含代码,仿真结果。作者亲测代码无bug,内容详细,易于理解,适合初学者。本文还采用了do文件的仿真方式,即写tcl命令的方式,配合译码器这一例子,加深对tcl命令方式进行仿真的理解。 2-4 译码器是一种数字逻辑电路,它接收2位二进制输入(i_dec)并产生4位二进制输出(o_dec)。在使能输入端口(i_en)有效时,译码器根据输入值解码并输出相应的4位编码。如果使能信号无效,所有输出应为0。在Verilog中,我们可以用模块定义这种功能,并通过仿真验证其正确性。 在Modelsim这样的仿真工具中,有两种主要的仿真方式:一种是通过传统的testbench(测试平台)方法,另一个是使用TCL命令进行仿真。在传统方式中,我们需要创建一个模块文件(module)和一个测试文件(testbench),然后通过Modelsim的图形用户界面(GUI)执行一系列操作来编译、仿真和查看结果。 对于TCL命令仿真,我们首先需要确保模块文件被编译无误。然后,通过"File"菜单创建一个新的"Source",选择"DO"文件类型。DO文件是Modelsim支持的TCL脚本,用于自动化仿真流程。在DO文件中,我们可以编写TCL命令来编译、仿真和显示结果。例如,图3中的TCL代码可能包括了`vcom`命令编译源代码,`vsim`命令启动仿真,以及`run`命令执行仿真过程。注释符`#`用于标记非执行文本,其余命令则按照指定的逻辑执行。 例如,一个简单的DO文件可能会包含如下命令: ```tcl vcom -work work your_module.v vsim -t 1ps -c work.your_module your_testbench run -all wave add your_signals view wave run -all ``` 在TCL仿真完成后,结果可以在Transcript窗口中通过`do`命令加载,如`do filename.do`。这样,可以观察到与常规方法相同但更自动化产生的仿真波形。图5显示了两种仿真方式的结果对比,上面的是通过DO文件的TCL命令仿真,下面的是通过常规方法(实例化testbench)的仿真。 使用TCL命令仿真有助于减少手动操作,提高效率,尤其是在大型项目或重复性仿真任务中。这种方式也使得仿真流程更易于自动化和集成到持续集成系统中。对于初学者而言,掌握TCL命令可以提升在Verilog设计和验证中的技能水平。

- 粉丝: 5

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功