FSMs and Synchronization

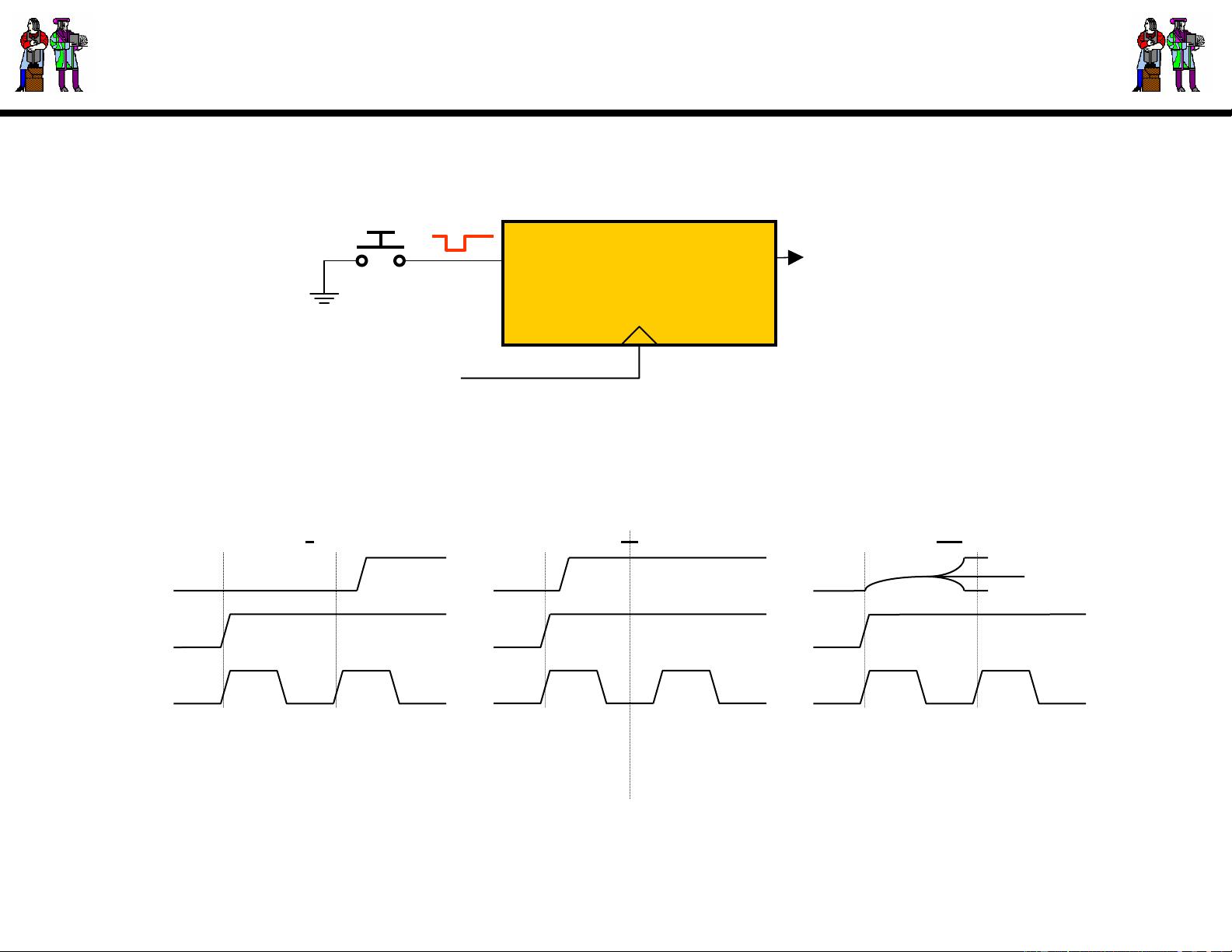

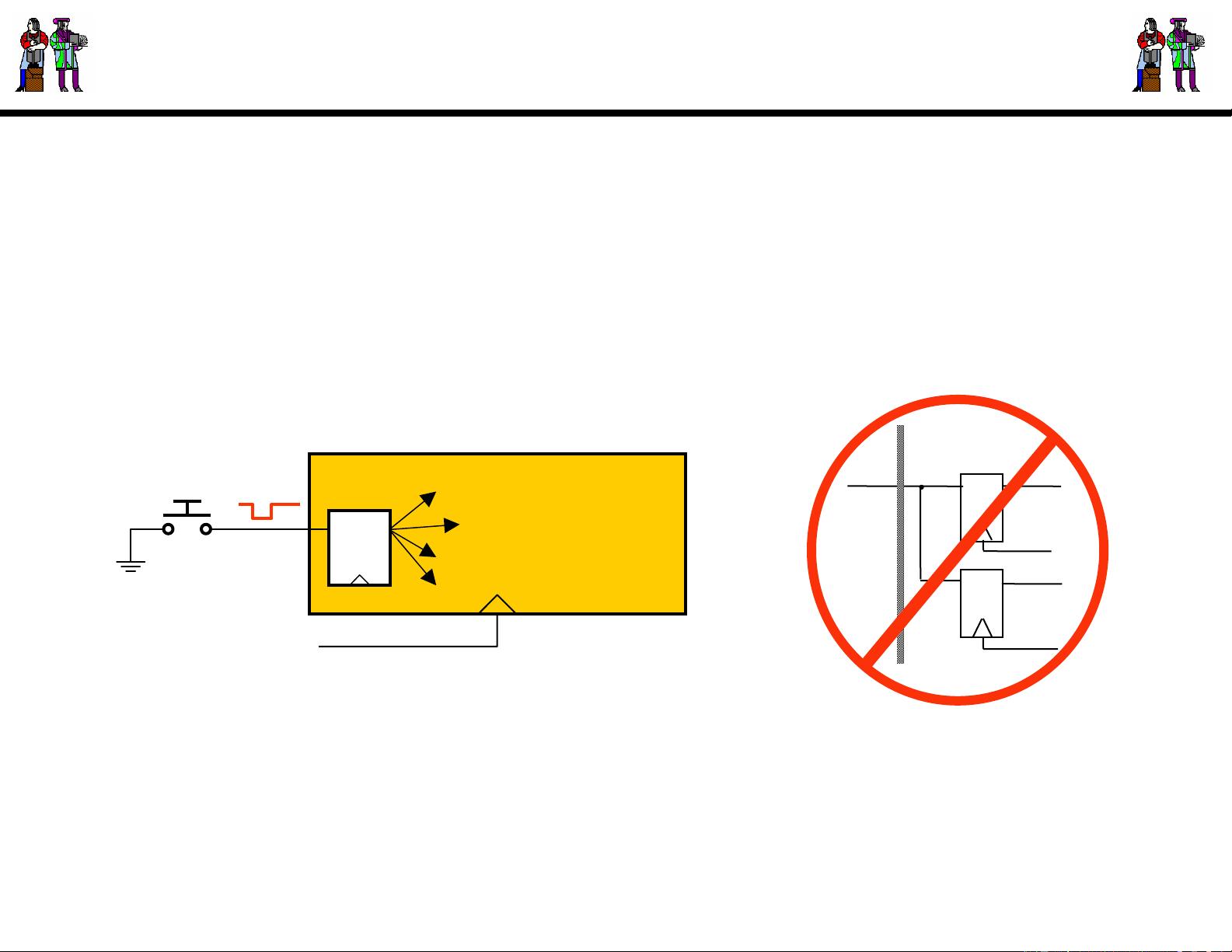

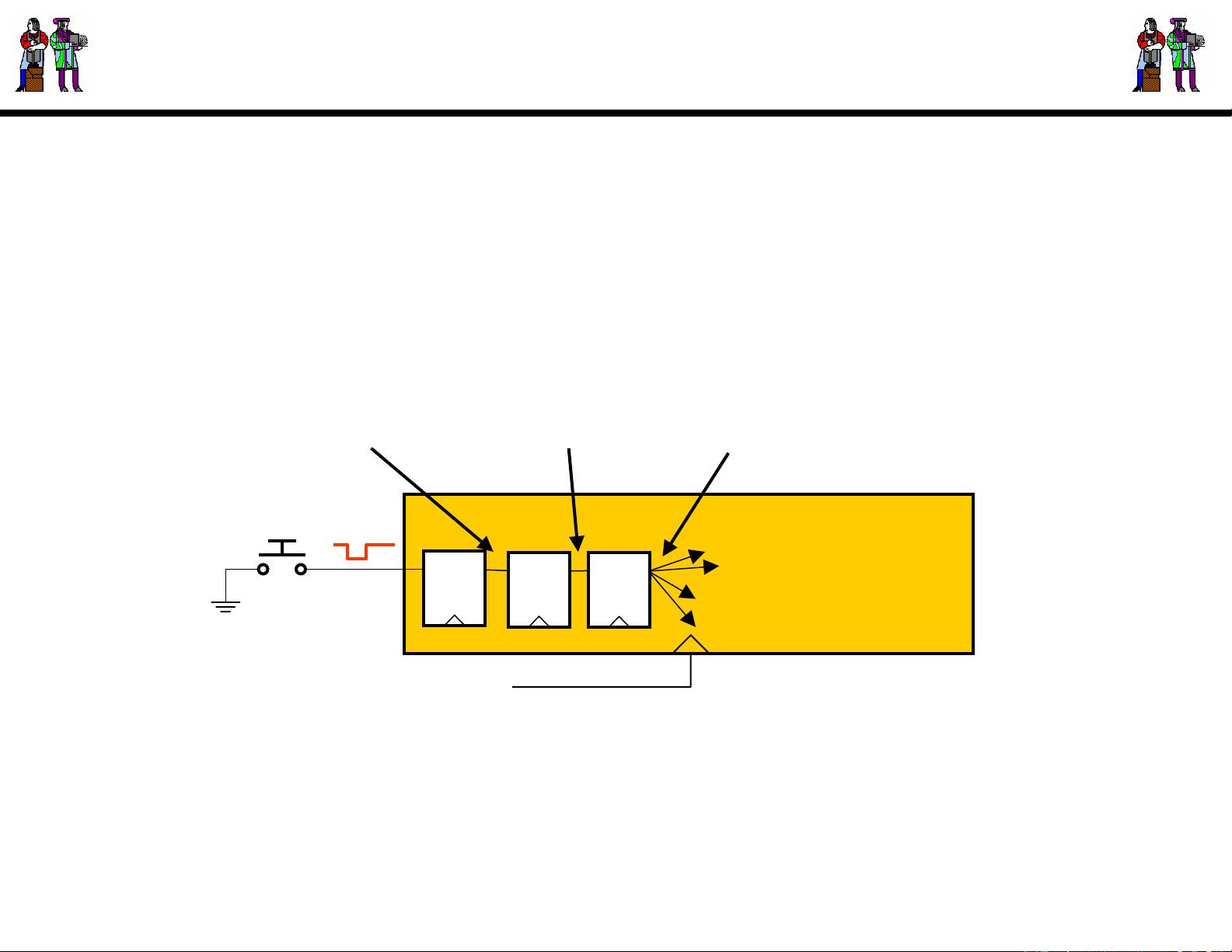

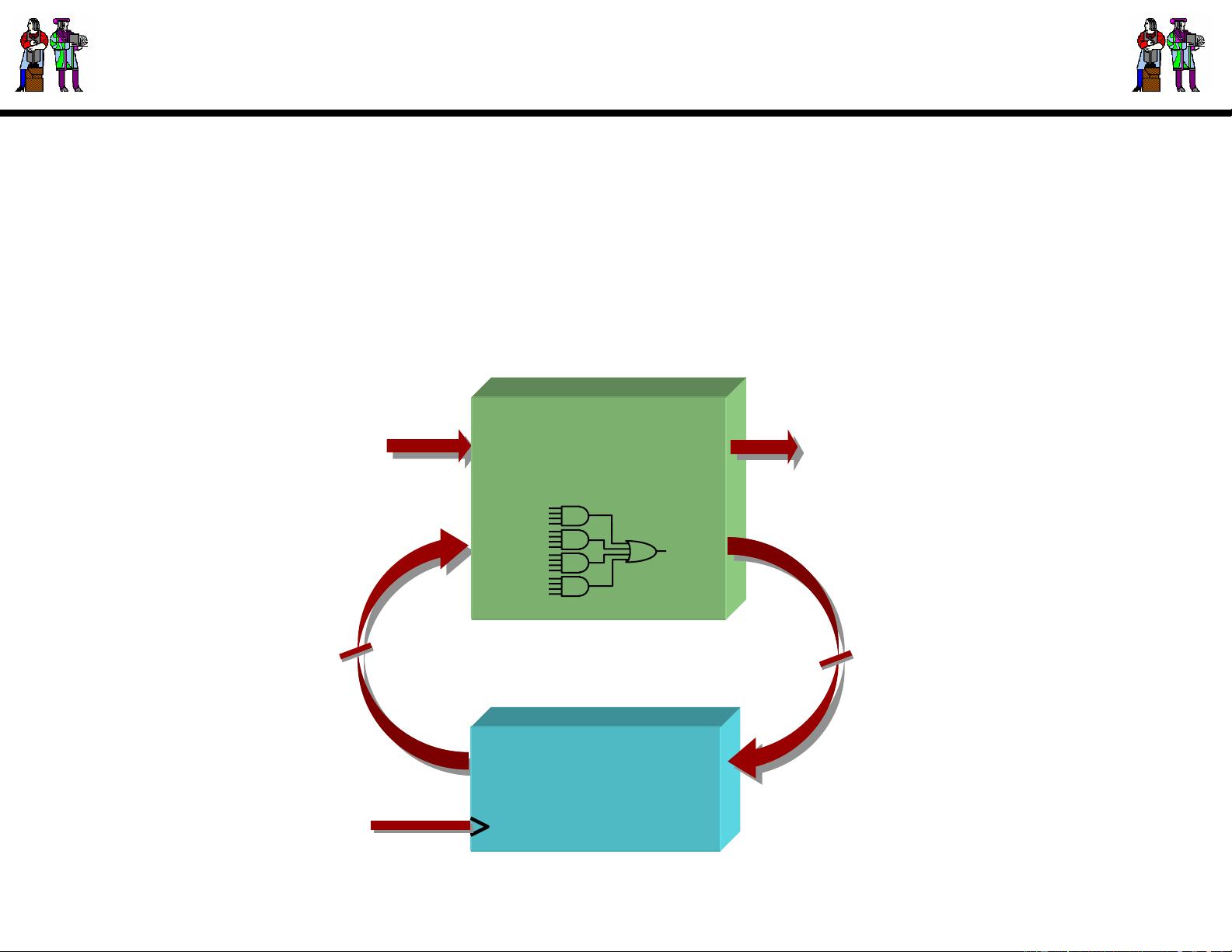

### FSMs与同步 在数字系统设计领域,特别是硬件描述语言如Verilog的应用场景中,状态机(Finite State Machine, FSM)是一种极为重要的抽象模型。本文档“FSMs and Synchronization”是MIT的一份关于逻辑设计课程的课件,重点介绍了几种状态机的设计方法以及流程图的绘制方式。通过学习本课件,可以加深对如何使用Verilog来设计状态机的理解。 #### 一、状态机基础知识 **状态机**是一类数学模型,它由有限个状态组成,并且能够在外部输入信号的作用下改变当前的状态。状态机可以分为两大类:**Mealy状态机**和**Moore状态机**。这两类状态机的主要区别在于输出信号的确定时间点不同。 - **Moore状态机**的输出仅依赖于当前的状态,而与输入信号无关。 - **Mealy状态机**的输出不仅依赖于当前状态,还依赖于输入信号。 #### 二、状态机设计 在本课件中,将详细介绍几种常见的状态机设计方法,包括但不限于: 1. **状态转换表**:这是设计状态机的基础,它定义了每个状态下机器的行为,以及在接收到不同输入时的状态转换规则。 2. **状态转换图**:通过图形化的方式表示状态机的工作原理,有助于更直观地理解状态机的工作过程。 3. **编码方案**:选择合适的编码方案对于减少电路复杂度、提高效率非常重要。 4. **状态编码**:根据具体需求,可以采用格雷码、二进制编码等不同的编码方法来表示状态机的不同状态。 5. **状态简化**:通过对状态进行合并等操作,可以进一步简化状态机的设计,减少硬件资源消耗。 #### 三、同步问题及其解决方法 课件还讨论了在设计同步数字系统时遇到的一个常见问题——**异步输入信号处理**。当外部信号进入同步系统时,可能会导致设置时间(setup time)和保持时间(hold time)的违反,从而引发一系列问题,如元稳定性(metastability)。元稳定性是指电路在不确定的时间内处于不稳定状态的情况,这通常发生在时钟边沿触发的寄存器中。 为了解决这个问题,文档提出了一些解决方案: 1. **确保每个外部信号只直接连接到一个寄存器**:这样可以避免同时在多个地方出现设置和保持时间的违反。 2. **使用同步寄存器**:通过增加同步寄存器的数量,可以为信号提供足够的时间来稳定下来。通常情况下,一到两个同步寄存器就足够了。 #### 四、实例分析 文档中的部分示例展示了如何通过增加同步寄存器来处理异步输入信号的问题。例如,在一个复杂的时序逻辑系统中,如果直接将异步信号连接到寄存器,那么该寄存器在采样后很可能处于元稳定状态。但是,通过添加额外的同步寄存器,可以让信号有更多的时间来稳定,从而极大地降低了在超过一个时钟周期内仍处于元稳定状态的可能性。 #### 五、总结 通过这份课件的学习,我们可以了解到状态机设计的基本原则和技术,特别是在处理同步问题方面的方法。这对于理解和设计高效的数字系统至关重要。无论是对于学习数字逻辑设计的学生还是从事相关工作的工程师来说,掌握这些知识都是非常有益的。

剩余28页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功