Design of ADC Control Module in a MCU

Yueli Hu, Ke Yan, Wenyi Jing

Microelectronics Research & Development Center Shanghai University

Key Laboratory of Advanced Displays and system Application, Ministry of Education, Shanghai

University

Campus P.O.B. 25, 149 Yanchang Rd., Shanghai 200072, China

E-mail:huyueli@shu.edu.cn

Abstract

A new method for ADC IP integration in a mixed-

signal MCU is proposed in this paper. The single

conversion of ADC is controlled by three modes:

software triggered mode, hardware triggered mode

and PWM triggered mode. ADC and the PWM control

module can work independently under software and

hardware triggered mode. PWM triggered mode used

for real-time monitoring is an innovation of the paper,

which simplifies software and improves the operating

efficiency of MCU. The design of the ADC control

module is elaborated and full-chip mixed-signal

verification using Nanosim-VCS is also given.

Key words:ADC; MCU ;PWM; mix-signal verification

1. Introduction

SoC technology is a new trend for VLSI design. It

provides unprecedented market prospects and

development opportunities for IC industry. The main

characteristic of SoC design is IP reuse and integration.

Today’s high performance of manufacturing processes

of integrated circuits in CMOS technology allows and

even forces due to cost issues the developers to add

more and more functionality in one circuit. The trend is

to place especially analog and even RF parts besides

digital circuits on the same die. The most common

building blocks added in this way are e.g. PLL’s, A/D

and D/A converters .In this paper ,a new method of

integrating a 10-bit SAR ADC IP in SHU-MV06, an 8-

bit MCU compatible with 8051 is proposed. The

introduction of the project is in section 2. The detail

design of the ADC control module is in section 3 and

its full-chip verification result will be presented in

section 4.

2. Introduction of the SoC design

SHU-MV06 designed in this project is a micro

controller chip of cooling fans for automotive

electronics. It is an 8-bit MCU compatible with MCS-

51, integrated with a 2-channel pulse-width modulation

(PWM) module and an ADC IP block for practical

applications. We choose a 4-channel 10-bit 3MHz

samples CMOS successive approximation ADC to

implement the design.

3. Design of ADC control module flow

The ADC module is required to perform single

conversion in software, hardware and PWM triggered

mode. The clock for conversion should be

programmable. A flag should be set and the module

should be capable of generating a CPU interrupt if

ADC interrupt is enabled after the conversion is over.

The result is in 10-bit or 8-bit format.

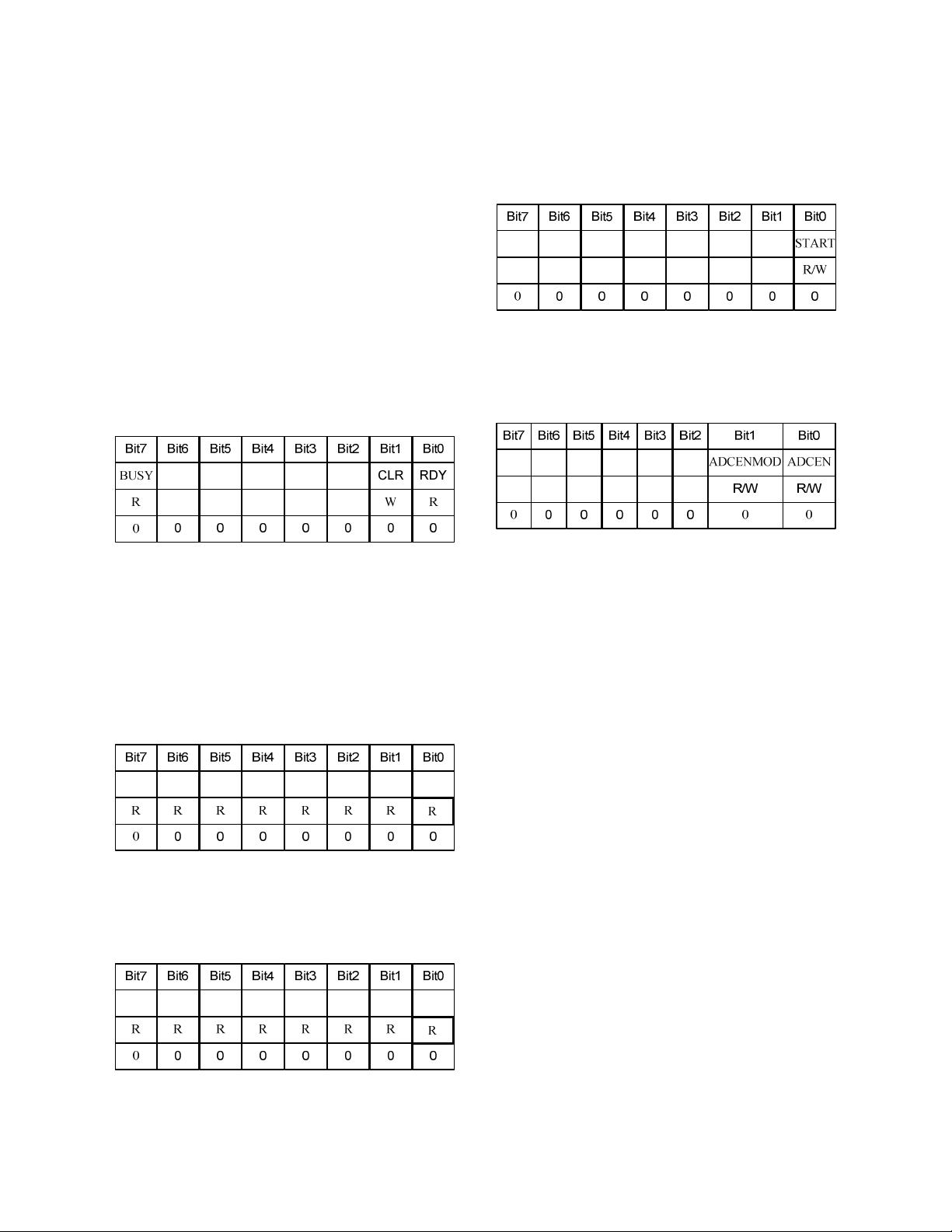

3.1. Design of ADC control module registers

We add 5 registers to control and monitor the

operation of ADC IP, including Control Register,

Status Register, Start Register and two Result

Registers. To implement PWM triggered function, we

add a PWM Trigger Enable Bit ADCEN and a Channel

Select Bit

ADCENMOD for PWM triggered mode in PWM SFR

register PWMCON.

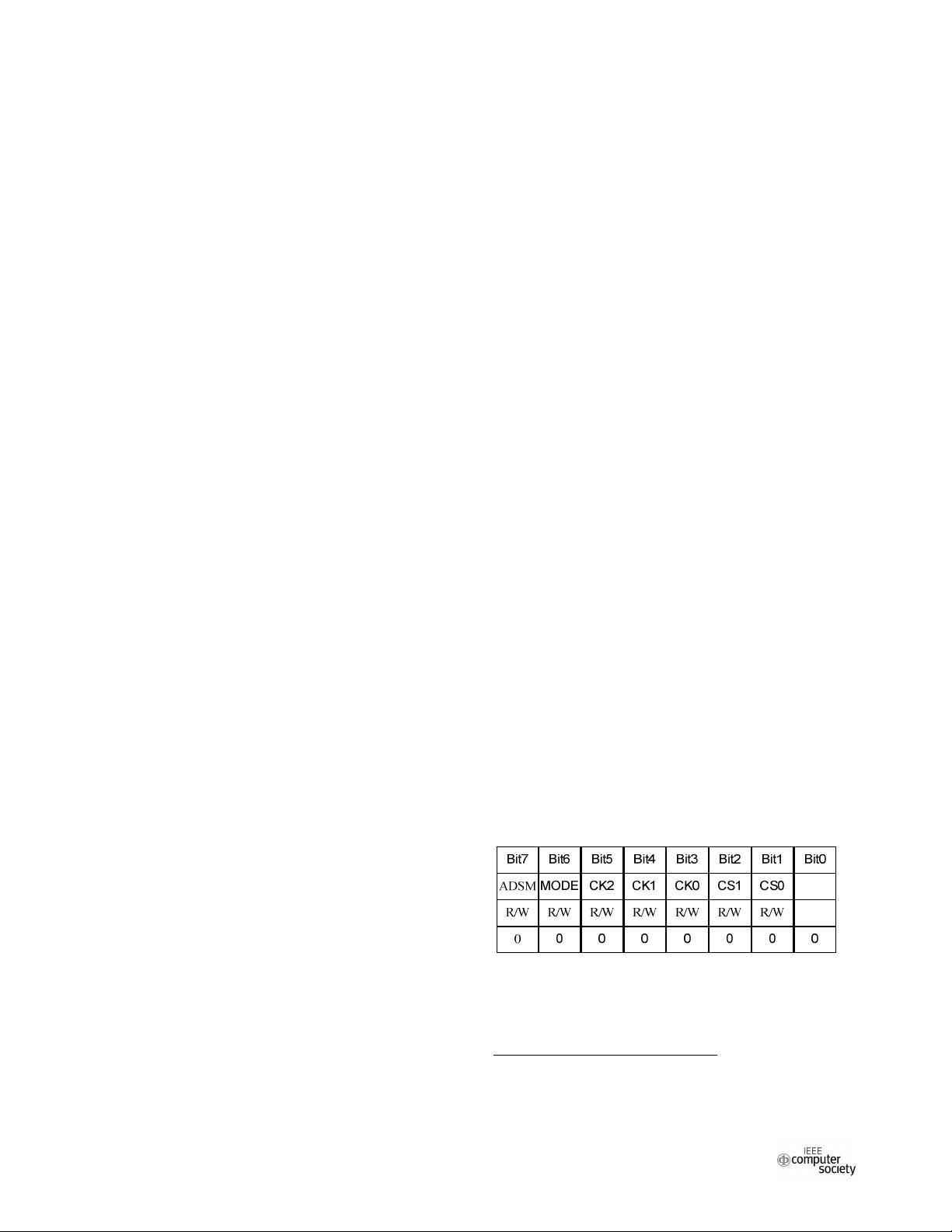

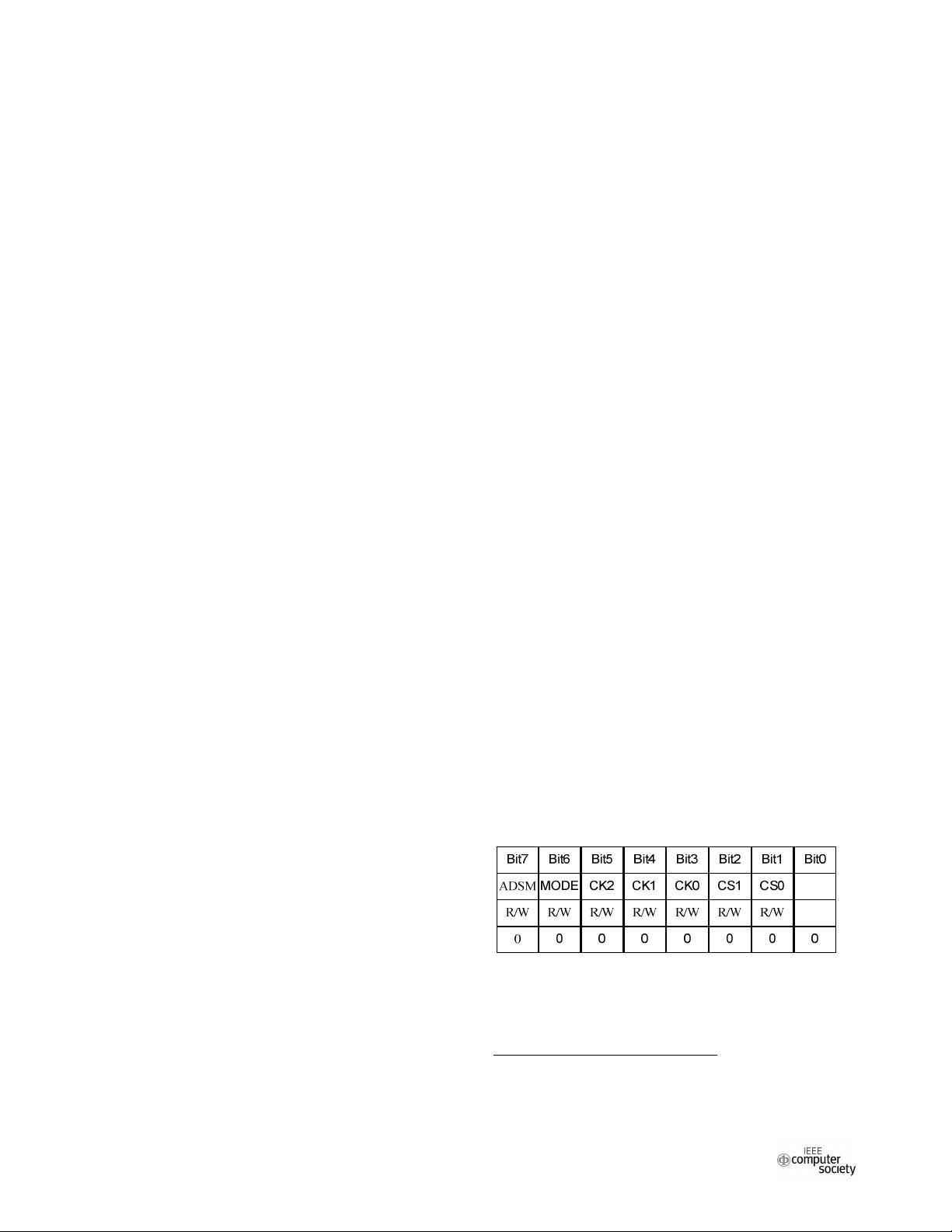

1) ADC Control Register(ADCCON F9H)

Table 1. ADC control register

ADSM is software or hardware triggered mode

select bit. If ADSM=0, ADC is in software triggered

mode. A conversion can be initiated by setting START

in ADC Start Register. If ADSM=1, ADC is in

National Natural Science Foundation of China(60773081, 60777018)

IC Special Foundation of Shanghai Municipal Commission of

Science and Technology(077062008)

Fourth International Conference on Natural Computation

978-0-7695-3304-9/08 $25.00 © 2008 IEEE

DOI

133

Fourth International Conference on Natural Computation

978-0-7695-3304-9/08 $25.00 © 2008 IEEE

DOI

133

Fourth International Conference on Natural Computation

978-0-7695-3304-9/08 $25.00 © 2008 IEEE

DOI 10.1109/ICNC.2008.204

133

Fourth International Conference on Natural Computation

978-0-7695-3304-9/08 $25.00 © 2008 IEEE

DOI 10.1109/ICNC.2008.204

133