AN10302

Using the Philips LPC2000 Flash utility with the Keil MCB2100

and IAR LPC210x Kickstart evaluation boards

Rev. 03 — 10 June 2004 Application note

Document information

Info Content

Keywords LPC2000, Flash utility, Keil MCB2100, IAR LPC210x

Abstract Application information for the Philips LPC2000 Flash utility with the Keil

MCB2100 and IAR LPC210x Kickstart evaluation boards

9397 750 13354 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Application note Rev. 03 — 10 June 2004 2 of 14

Philips Semiconductors

AN10302

Using the Philips LPC2000 Flash utility

Contact information

For additional information, please visit: http://www.semiconductors.philips.com

For sales office addresses, please send an email to: sales.addresses@www.semiconductors.philips.com

Revision history

Rev Date Description

3 10 June 2004 Third version (9397 750 13354).

Modifications:

• Updated Table 2.

• Updated Section 4.2.1.

2 12 May 2004 Second version (9397 750 13287).

1 30 April 2004 Initial version (9397 750 13231).

9397 750 13354 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Application note Rev. 03 — 10 June 2004 3 of 14

Philips Semiconductors

AN10302

Using the Philips LPC2000 Flash utility

1. Introduction

In-System programming (ISP) is a method of programming and erasing the on-chip flash

or RAM memory using the boot loader software and a serial port. The part may reside in

the end-user system. The flash boot loader provides an In-System Programming interface

for programming the on-chip flash or RAM memory. This boot loader is located in the

upper 8 kB of flash memory, it can be read but not written to or erased.

2. LPC2000 ISP overview

The flash boot loader code is executed every time the part is powered on or reset. The

loader can execute the ISP command handler or pass execution to the user application

code.

A LOW level, after reset, at the P0.14 pin is considered as the external hardware request

to start the ISP command handler. The boot loader samples this pin during reset.

Assuming that proper signal is present on X1 pin when the rising edge on RST pin is

generated, it may take up to 3 ms before P0.14 is sampled and the decision on whether to

continue with user code or ISP handler is made. If P0.14 is sampled LOW and the

watchdog overflow flag is set, the external hardware request to start the ISP command

handler is ignored. If there is no request for the ISP command handler execution (P0.14 is

sampled HIGH after reset), a search is made for a valid user program. If a valid user

program is found then the execution control is transferred to it. If a valid user program is

not found, the auto-baud routine is invoked.

Pin P0.14 is used as hardware request for ISP requires special attention. Since P0.14 is in

high impedance mode after reset, it is important that the user provides external hardware

(a pull-up resistor or other device) to put the pin in a defined state. Otherwise unintended

entry into ISP mode may occur.

Figure 1

shows the boot sequence of the LPC210x devices.

9397 750 13354 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Application note Rev. 03 — 10 June 2004 4 of 14

Philips Semiconductors

AN10302

Using the Philips LPC2000 Flash utility

Fig 1. Boot process flowchart.

9397 750 13354 © Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Application note Rev. 03 — 10 June 2004 5 of 14

Philips Semiconductors

AN10302

Using the Philips LPC2000 Flash utility

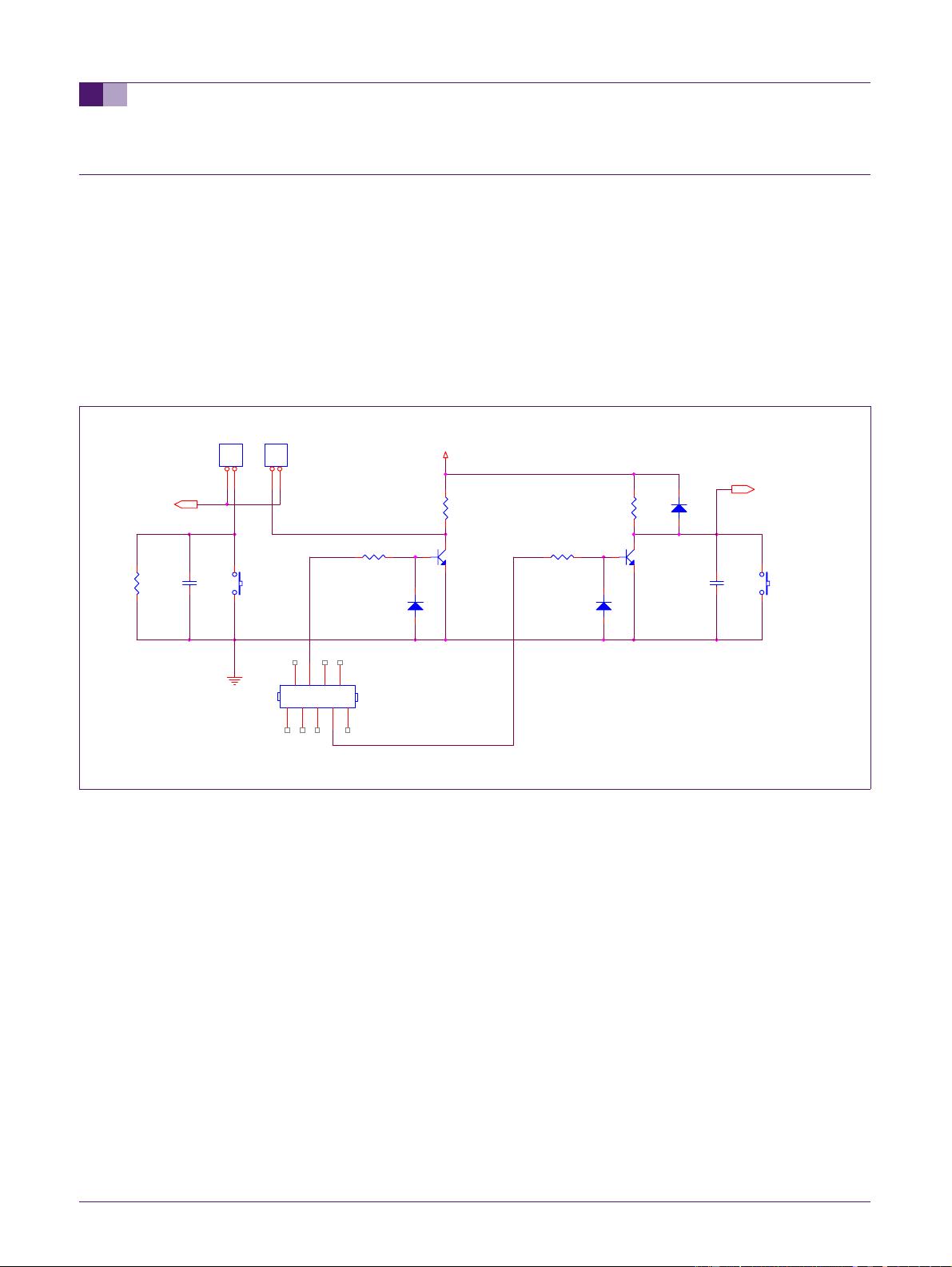

3. Details of the Philips LPC2000 Flash utility

This flash utility is available for free download from the Philips website. This software, in

combination with the hardware described below, allows for hands-off erasure, uploading,

and execution of code.

The Philips LPC2000 Flash utility utilizes two, otherwise unused, signals (RTS and DTR)

of the PC serial port to control the microcontroller reset and P0.14 pins. The port pin

P0.14, if LOW during reset, puts the microcontroller into In System Programming (ISP)

mode; this pin has the alternate functions of external interrupt one and general purpose

I/O (GPIO). Some details on the associated circuitry will help in understanding how this

works.

3.1 Manual entry into ISP mode

With jumper J1 removed and jumper J2 in place ISP mode will be entered manually by

holding S2 while pressing and releasing S1 (reset). This can become cumbersome and so

it is advantageous to use RTS/DTR control of these signals.

3.2 ISP mode entry using DTR/RTS

With jumper J1 inserted and jumper J2 removed the reset and P0.14 signals may be

controlled by the previously un-used RTS/DTR signals of the PC serial port. In this

application both these signals are active HIGH. When RTS is asserted Q2 is turned on

and the microcontroller reset is pulled LOW. While the micro is held in reset, DTR is

asserted and P0.14 is held LOW. RTS is then brought LOW and so Q2 is turned off. The

10K pull-up resistor releases the RESET signal by pulling it HIGH. The microcontroller is

now running in ISP mode.

This sequence of ISP mode entry is performed for every operation offered by the Philips

LPC2000 Flash Utility.

Fig 2. The RTS/DTR control - an example circuit.

10K

DTR

S2_INT1_ISP

D3

1 2

Q2

3

2

1

RST

22K

S1_res

et

33K

D4

1 2

D1

1 2

P2

DSUB 9-R

5

9

4

8

3

7

2

6

1

5

9

4

8

3

7

2

6

1

100n

Note: All signals to P2

except DTR and RTS have been

omitted for clarity.

33K

J2

1

2

100n

RTS

Q1

3

2

1

22K

P0.14

Vcc

J1

1

2

- 1

- 2

前往页