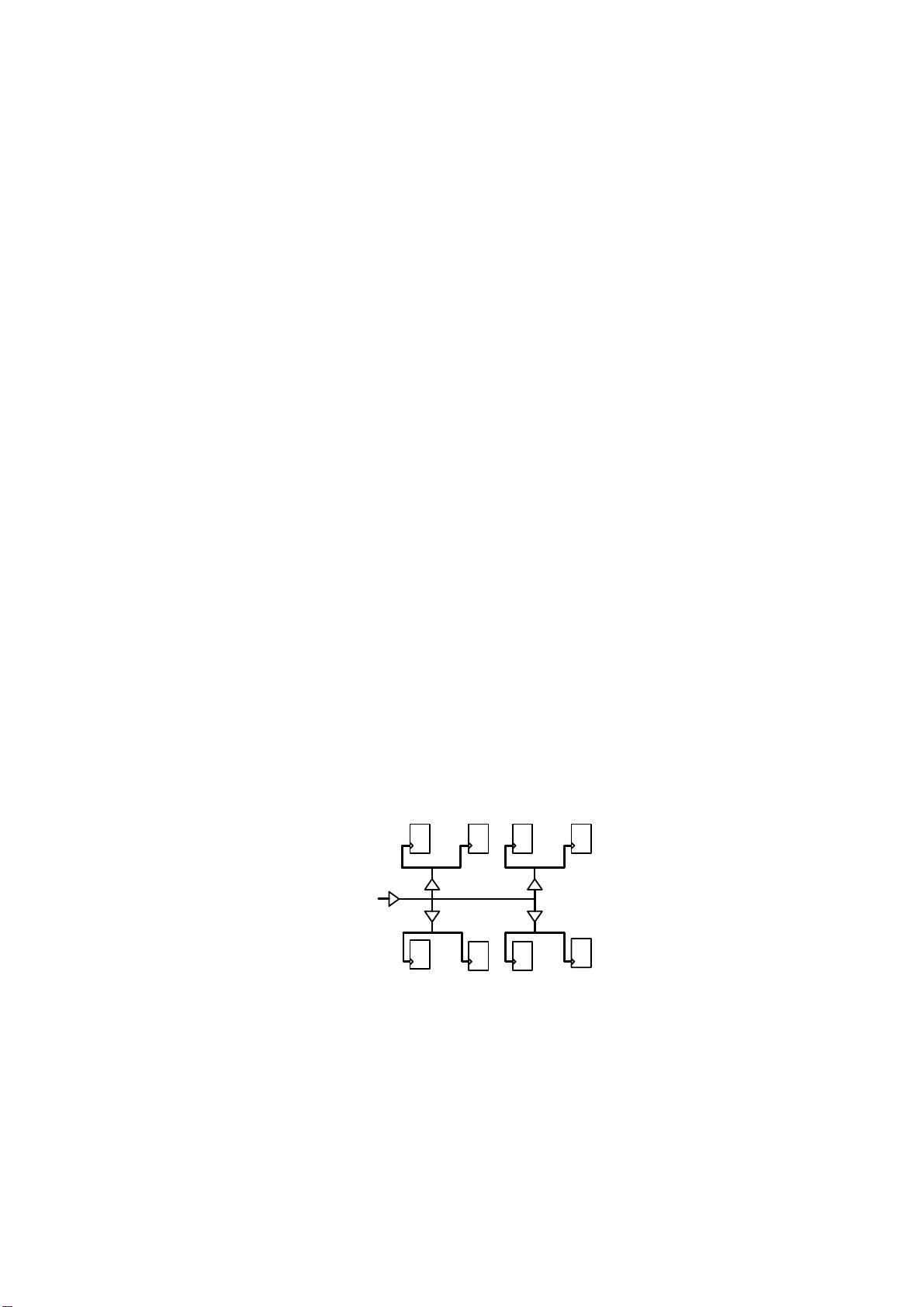

和基于ASIC(专用集成电路)的时钟电路相比,基于FPGA(现场可编程门阵列)的时钟电路有其自身的特点。FPGA一般提供其专用时钟资源搭建时钟电路,相应的综合工具也能够自动使用这些资源,但是针对于门控时钟和时钟分频电路,如果直接使用综合工具自动处理的结果,会造成较大的时钟偏差。通过合理使用DCM(数字时钟管理单元)和BUFGMUX(全局时钟选择缓冲器)等FPGA的特殊资源,手动搭建时钟电路,可以尽可能地减少时钟偏差对电路时序的影响。 ### FPGA时钟树介绍 #### 一、引言 随着集成电路技术的发展,FPGA作为一种重要的硬件平台,在电子系统设计中扮演着越来越重要的角色。相比于传统的ASIC设计,FPGA提供了更为灵活的设计方式,使得设计师能够在无需制造实体芯片的情况下,快速迭代和验证设计方案。然而,FPGA在时钟电路设计方面具有其独特的挑战,尤其是在时钟偏差管理和优化方面。本文将深入探讨FPGA时钟树的基本概念,以及如何合理利用DCM和BUFGMUX等特殊资源来减少时钟偏差。 #### 二、ASIC与FPGA时钟电路对比 ##### 1. ASIC时钟电路 在ASIC设计中,时钟偏差通常是通过动态搭建时钟缓冲器树的方法来解决。这种方法的基本原理是控制时钟源与寄存器之间的门延时与线路延时,确保同一时钟域内的所有寄存器的时钟延时大致相同,以此来减少时钟偏差。典型的ASIC时钟树结构如图1所示。 ##### 2. FPGA时钟电路 FPGA的时钟电路设计则有所不同。由于FPGA的内部布线在出厂前就已经固定,且连线延时相对于门延时较大,因此不能简单采用动态搭建时钟缓冲器树的方法。相反,FPGA通常会预先在芯片中构建固定的时钟树结构。以Xilinx公司的Virtex-II系列FPGA为例,其时钟结构如图2所示。该系列FPGA利用单独的一层铜布线层搭建时钟网络,所有时钟信号只能通过处于芯片纵向中轴线上下两端的16个BUFGMUX进入时钟网络。这种结构允许最多存在16个时钟域,但同时只能存在最多8个全局时钟。 #### 三、FPGA时钟电路的关键组件 ##### 1. DCM(Digital Clock Manager) DCM是一种数字时钟管理单元,用于产生多个频率、相位和偏移量不同的时钟信号。它可以对输入时钟进行倍频、分频、相位调整等多种操作,是FPGA时钟管理的核心组件之一。 ##### 2. BUFGMUX(Buffer Global Multiplexer) BUFGMUX是一种全局时钟选择缓冲器,用于选择并缓冲全局时钟信号。它可以在多个输入时钟信号中选择一个作为输出,并将其传输到整个FPGA芯片。BUFGMUX是连接时钟源与FPGA内部各个部分的关键部件,对于时钟信号的传播非常重要。 #### 四、FPGA时钟电路设计案例 为了更好地理解FPGA时钟电路的设计方法及其可能遇到的问题,以下是一个具体的案例分析: ##### 1. 问题背景 图3显示了一个设计实例中的4个时钟域。在这个例子中,如果不加以特别处理,可能会导致综合软件自动指定BUFGMUX,从而引起门控时钟和分频时钟与源时钟之间较大的时钟偏差。 ##### 2. 设计策略 为了减少时钟偏差,设计师需要手动搭建时钟电路,合理利用DCM和BUFGMUX等资源。例如: - 使用DCM对输入时钟进行适当的分频或倍频,以满足不同时钟域的需求。 - 通过精心选择BUFGMUX的位置和连接方式,确保每个时钟域内的时钟信号传播延时尽可能一致。 - 对于门控时钟和分频时钟,可以考虑手动插入必要的延迟或使用专门的时钟管理模块来优化时序性能。 #### 五、结论 通过对FPGA时钟电路的深入探讨,我们了解到FPGA时钟电路与ASIC时钟电路在设计方法上的显著差异。合理利用DCM和BUFGMUX等FPGA特有的资源,可以有效地减少时钟偏差,提高电路的整体性能。在未来的设计过程中,设计师应当充分利用这些特性,以获得更优的电路性能。

- 粉丝: 0

- 资源: 7

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功

- 1

- 2

前往页