ADSP-BF531/ADSP-BF532/ADSP-BF533

-1-

概要

高达 600 MHz 高性能 Blackfin 处理器

2 个 16 位 MAC,2 个 40 位 ALU,4 个 8 位视频

ALU,以及 1 个 40 位移位器

RISC 式寄存器和指令模型,编程简单,编译环境友好

先进的调试、跟踪和性能监视

内核电压 V

DD

0.8V-1.2V

片内调压器支持从 3.3V-2.5V 的输入电压

160 引脚 Mini-BGA 封装;169 引脚 PBGA 封装;176 引脚

LQFP 封装

存储器

高达 148KBytes 片内存储器:

16KBytes 指令 SRAM/Cache

64KBytes 指令 SRAM

32KBytes 数据 SRAM/Cache

32KBytes 数据 SRAM

4KBytes 存放中间结果的 SRAM

两个双通道存储器 DMA 控制器

存储器管理单元提供存储器保护

存储器控制器可与 SDRAM、SRAM、Flash 和 ROM 无缝

连接

灵活的存储器引导模式,可以选择从 SPI 口或外部存储器

导入

外设

并行外设接口(PPI) /GPIO 支持 ITU-R 656 视频数据格式

2 个双通道全双工同步串行接口,支持 8 个立体声 I

2

S 通道

12 通道 DMA 控制器

SPI 兼容端口

3 个定时/计数器,支持 PWM

支持 IrDA 的 UART

事件处理

实时时钟

“看门狗”定时器

调试 /JTAG 接口

1x-63x 倍频的片内 PLL

内核定时器

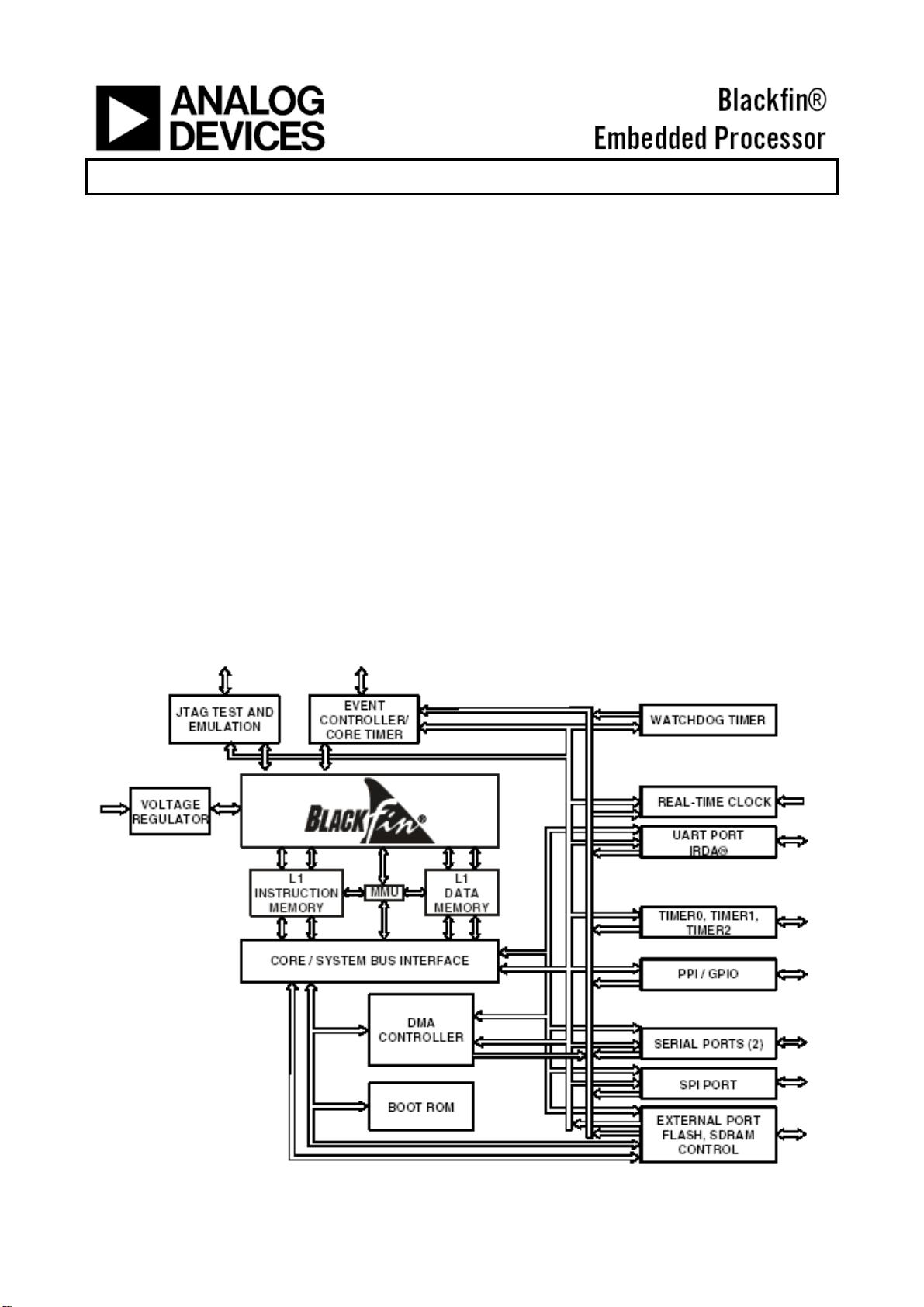

图 1. 功能框图

ADSP-BF531/ADSP-BF532/ADSP-BF533

-2-

目录

概 述…………………………………………………………3

便携式低功耗结构 ....................................................... 3

系统集成....................................................................... 3

ADSP-BF531/2/3 处理器外设...................................... 3

BLACKFIN 处理器内核 ............................................. 3

存储器结构................................................................... 4

DMA 控制器................................................................. 7

实时时钟....................................................................... 8

“看门狗”定时器 ......................................................... 8

定时器........................................................................... 8

串行口(SPORTs)........................................................... 8

串行外设接口(SPI)....................................................... 9

UART 端口 ................................................................... 9

可编程标志(PFx)..................................................... 9

并行外设接口............................................................. 10

动态电源管理............................................................. 10

电压调节..................................................................... 11

时钟信号..................................................................... 11

引导模式..................................................................... 12

指令集描述................................................................. 13

开发工具..................................................................... 13

设计仿真器兼容的 DSP 板........................................ 14

引脚描述……………………………………………………15

技术规格……………………………………………………18

推荐工作条件............................................................. 18

电气特性..................................................................... 18

绝对最大额定值......................................................... 19

ESD 灵敏度 ............................................................... 19

时序规格..................................................................... 20

时钟和复位时序................................................ 21

异步存储器读周期时序.................................... 22

异步存储器写周期时序.................................... 23

SDRAM 接口时序............................................ 24

外部端口总线请求和许可周期时序 ................ 25

并行外设接口时序............................................ 26

串行口................................................................ 27

串行外设接口(SPI)—主时序 ...................... 30

串行外设接口(SPI)—从时序 ...................... 31

通用异步收发器(

UART)端口—接收和发送

时序 ................................................................... 32

可编程标志周期时序........................................ 32

定时器周期时序 ................................................33

JTAG 测试和仿真端口时序 ..............................34

输出驱动电流 .............................................................35

功耗 .............................................................................36

测试条件 .....................................................................37

环境条件 .....................................................................40

160-LEAD BGA 引脚…………………………………..…42

169-Ball PBGA 引脚 …………………………………..…45

176-LEAD LQFP 引脚…………………………………..…47

外形尺寸 ………………………………..…..…..…..…..…49

订购指导……………………………………………………50

版本历史

11/04-版本 A: 从版本 0 变到版本 A

删除了片上调压器说明中的电压允许偏差,更换了

(图 7)电压调节电路的元件……………………………11

在推荐工作条件中定义了 ADSP-BF533 新的标称电

压…………………………………………………………18

给出了表 10,表 11 和表 12 的测试电压…………………20

改变了(表 30)内部功耗在 400MHz 时的数据………36

改变了(图 46)160-BALL Mini-BGA(BC-160)

的封装高度………………………………………………49

改变了 ADSP-BF532 和 ADSP-BF533 的工作电压,

订购指导中新增了两个型号……………………………50

11/04-版本 0: 最初版本

ADSP-BF531/ADSP-BF532/ADSP-BF533

-3-

概述

ADSP-BF531/2/3 处理器是 Blackfin 系列产品的成员,

融合了 Analog Devices/Intel 的微信号结构(Micro Signal

Architecture) (MSA)。Blackfin 处理器这种体系结构将艺

术级的 dual-MAC 信号处理引擎,简洁的 RISC 式微处理

器指令集的优点,以及单指令多数据(SIMD)多媒体能力结

合起来,形成了一套独特的指令集结构。

ADSP-BF531/2/3 处理器的代码和管脚完全兼容,它们

之间的差别仅仅在于具有不同的性能和片内存储器容量。

详细的性能和存储器区别见表 1:

表 1 处理器比较

ADSP-BF531 ADSP-BF532 ADSP-BF533

最大频率

400MHz 400 MHz 600 MHz

性能

800 MMACs 800 MMACs

1200

MMACs

指令

SRAM/Cache

16Kbytes 16Kbytes 16Kbytes

指令 SRAM

16Kbytes 32Kbytes 64Kbytes

数据

SRAM/Cache

16Kbytes 32Kbytes 32Kbytes

数据 SRAM

32bytes

中间存储器

4Kbytes 4Kbytes 4Kbytes

通过集成业界领先和丰富的系统外设及存储器,

Blackfin 处理器系列成为下一代需要将 RISC 式编程、多

媒体支持和前沿的信号处理等功能集成在单个封装内的选

择平台。

便携式低功耗结构

Blackfin 处理器系列具有世界领先的功率管理和性

能。Blackfin 处理器采用低功耗和低电压的设计方法,具

有动态功率管理的特点,即通过改变工作电压和频率来大

大降低总功耗。与仅改变工作频率相比,既改变电压又改

变频率能够使总功耗明显减少。对于便携式应用来说,这

相当于延长了电池的寿命。

系统集成

对下一代的数字通信和消费多媒体应用来说,

ADSP-BF531/2/3 处理器是高度集成的片上系统解决方案。

通过将工业标准接口与高性能的信号处理内核相结合,用

户可以快速开发出节省成本的解决方案,而无需昂贵的外

部组件。ADSP-BF531/2/3 处理器系统外设包括一个 UART

口、一个 SPI 口、两个串行口(SPORTs)、四个通用定时器

(其中三个具有 PWM 功能)、一个实时时钟、一个看门狗

定时器,以及一个并行外设接口。

ADSP-BF531/2/3 处理器外设

ADSP-BF531/2/3 处理器包含丰富的外设,它们通过不

同的高速宽带总线与内核相连,使系统不但配置灵活而且

有极好的性能(见第 1 页的图 1)。通用外设包括一些功能,

如 UART、带 有 PWM(脉冲宽度调制)和脉冲测量能力的

定时器、通用的 I/O 标志引脚、一个实时时钟和一个看门

狗定时器。这些外设满足了典型系统的各种需求,并且通

过它们增强了系统的扩充能力。除了这些通用的外设,

ADSP-BF531/2/3 处理器还包含有用于各种音频、视频和调

制解调编解码功能的高速串行和并行端口;一个用于灵活

地管理来自片内外设和外部信源的中断事件处理器;以及

可根据不同的应用来配置系统的性能和功耗的功率管理控

制功能。

除通用 I/O,实时时钟和定时器外,所有其它的外设都

有一个灵活的 DMA 结构。片内还有一个独立的存储器

DMA 通道,专用于在处理器的不同存储空间,包括外部的

SDRAM 和异步存储器,进行数据传输。多条片内总线能

以 133MHz 的速度运行,提供了足够的带宽以保证处理器

内核能够跟得上片内和片外外设。

ADSP-BF531/2/3 处理器包含支持 ADSP-BF531/2/3 处

理器动态功率管理功能的片上调压器,从 2.25V 到 3.6V

的单输入电压提供内核电压。该调压器也可以由用户旁路。

BLACKFIN 处理器内核

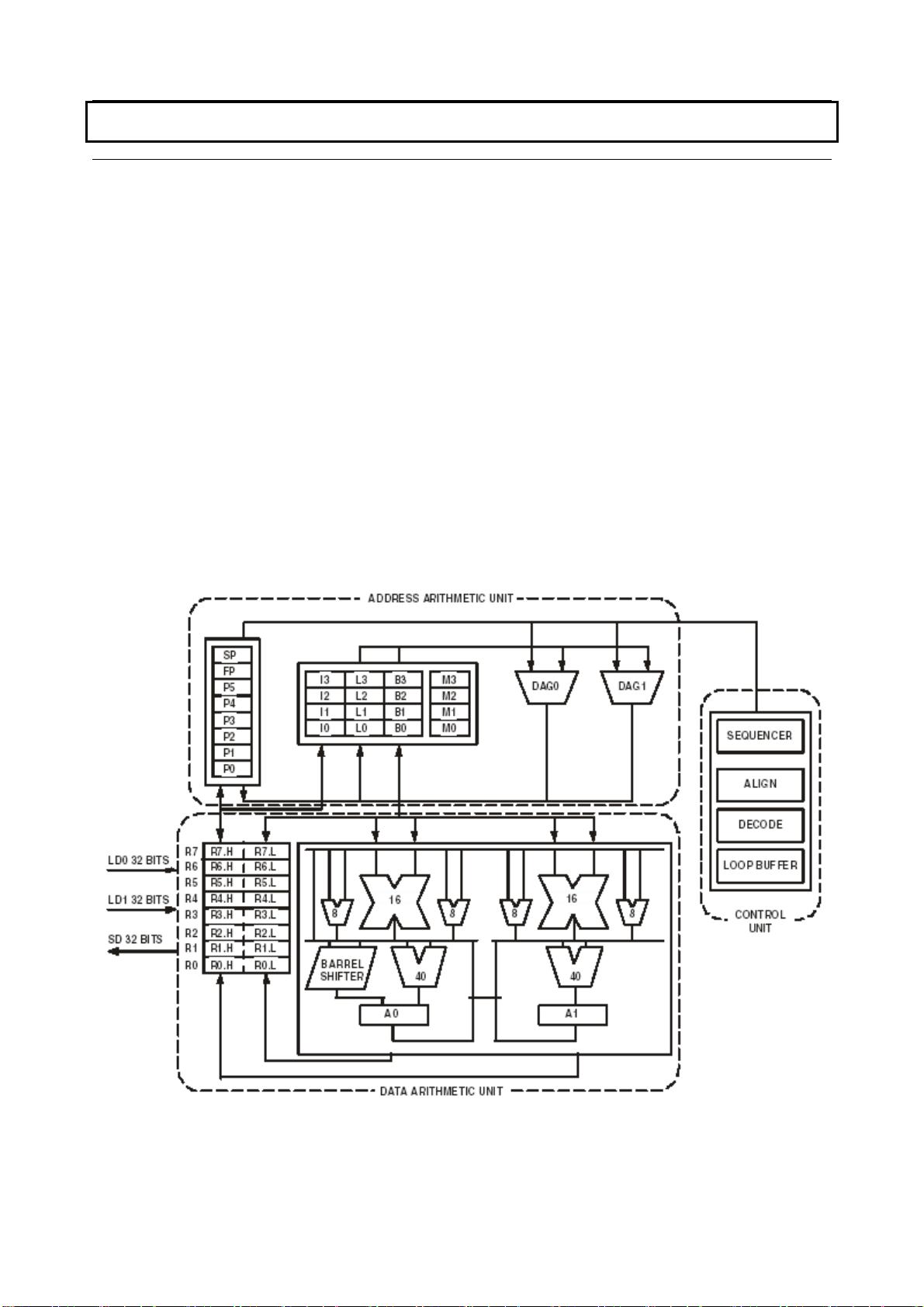

如第 5 页的图 2 所示,BLACKFIN 处理器内核包含 2

个 16 位乘法器,2 个 40 位的累加器,2 个 40 位的 ALU,

4 个视频 ALU 和 1 个 40 位移位器。运算单元处理来自寄

存器组的 8 位、16 位或者 32 位数据。

运算寄存器组包括 8 个 32 位寄存器。当执行 16 位操

作数的运算时,寄存器组可作为 16 个独立的 16 位寄存器。

运算的所有操作数都来自多端口寄存器组和指令常量域。

每个 MAC 每周期可完成一个 16 位乘 16 位的乘法运

算,并把结果累加到 40 位的累加器中。支持符号型和无符

号型数据格式,舍入与饱和等操作。

ALU 除执行一套传统的 16 位或 32 位数据的算术和逻

辑运算外,还包含许多特殊指令用于加速不同的信号处理

任务。这些指令包括位操作(例如域提取和计算总数)、模

2

32

乘法、除法、饱和与舍入、符号/指数检测等;专用的

一套视频指令包括字节对准和压缩操作,16 位和 8 位截断

加,8 位平均操作,8 位减法/绝对值/累加(SAA)操作等;

还提供有比较/选择和矢量搜索指令。

对于某些指令,两个 16 位 ALU 操作可以同时在寄存

器对(运算寄存器的高 16 位和低 16 位)中执行,也可以

使用第二个 ALU,进行四个 16 位运算。

40 位的移位器可以执行移位和循环移位,可以用于标

准化、提取和存储等操作。

程序控制器控制指令执行的顺序,包括指令对准和译

码。对于程序流程,程序控制器支持相对于 PC 的间接条

ADSP-BF531/ADSP-BF532/ADSP-BF533

-4-

件跳转(支持静态分支预测)和子程序调用。硬件提供对

零耗循环的支持。这种结构是完全互锁的,这就意味着,

当有数据相关的指令时,编程者不用自己管理的流水线。

地址算术单元能够提供两套地址,用于从存储器中同

时进行双存取。一个多端口寄存器组由 4 套 32 位的索引、

修改、长度、基地址(用于循环缓冲)寄存器和 8 个另外

的 32 位指针寄存器(用于 C 风格的索引堆栈操作)组成。

Blackfin 处理器采用改进的哈佛结构和分级的存储器

结构。Level 1(L1)存储器一般以全速运行,没有或只有

很少的延迟。在 L1 级,指令存储器只存放指令。2 个数据

存储器存放数据,一个专用的临时数据存储器存放堆栈和

局部变量信息。

此外,由多个 L1 存储器组成的模块,可进行 SRAM

和 CACHE 的混合配置。存储器管理单元(MMU)提供存储

器保护功能,对运行于内核上的独立的任务,可保护系统

寄存器免于意外的存取。

这种体系结构提供了 3 种运行模式:用户模式、管理

员模式和仿真模式。用户模式限制对某些系统资源的访问,

因此提供了一个受保护的软件环境;而管理员模式对系统

和内核资源的访问不受限制。

Blackfin 处理器指令系统经过优化,16 位操作码组成

了最常用的指令,这使得编译后的代码密度非常高。复杂

DSP 指令采用 32 位操作码,体现了多功能指令的全部特

征。Blackfin 处理器支持有限的并行能力,即 1 个 32 位的

指令可以和 2 个 16 位指令并行执行,使编程人员在单指令

周期中使用尽可能多的内核资源。

Blackfin 处理器汇编语言使用易于编程和可读性强的

代数语法,而且在和 C/C++编译器的链接上进行了优化,

给程序员提供了快速有效的软件环境。

存储器结构

ADSP-BF531/2/3 处理器把存储器视为一个统一的

4GBytes 的地址空间,使用 32 位地址。所有的资源,包括

内部存储器、外部存储器和 I/O 控制寄存器,都占据公共

地址空间的各自独立的部分。此地址空间的各部分存储器

按分级结构排列,以提供高的性能价格比。一些非常快速、

低延迟的存储器(如 CACHE 或 SRAM)的位置非常接近

处理器,而更大的低成本、低性能的存储器远离处理器。

参见第 6 页图 3、图 4、图 5。

L1 存储器是 Blackfin 处理器内核中性能最高的最重要

的存储器。通过外部总线接口单元(EBIU),片外存储器可

以由 SDRAM、FLASH 和 SRAM 进行扩展,可以访问多达

132MBytes 的物理存储器。

存储器 DMA 控制器提供高带宽的数据传输能力。它

能够在内部存储器和外部存储器空间之间完成代码或数据

的块传输。

内部(片内)存储器

ADSP-BF531/2/3 处理器有 3 块片内存储器,提供到内

核的高带宽的访问。

第 1 块是 L1 指令存储器, 由高达 80KBytes 的 SRAM

组成,其中 16KBytes 可以配置为一个 4 路组联合的

CACHE。L1 指令存储器以处理器的最快速度访问。

第 2 块片内存储器是 L1 数据存储器,包括分别为

32KBytes 的两个 Bank。每个 Bank 都可配置成 CACHE 或

SRAM。此存储器也以全速度访问。

第 3 块是一个 4KBytes 的临时数据

SRAM,它和 L1

存储器有相同的运行速度,但是只能作为数据 SRAM,不

能配置为 CACHE。

外部(片外)存储器

外部总线接口单元(EBIU)即可以用于异步设备(例如:

FLASH、EPROM、ROM、SRAM 和存储器映射 I/O 设备)

也可以用于同步设备(例如:SDRAM)。它们的总线宽度

均为 16 位,其中 A1 为 16 位字的最低位。8 位的外围设备

必须象 16 位设备一样分配 16 位地址,但只使用其低 8 位

数据。

PC133 兼容的 SDRAM 控制器可以通过编程与高达

128MBytes 的 SDRAM 接口。内部最高可以配有 4 个

SDRAM banks,SDRAM 控制器允许为内部 SDRAM 的每个

banks 同时打开一个通道,从而提高系统性能。

异步存储器的控制器也能够通过编程控制多达 4 个

bank 的时序参数灵活的各种异步存储设备。无论使用设备

的大小如何,每个 bank 的空间都占据 1MByte。这样,只

有装满 4 个 1MByte 的存储器时地址空间才能连续。

I/O 存储器空间

Blackfin 处理器没有定义独立的 I/O 空间。所有的资

源都被映射到统一的 32 位地址空间。片上 I/O 设备的控制

寄存器被映射到靠近 4GByte 地址空间顶端的存储器映射

寄存器(MMR)

地址范围内。这个地址空间又被划分为两个

部分,一部分包含完成所有内核功能的控制 MMR,另一

部分包含用于设置和控制内核以外的片内外设的寄存器。

MMR 仅在管理员模式下可被访问,并且被看作是片内外

设的保留空间。

引导

ADSP-BF531/2/3 处理器包括一个小的引导内核,用于

配置的适当的外设来引导。如果 ADSP-BF531/2/3 处理器

被配置为从引导 ROM 存储器引导,那么 DSP 从片内引导

ROM 开始执行。若需要更多信息,请看第 12 页的引导模

式。

事件处理

ADSP-BF531/2/3 处理器的事件控制器处理到达处理

器的所有的同步和异步事件。事件处理支持嵌套和优先级。

嵌套允许同时激活多个事件的服务程序。优先级保证高优

先级事件的响应可以抢占较低优先级事件的响应。控制器

支持 5 种不同类型的事件:

ADSP-BF531/ADSP-BF532/ADSP-BF533

-5-

1. 仿真:仿真事件使处理器进入仿真模式,允许通过

JTAG 接口命令和控制处理器。

2. 复位:此事件使处理器复位。

3. 不可屏蔽中断(NMI):NMI 事件可以由软件“看门狗”

定时器或者处理器的 NMI 输入信号产生的。NMI 事件

经常用作断电指示,有序地进行系统关闭工作。

4. 异常:异常是与程序执行同步发生的事件,即指令执

行完之前可能会产生异常。例如数据对准违规、未定

义指令等情况都将导致异常。

5. 中断:中断是与程序执行异步发生的事件,由定时器、

外设、输入引脚等引起,也可以由软件指令触发。

每个事件都有一个相应的保存返回地址的寄存器和

一个相应的从事件返回指令。一个事件被触发后,处理器

当前状态被保存在管理员堆栈内。

ADSP-BF531/2/3 处理器的事件控制器包括 2 个部分,

内核事件控制器(CEC)和系统中断控制器(SIC)。内核

事件控制器和系统中断控制器协同工作来控制优先级和控

制所有系统事件。从概念上讲,来自外设的中断进入到

SIC,然后被直接发送到 CEC 的通用中断中处理。

内核事件控制器(CEC)

除专用中断和异常事件外,CEC 还支持 9 个通用中断

(IVG15-7)。这些通用中断中,推荐将优先级最低的 2 个中

断(IVG15-14)留作软件中断,剩下的 7 个优先级中断分别

用于 ADSP-BF531/2/3 处理器的外设。表 2 描述了 CEC 的

事件、事件向量表(EVT)的名称及优先级。

系统中断控制器(SIC)

系统中断控制器为来自多个外设的中断源提供至 CEC

通用中断输入的映射和路由。尽管 ADSP-BF531/2/3 处理

器提供了默认的映射,用户仍可以通过改写中断设置寄存

器(IAR)

的值,来改变中断事件的映射和优先权。表 3 描述

了 SIC 的中断源和至 CEC 的默认映射。

图 2 BLACKFIN 处理器内核