SHARC和SHARC标志均为ADI公司的注册商标。

Rev. C Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

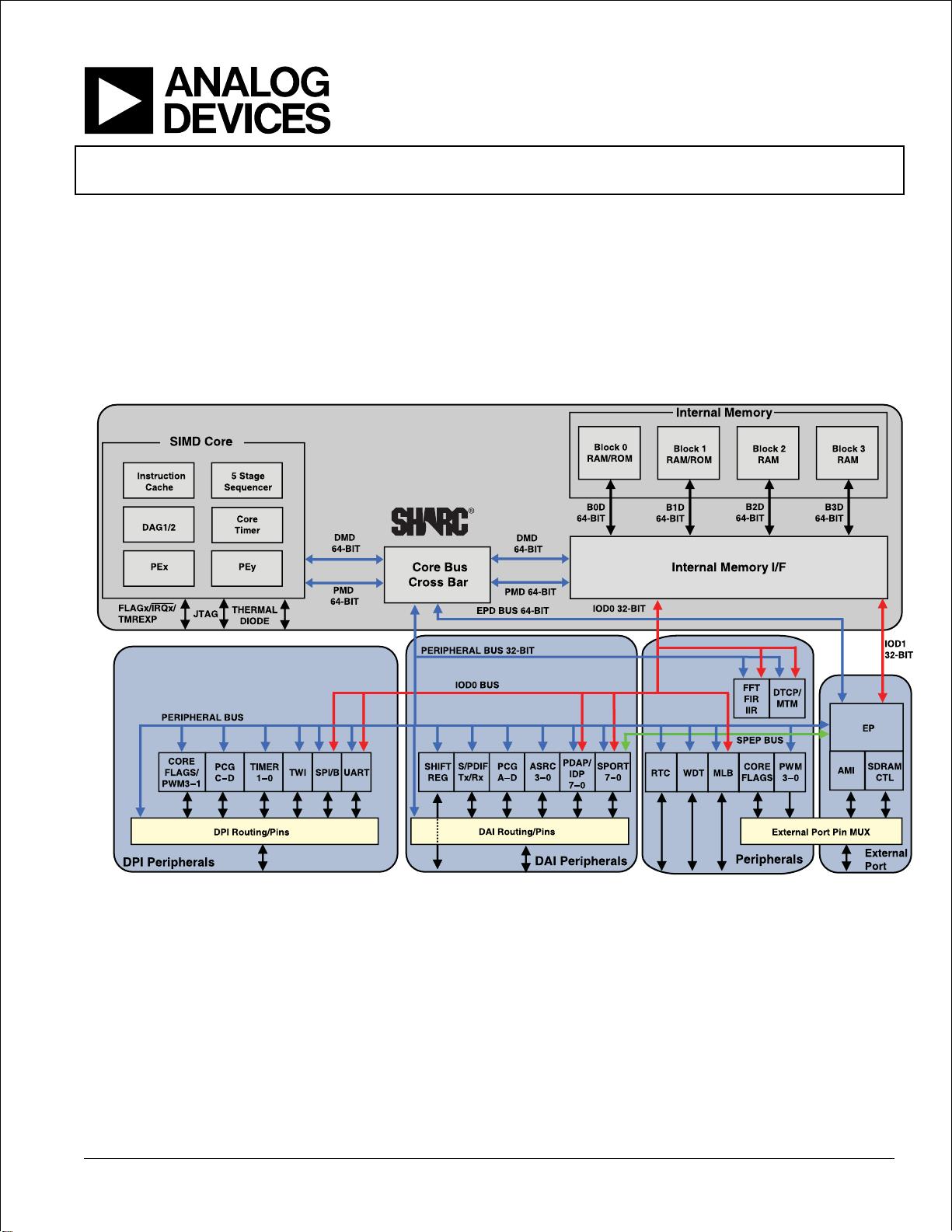

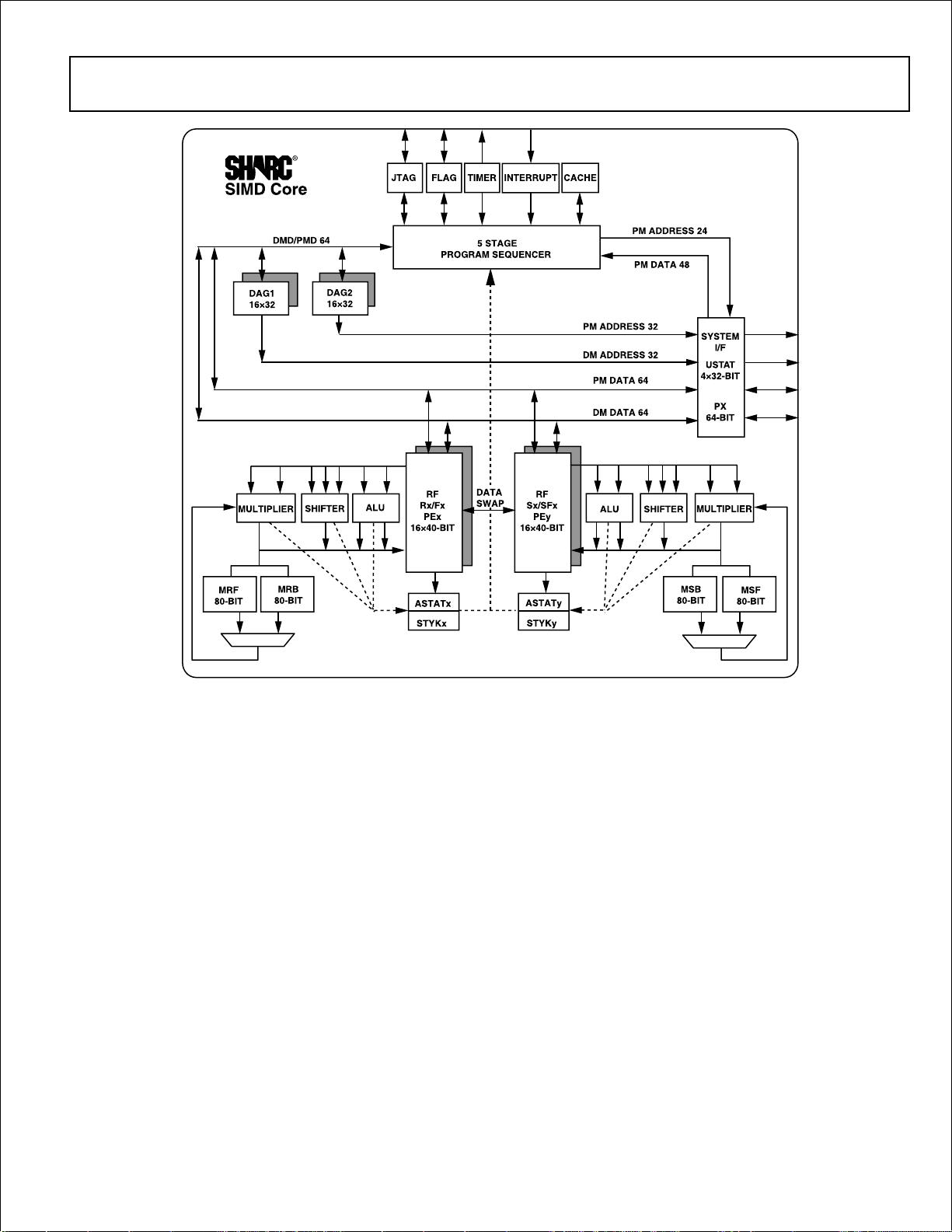

图1. 功能框图

ADSP-21477/ADSP-21478/ADSP-21479

SHARC处理器

摘要

高性能32/40位浮点处理器,针对高性能音频处理进行优化

单指令、多数据(SIMD)计算架构

片内存储器:最多5 Mb片内RAM,4 Mb片内ROM

工作频率高达300 MHz

通过汽车应用认证。参见第75页的汽车应用产品

与SHARC系列的所有其它产品代码兼容

ADSP-2147x处理器提供以音频中心的独特外设,例如:数字

应用接口、串行端口、精密时钟发生器、S/PDIF收发器、

异步采样速率转换器、输入数据端口等。

工厂编程的ROM版本包含Dolby和DTS的最新音频解码器,可供

IP授权用户使用。详细订购信息请参阅第76页的订购指南。

Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Technical Support www.analog.com

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供

的最新英文版数据手册。

Rev. C | Page 2 of 76 | July 2013

目录

摘要.................................................................................................. 1

概述.................................................................................................. 3

系列内核架构........................................................................... 4

系列外设架构........................................................................... 8

I/O处理器特性 ....................................................................... 12

系统设计.................................................................................. 13

开发工具.................................................................................. 13

其他信息.................................................................................. 15

相关信号链 ............................................................................. 15

引脚功能描述 .............................................................................. 16

技术规格....................................................................................... 21

工作条件.................................................................................. 21

电气特性.................................................................................. 22

最大功耗.................................................................................. 24

封装信息.................................................................................. 24

产品应用限制

不得用于活体内体液成分监控应用,包括监控形成、组成

或污染人体血液或其他体液的一种或多种成分,包括但不

限于碳氧血红蛋白、正铁总血红蛋白、血氧饱和度、血氧

含量、脉搏血氧饱和度、胆红素、葡萄糖、药物、脂质、

水、蛋白质和酸碱度。

ESD灵敏度 .............................................................................. 24

绝对最大额定值..................................................................... 24

时序规格.................................................................................. 25

输出驱动电流......................................................................... 65

测试条件.................................................................................. 65

容性负载.................................................................................. 65

热特性 ...................................................................................... 66

88-LFCSP_VQ引脚分配............................................................. 68

100引脚LQFP_EP引脚分配 ...................................................... 70

196引脚BGA引脚分配 ............................................................... 72

外形尺寸....................................................................................... 73

表贴设计.................................................................................. 75

汽车应用级产品..................................................................... 75

订购指南....................................................................................... 76

修订历史

2013年7月—修订版B至修订版C

更新开发工具 .............................................................................. 13

更改引脚功能描述中的MS

1-0

引脚描述和V

DD_RTC

引脚

描述................................................................................................ 16

将电气特性中的参数I

DD-INTYP

纠正为I

DD_INT

............................22

更改总功耗描述...........................................................................23

AMI读取中的表32增加尾注3 ...................................................37

更改脉宽调制发生器(PWM)中表43的最大值......................51

纠正88-LFCSP_VQ引脚分配中表61的下列引脚名称 .........68

• CLK_CFG_1改为CLK_CFG1

• BOOTCFG_0改为BOOT_CFG0

• BOOTCFG_1改为BOOT_CFG1

• CLK_CFG_0改为CLK_CFG0

• XTAL2改为XTAL

更新外形尺寸中88引脚LFCSP和100引脚LQFP_EP的封装外

形图................................................................................................ 73

在汽车应用级产品中增加车用型号,并纠正表64(车用产品

型号)中的型号............................................................................. 75

欲浏览与本修订版数据手册有关的产品/工艺变更通知

(PCN),请访问www.analog.com网站上的处理器产品页

面,并点击“查看PCN”链接。

ADSP-21477/ADSP-21478/ADSP-21479

Rev. C | Page 3 of 76 | July 2013

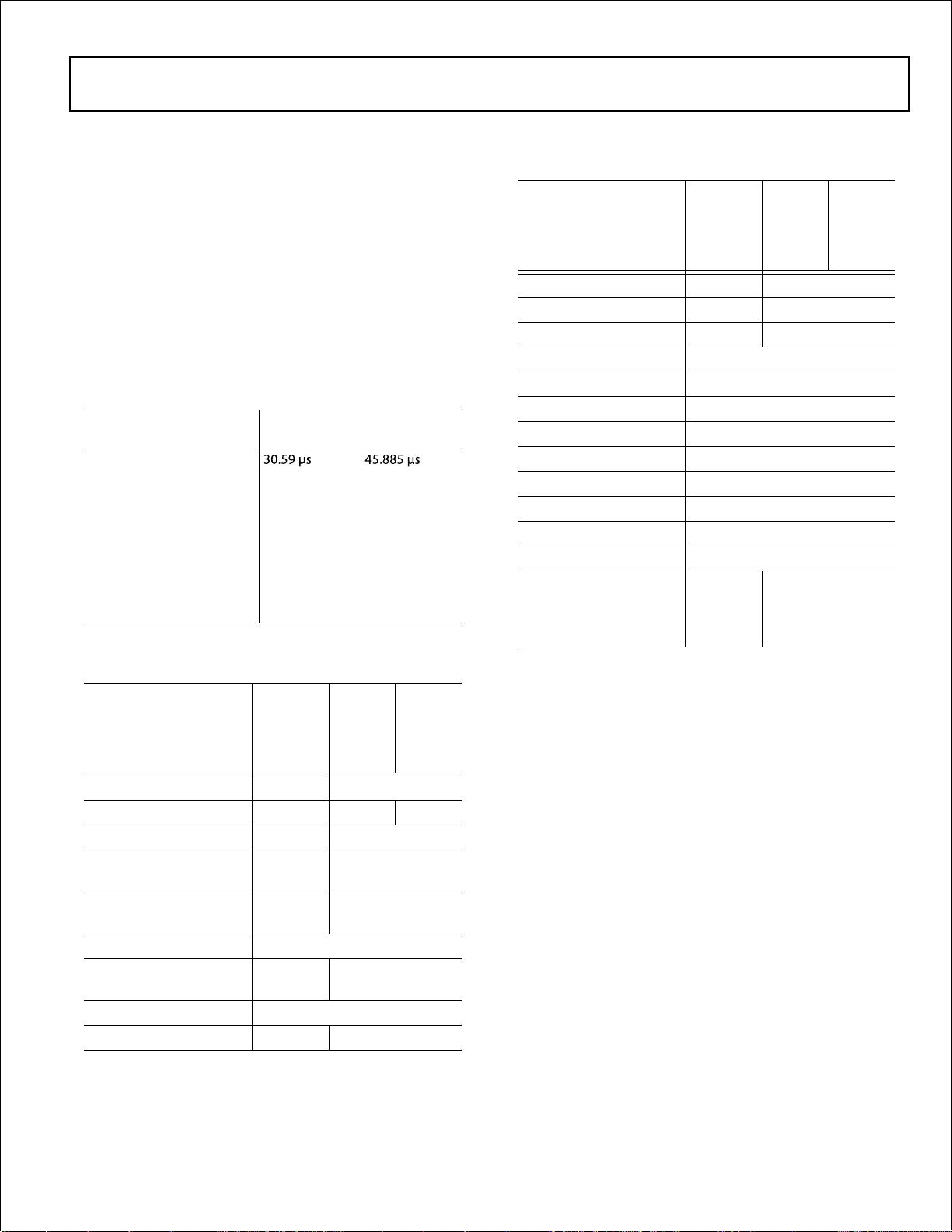

表1. 处理器基准

基准算法

速度

(300 MHz时)

速度

(200 MHz时)

1024点复数FFT

(基4,带翻转)

FIR滤波器(每抽头)

1

1.66 ns 2.49 ns

IIR滤波器(每双二阶

)

1

6.65 ns 9.975 ns

矩阵乘法(流水线)

[3 × 3] × [3 × 1]

[4 × 4] × [4 × 1]

14.99 ns

26.66 ns

22.485 ns

39.99 ns

11.61 ns 17.41 ns

18.08 ns 27.12 ns

除法(y/×)

平方根倒数

表2. ADSP-2147x系列特性

特性

频率

ADSP-21477

ADSP-21478

ADSP-21479

200 MHz 高达300 MHz

5Mb 3Mb2Mb

3

MAR

4Mb

是

有(16-bit)

A/NMOR

脉冲宽度调制

4单元(3个在

100引脚封装中)

外部端口接口(SDRAM、

AMI

)

1

否

8

是

串行端口

从SPORT到外部存储器均

直接DMA

否

否

FIR、IIR、FFT加速器

MediaLB接口 仅汽车应用型号

看门狗定时器

2

否

实时时钟

2, 3

否

移位寄存器

2

否

是

是

是

是IDP/PDAP

1UART

DAI (SRU)/DPI (SRU2)

1S/PDIF收发器

2IPS

1

–128 dB

IWT

SRC SNR性能

20/14引脚

热二极管

4

是

是VISA支持

封装

1

100引脚

LQFP、

88引脚

LFCSP_VQ

196引脚 CSP_BGA、

100引脚 LQFP、

88引脚 LFCSP_VQ

表2. ADSP-2147x系列特性(续)

特性

ADSP-21477

ADSP-21478

ADSP-21479

概述

ADSP-2147x SHARC®处理器属于SIMD SHARC系列DSP,采

用ADI公司的Super Harvard架构。处理器与ADSP-2126x、

ADSP-2136x、ADSP-2137x、ADSP-2146x和ADSP-2116x

DSP以及SISD(单指令流-单数据流)模式的第一代ADSP-

2106x SHARC处理器源代码兼容。这些处理器为32/40位浮

点处理器,针对高性能音频应用进行了优化,具有大容量

片内SRAM,多条内部总线可消除I/O瓶颈,并且提供创新

的数字应用接口(DAI)。

表1给出了ADSP-2147x处理器的性能基准。表2显示了每款

产品的特性。

图1显示了构成ADSP-2147x处理器的两个时钟域(内核和

I/O处理器)。内核时钟域包含以下特性:

• 两个处理元件(PEx、PEy),各元件均由ALU、乘法

器、移位器和数据寄存器文件组成

• 两个数据地址发生器(DAG1、DAG2)

• 一个带指令缓存的程序序列器

• PM和DM总线,支持存储器与内核之间在每个内核

处理器周期传输2x64位数据

• 一个带引脚排列的周期性间隔定时器

• 片内SRAM (最多5 Mb)

• 一个用于仿真和边界扫描的JTAG测试访问端口。

JTAG通过用户断点提供软件调试功能,支持灵活的

异常处理。

1

假定多通道SIMD模式下有两个文件。

1

处理器的100引脚和88引脚封装不含外部端口。使用此封装时,SDRAM

控制器引脚必须禁用。更多信息请参阅第17页的引脚功能描述。

2

仅限196引脚CSP_BGA封装提供。

3

仅温度范围为0°C至+70°C的产品支持实时时钟(RTC),所有其它温度等

级的产品均不支持。

4

仅限88引脚和100引脚封装提供。

ADSP-21477/ADSP-21478/ADSP-21479

Rev. C | Page 4 of 76 | July 2013

图1所示ADSP-2147x框图还显示了外设时钟域(也称为I/O

处理器),它包含以下特性:

• 用于32位数据传输的IOD0(外设DMA)和IOD1(外部端

口DMA)总线

• 用于内核连接的外设和外部端口总线

• 带异步存储器接口(AMI)和SDRAM控制器的外部端口

• 4个脉冲宽度调制(PWM)控制单元

• 1个用于内部到内部存储器传输的存储器到存储器

(MTM)单元

• 数字应用接口,包括4个精密时钟发生器(PCG)、1个

用于串行和并行互连的输入数据端口(IDP/PDAP)、1个

S/PDIF接收器/发送器、4个异步采样速率转换器、8个串

行端口、1个移位寄存器和1个灵活的信号路由单元

(DAI SRU)。

• 数字外设接口,包括2个定时器、1个双线式接口、1个

UART、2个串行外设接口(SPI)、2个精密时钟发生器

(PCG)、3个脉宽调制(PWM)单元和1个灵活的信号路

由单元(DPI SRU)。

如第5页的SHARC内核框图所示,该系列处理器采样两个

计算单元,相对于以前的SHARC处理器,其处理各种DSP

算法的性能有了显著提高。利用SIMD计算硬件并以300 MHz

速率运行时,该系列处理器能够执行1.8 GFLOPS。

系列内核架构

处理器与ADSP-2146x、 ADSP-2137x、 ADSP-2136x、

ADSP-2126x、ADSP-21160、ADSP-21161及第一代ADSP-

2106x SHARC处理器在汇编水平上代码兼容。ADSP-2147x

与ADSP-2126x、ADSP- 2136x、ADSP-2137x、ADSP-2146x、

ADSP-2116x SIMD SHARC处理器具有相同的架构特性,如

图2所示,详见以下部分的说明。

SIMD计算引擎

处理器包含两个用作单指令、多数据(SIMD)引擎的计算处

理器元件,分别称为PEX和PEY,各元件均由ALU、乘法

器、移位器和寄存器文件组成。PEX始终有效,PEY可通

过将MODE1寄存器的PEYEN模式位设为1来使能。SIMD

模式允许处理器在两个处理元件中执行同一指令,但各处

理元件处理不同的数据。这种架构对于执行计算密集型

DSP算法非常有效。

SIMD模式也会影响数据在存储器与处理元件之间的传输

方式,因为为了支持处理元件的计算操作,需要两倍的数

据带宽。所以,进入SIMD模式时,存储器与处理元件之

间的带宽也会加倍。在SIMD模式下使用DAG传输数据

时,每次存储器或寄存器文件访问传输两个数据值。

外部SDRAM支持SIMD模式,但AMI不支持。

独立并行计算单元

各处理元件内部有一组计算单元。计算单元由算术/逻辑单

元(ALU)、乘法器和移位器组成。这些单元在单一周期内

执行所有操作。这三个单元在每个处理元件内并行排列,

从而使计算吞吐速率达到最大。单一多功能指令执行并行

ALU和乘法器操作。在SIMD模式下,并行ALU和乘法器操

作同时在两个处理元件中进行。这些计算单元支持IEEE 32

位单精度浮点、40位扩展精度浮点和32位定点数据格式。

定时器

处理器包含一个内核定时器,用于产生周期性软件中断。

内核定时器可以配置为利用FLAG3作为定时器到期信号。

数据寄存器文件

每个处理元件均包含一个通用数据寄存器文件。该寄存器

文件用于在计算单元与数据总线之间传输数据,以及存储

即时结果。这些10端口、32寄存器(16个主要寄存器、16个

辅助寄存器)寄存器文件加上处理器的增强Harvard架构,

实现了计算单元与内部存储器之间不受限制的数据流动。

PEX中的寄存器称为R0至R15,PEY中称为S0至S15。

上下文切换

处理器的许多寄存器都有辅助寄存器,在中断处理期间可

以将其激活以实现快速上下文切换。寄存器文件中的数据

寄存器、DAG寄存器以及乘法器结果寄存器均有辅助寄存

器。主要寄存器在复位时有效,辅助寄存器则是通过模式

控制寄存器中的控制位激活。

通用寄存器

通用寄存器可用于一般任务。USTAT (4)寄存器可以对所有

外设控制和状态寄存器轻松进行位操作(置1、清0、反转、

测试、XOR)。

数据总线交换寄存器(PX)允许数据在64位PM数据总线与64

位 DM数据总线之间传送,或者在40位寄存器文件与

PM/DM数据总线之间传送。这些寄存器包含用来处理数

据宽度差异的硬件。

单周期获取1个指令和4个操作数

处理器采用增强的Harvard架构,数据存储器(DM)总线传

输数据,程序存储器(PM)总线传输指令和数据(见图2)。利

用独立的程序和数据存储器总线以及片内指令缓存,处理

器可以在一个周期内同时获取4个操作数(每条数据总线2个)

和1个指令。

ADSP-21477/ADSP-21478/ADSP-21479

Rev. C | Page 5 of 76 | July 2013

图2. SHARC内核框图

指令缓存

处理器含有一个片内指令缓存,支持三总线操作以获取一

个指令和四个数据值。缓存是选择性的,只有这样的指令

才会被缓存:指令获取与PM总线数据存取冲突。此缓存

支持全速执行内核环路操作,如数字滤波器乘加和FFT蝴

蝶处理等。

带零开销硬件环形缓冲器支持的数据地址发生器

处理器的两个数据地址发生器(DAG)用于间接寻址以及环

形数据缓冲器的硬件实现。环形缓冲器支持对数字信号处

理所需的延迟线和其它数据结构进行高效编程,常用于数

字滤波器和傅里叶变换。处理器的两个DAG包含足够的寄

存器,最多可以创建32个环形缓冲器(16个主要寄存器集、

16个辅助寄存器集)。DAG自动处理地址指针回绕,可降

低开销、提高性能并简化实现。环形缓冲器可以在任何寄

存器位置开始和结束。

灵活的指令集

48位指令字支持各种并行操作,可实现简练编程。例如,

处理器可以有条件地在两个处理元件中执行乘法、加法和

减法,同时进行分支并从存储器获取最多4个32位数据值,

所有这些只需一个指令。

可变指令集架构(VISA)

除了支持源自上一代SHARC处理器的标准48位指令以外,

处理器还支持新的16位和32位指令。此特性称为可变指令

集架构(VISA),48位指令中的冗余/无用位被删除,从而使

代码更有效、更紧凑。程序序列器支持从内部和外部

SDRAM存储器获取这些16位和32位指令。此支持未扩展到

异步存储器接口(AMI)。为使代码生成工具能够产生更高

效的操作码,源模块需要利用VISA选项构建。

ADSP-21477/ADSP-21478/ADSP-21479