Vivado集成开发环境时序约束介绍.docx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

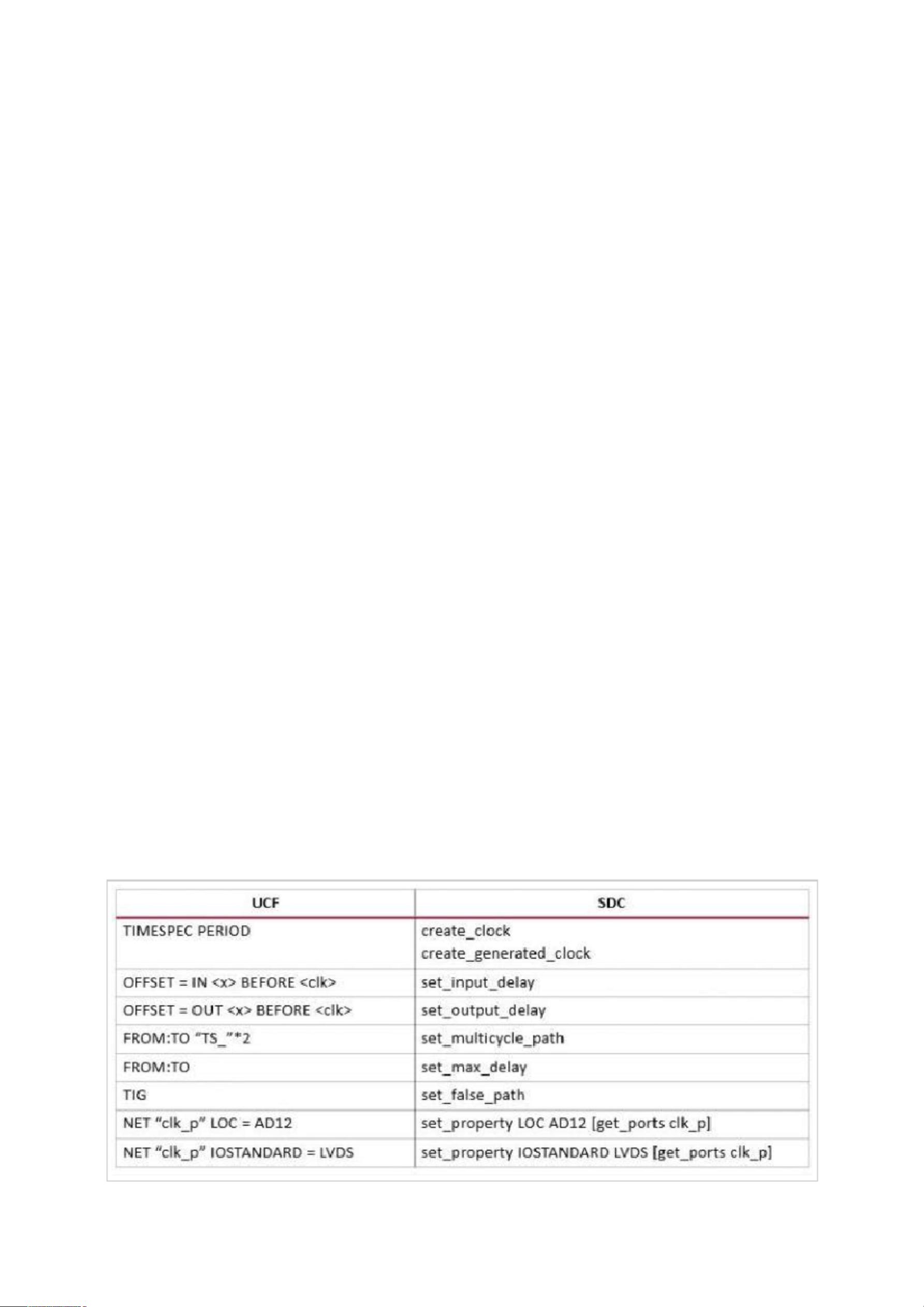

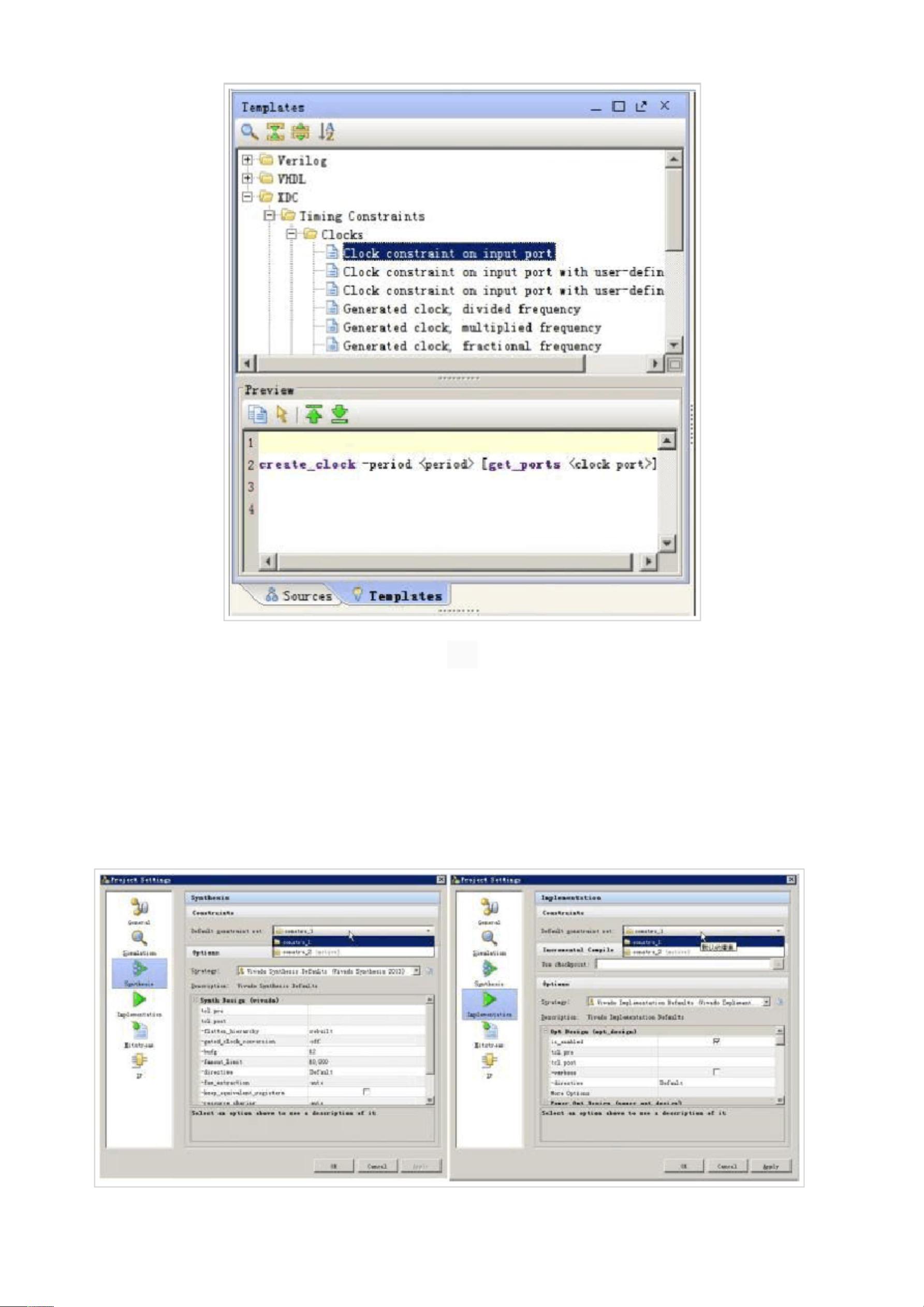

Vivado集成开发环境中的时序约束是设计高效、可靠数字电路的关键步骤,尤其是在 FPGA 开发中。Vivado 设计套件引入了 Xilinx Design Constraints (XDC) 文件格式,取代了传统的 User Constraints File (UCF),以更接近业界标准的 Synopsys Design Constraints (SDC) 标准。这一变化使得在不同EDA工具之间转换设计变得更加顺畅,例如从Altera的TimeQuest到Xilinx的Vivado。 SDC 是一种广泛采用的设计约束格式,用于描述合成、时钟、时序、电源、测试以及环境和操作条件的“设计意图”。它的应用已超过20年,是描述设计约束最流行和经过验证的格式。几乎所有的综合设计都使用 SDC,许多EDA公司都有能读取和处理 SDC 的转换器。 在 UCF 和 XDC 之间转换,主要的区别包括: 1. XDC 支持顺序执行约束,这意味着每个约束指令具有优先级,这允许更精细的控制。 2. UCF 通常约束网络(nets),而 XDC 约束的对象可以是引脚(pins)、端口(ports)和单元(cells),提供了更精确的定位。 3. UCF 不默认分析异步时钟路径的时序,而在 XDC 中,所有时钟默认相关,会分析所有路径。如果需要,可以使用 `set_clock_groups` 命令来取消时钟间的相关性。 在Vivado中添加和管理 XDC 文件的步骤如下: 1. 在 Project Manager 中,展开 Constraints 类别。 2. 使用 Add Sources 功能添加现有的 XDC 文件或创建新的 XDC 文件。 3. 双击新添加的 XDC 文件,在文本编辑器中,可以选择左侧的 Templates,这里包含了各种 XDC 约束命令的示例,方便开发者快速引用和编写约束。 举例来说,时钟周期约束在 UCF 中用 `TIMESPEC` 命令定义,而在 XDC 中则通过 `create_clock` 命令完成。输入和输出端口的延迟约束也可以分别通过 `OFFSET`(UCF)和 `set_input_delay` / `set_output_delay`(XDC)命令设定。这些命令在 XDC 中提供了更灵活的配置方式,比如可以指定时钟波形和特定的时钟边沿。 Vivado 中的 XDC 提供了一种更强大且标准化的方式来管理时序约束,使得设计者能够更精确地控制 FPGA 中的逻辑行为,确保设计满足性能和时序要求。理解和熟练掌握 XDC 文件的编写是Vivado 用户必须具备的技能,它对于优化设计性能、提高系统稳定性以及降低设计风险至关重要。

剩余80页未读,继续阅读

- 粉丝: 4042

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功