没有合适的资源?快使用搜索试试~ 我知道了~

TI-TL16C554A.pdf

温馨提示

试读

49页

UART收发器

资源推荐

资源详情

资源评论

TL16C554A, TL16C554AI

ASYNCHRONOUS-COMMUNICATIONS ELEMENT

SLLS509E − AUGUST 2001 − REVISED JUNE 2010

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D Integrated Asynchronous-Communications

Element

D Consists of Four Improved TL16C550C

ACEs Plus Steering Logic

D In FIFO Mode, Each ACE Transmitter and

Receiver Is Buffered With 16-Byte FIFO to

Reduce the Number of Interrupts to CPU

D In TL16C450 Mode, Hold and Shift

Registers Eliminate Need for Precise

Synchronization Between the CPU and

Serial Data

D Up to 16-MHz Clock Rate for up to 1-Mbaud

Operation with V

CC

= 3.3 V and 5 V

D Programmable Baud-Rate Generators

Which Allow Division of Any Input

Reference Clock by 1 to (2

16

−1) and

Generate an Internal 16 × Clock

D Adds or Deletes Standard Asynchronous

Communication Bits (Start, Stop, and

Parity) to or From the Serial-Data Stream

D Independently Controlled Transmit,

Receive, Line Status, and Data Set

Interrupts

D 5-V and 3.3-V Operation

D Fully Programmable Serial Interface

Characteristics:

− 5-, 6-, 7-, or 8-Bit Characters

− Even-, Odd-, or No-Parity Bit

− 1-, 1 1/2-, or 2-Stop Bit Generation

− Baud Generation (DC to 1-Mbit Per

Second)

D False Start Bit Detection

D Complete Status Reporting Capabilities

D Line Break Generation and Detection

D Internal Diagnostic Capabilities:

− Loopback Controls for Communications

Link Fault Isolation

− Break, Parity, Overrun, Framing Error

Simulation

D Fully Prioritized Interrupt System Controls

D Modem Control Functions (CTS, RTS, DSR,

DTR

, RI, and DCD)

D 3-State Outputs Provide TTL Drive

Capabilities for Bidirectional Data Bus and

Control Bus

D Programmable Auto-RTS and Auto-CTS

D CTS Controls Transmitter in Auto-CTS

Mode,

D RCV FIFO Contents and Threshold Control

RTS

in Auto-RTS Mode,

description

The TL16C554A is an enhanced quadruple version of the TL16C550C asynchronous-communications element

(ACE). Each channel performs serial-to-parallel conversion on data characters received from peripheral

devices or modems and parallel-to-serial conversion on data characters transmitted by the CPU. The complete

status of each channel of the quadruple ACE can be read by the CPU at any time during operation. The

information obtained includes the type and condition of the operation performed and any error conditions

encountered.

The TL16C554A quadruple ACE can be placed in an alternate FIFO mode, which activates the internal FIFOs

to allow 16 bytes (plus three bits of error data per byte in the receiver FIFO) to be stored in both receive and

transmit modes. In the FIFO mode of operation, there is a selectable autoflow control feature that can

significantly reduce software overhead and increase system efficiency by automatically controlling serial-data

flow using RTS

output and CTS input signals. All logic is on the chip to minimize system overhead and maximize

system efficiency. Two terminal functions allow signaling of direct-memory access (DMA) transfers. Each ACE

includes a programmable baud-rate generator that can divide the timing reference clock input by a divisor

between 1 and 2

16

−1.

The TL16C554A is available in a 68-pin plastic-leaded chip-carrier (PLCC) FN package, 64-pin plastic quad

flatpack (PQFP) PM package and in an 80-pin (TQFP) PN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright © 2010, Texas Instruments Incorporated

TL16C554A, TL16C554AI

ASYNCHRONOUS-COMMUNICATIONS ELEMENT

SLLS509E − AUGUST 2001 − REVISED JUNE 2010

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

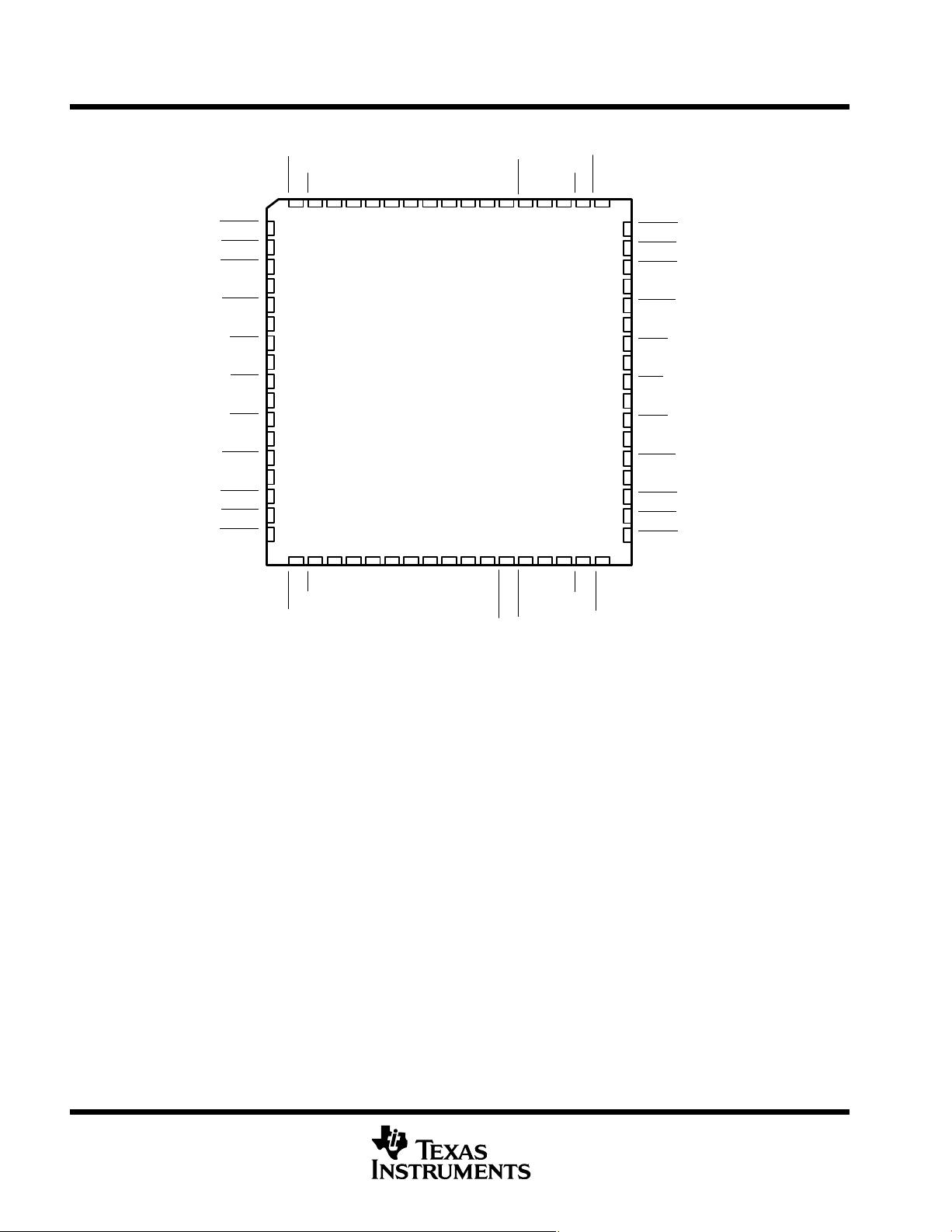

28 29

DSRD

CTSD

DTRD

GND

RTSD

INTD

CSD

TXD

IOR

TXC

CSC

INTC

RTSC

V

CC

DTRC

CTSC

DSRC

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

30

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

DSRA

CTSA

DTRA

V

CC

RTSA

INTA

CSA

TXA

IOW

TXB

CSB

INTB

RTSB

GND

DTRB

CTSB

DSRB

31 32 33 34

FN PACKAGE

(TOP VIEW)

D2

D1

87 6 5493

RXA

GND

D7

D6

D5

D4

D3

XTAL2

RESET

RXRDY

TXRDY

RXB

NC

A2

A1

A0

XTAL1

168672

35 36 37 38 39

66 65

27

DCDB

D0

INTN

64 63 62 61

40 41 42 43

GND

RXC

RIC

DCDC

RXD

RID

DCDD

DCDA

RIA

V

CC

RIB

V

CC

NC − No internal connection

TL16C554A, TL16C554AI

ASYNCHRONOUS-COMMUNICATIONS ELEMENT

SLLS509E − AUGUST 2001 − REVISED JUNE 2010

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

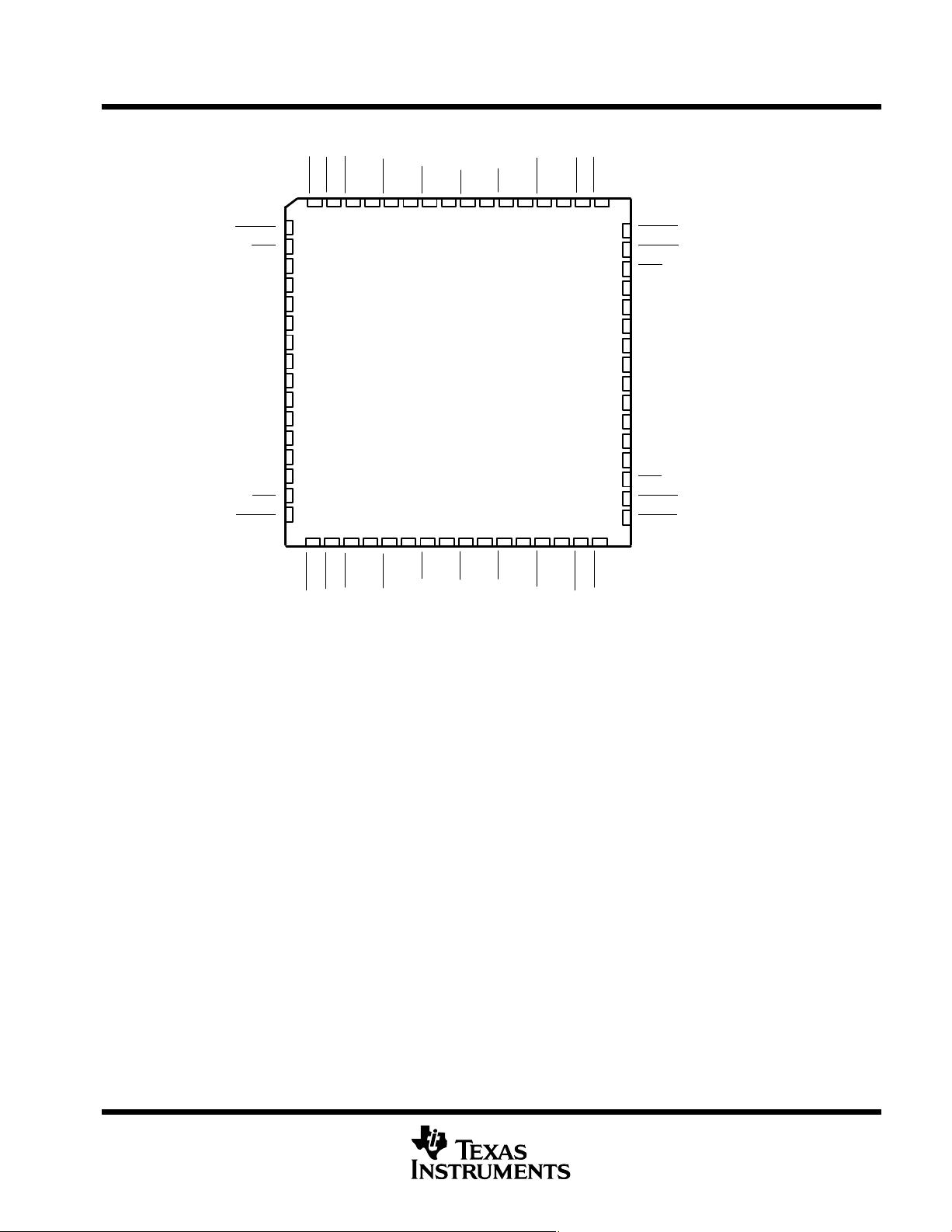

23

DSRC

DCDC

RIC

RXC

GND

RESET

XTAL2

XTAL1

A0

A1

A2

V

CC

RXB

RIB

DCDB

DSRB

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

4

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

DCDD

RID

RXD

V

CC

D0

D1

D2

D3

D4

D5

D6

D7

GND

RXA

RIA

DCDA

5678

PM PACKAGE

(TOP VIEW)

TXC

CSC

47 46 45 44 4348 42

DTRD

GND

RTSD

INTD

CSD

TXD

IOR

TXB

CSB

INTB

RTSB

DTRA

RTSA

INTA

CSA

TXA

IOW

40 39 3841

910111213

37 36

1

DSRA

INTC

RTSC

35 34 33

14 15 16

GND

DTRB

CTSB

DTRC

CTSC

DSRD

CTSD

V

CC

CTSA

V

CC

NC − No internal connection

TL16C554A, TL16C554AI

ASYNCHRONOUS-COMMUNICATIONS ELEMENT

SLLS509E − AUGUST 2001 − REVISED JUNE 2010

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

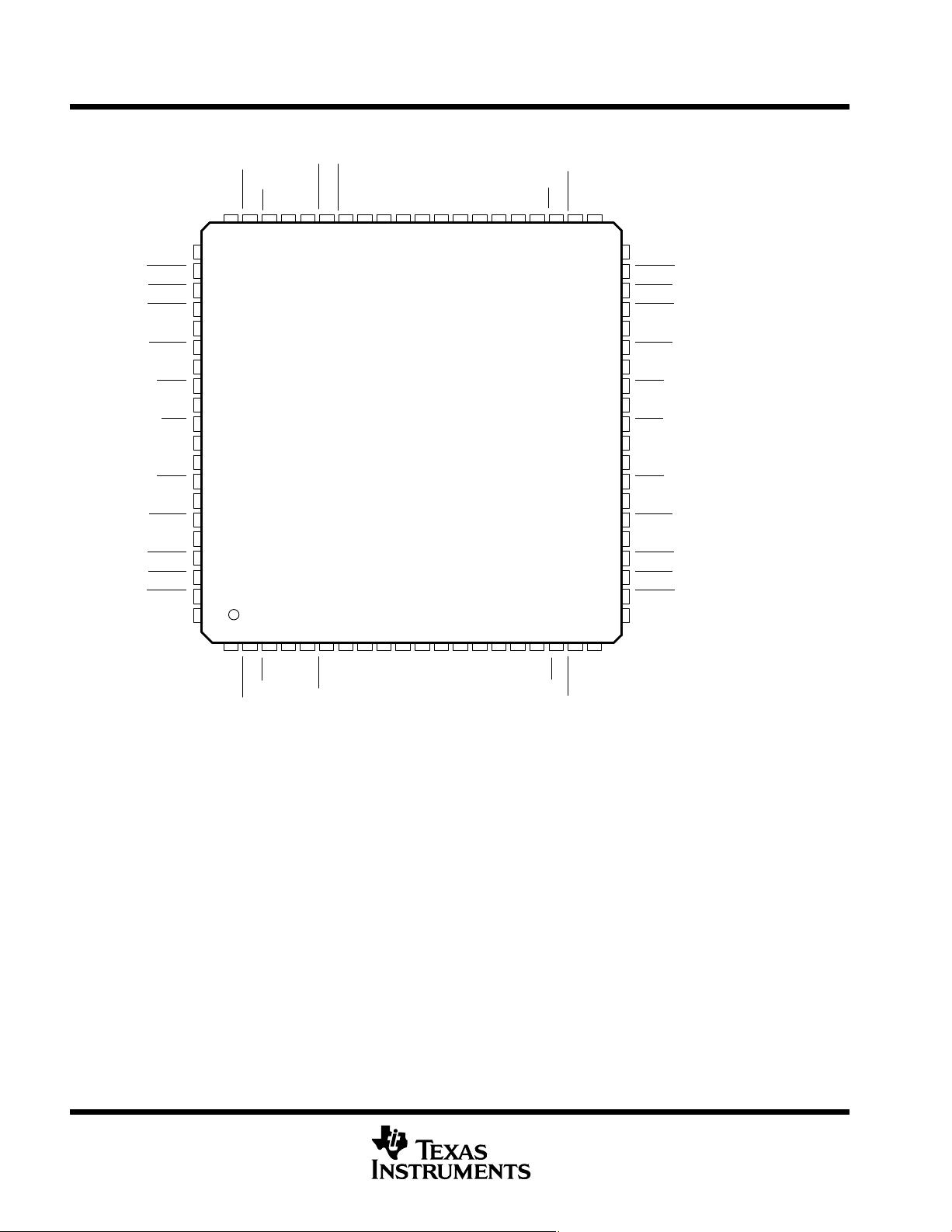

23

NC

DSRB

CTSB

DTRB

GND

RTSB

INTB

CSB

TXB

IOW

NC

TXA

CSA

INTA

RTSA

V

CC

DTRA

CTSA

DSRA

NC

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

4

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

NC

DSRC

CTSC

DTRC

V

CC

RTSC

INTC

CSC

TXC

IOR

NC

TXD

CSD

INTD

RTSD

GND

DTRD

CTSD

DSRD

NC

5678

PN PACKAGE

(TOP VIEW)

XTAL1

59 58 57 56 5560 54

RIC

RXC

GND

TXRDY

RXRDY

RESET

NC

D3

D5

RID

RXD

NC

INTN

D0

D1

D2

52 51 5053

9

10 11 12 13

49 48

1

NC

A0

47 46 45 44

14 15 16 17

D6

D7

GND

RXA

A1

A2

XTAL2

RXB

NC

DCDC

RIA

DCDA

18 19 20

RIB

DCDB

43 42 41

V

CC

NC

NC

CC

V

DCDD

D4

NC

NC − No internal connection

TL16C554A, TL16C554AI

ASYNCHRONOUS-COMMUNICATIONS ELEMENT

SLLS509E − AUGUST 2001 − REVISED JUNE 2010

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

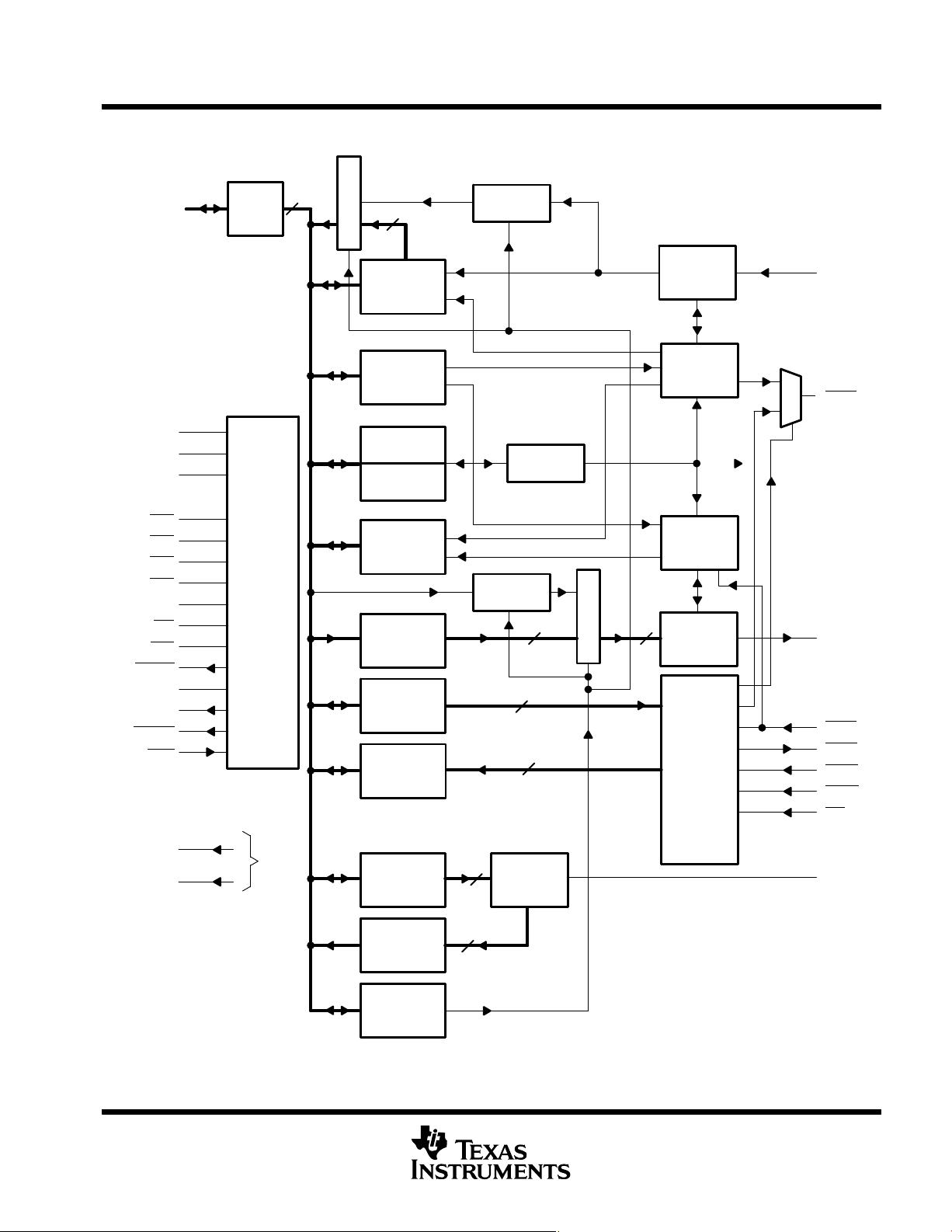

functional block diagram (per channel)

Receiver

Buffer

Register

Divisor

Latch (LS)

Divisor

Latch (MS)

Baud

Generator

Receiver

FIFO

Line

Status

Register

Transmitter

Holding

Register

Modem

Control

Register

Modem

Status

Register

Line

Control

Register

Transmitter

FIFO

Interrupt

Enable

Register

Interrupt

Identification

Register

FIFO

Control

Register

Select

and

Control

Logic

Interrupt

Control

Logic

S

e

l

e

c

t

Data

Bus

Buffer

RXA

TXA

CTSA

DTRA

DSRA

DCDA

RIA

INTA

11

12

10

9

8

15

17

7

16

A0

34

D(7 −0)

5 − 66

Internal

Data

Bus

33

32

20

50

54

37

52

18

39

35

36

38

65

A1

A2

CSA

CSB

CSC

CSD

RESET

IOR

IOW

XTAL1

RXRDY

S

e

l

e

c

t

Receiver

Shift

Register

Receiver

Timing and

Control

Transmitter

Timing and

Control

Transmitter

Shift

Register

Modem

Control

Logic

8

13, 30, 47, 64

6, 23, 40, 57

V

CC

GND

Power

Supply

RTSA

14

Autoflow

Control

(AFE)

8

8

8

8

8

8

8

TXRDY

XTAL2

INTN

NOTE A: Terminal numbers shown are for the FN package and channel A.

剩余48页未读,继续阅读

资源评论

qq_335607272023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

qq_335607272023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 m0_745259962023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

m0_745259962023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 CSDN_1872023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

CSDN_1872023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 2301_763960562023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

2301_763960562023-02-13#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

不觉明了

- 粉丝: 3102

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功