没有合适的资源?快使用搜索试试~ 我知道了~

TI-TS5V522C.pdf

需积分: 9 0 下载量 116 浏览量

2022-12-01

23:43:23

上传

评论 4

收藏 1.16MB PDF 举报

温馨提示

试读

21页

TI-TS5V522C.pdf

资源推荐

资源详情

资源评论

OE

AR

1R

2R

BR

AG

1G

2G

BG

AB

1B

GND

V

CC

BSCL

2SCL

1SCL

ASCL

BSCA

2SCA

1SCA

ASCA

BB

2B

SEL

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

TS5V522C

www.ti.com.cn

ZHCS156 –MARCH 2011

支持双通道

VGA 源极至汲极的 5 V、5 位视频交换开关 低导通电阻的 -2 V 下冲保护

查 询 样 品

: TS5V522C

1

特性

应用

• 双向数据流,支持近零传播延迟 • 数字及模拟信号接口

• 高带宽、380MHZ(典型值)RGB 开关 • 音频与视频信号接口

• 低导通阻抗 (ron) 特性(ron = 3 Ω 典型值) • 高速信号总线交换

• 低输入/输出电容可最大限度地减少加载与信号失 • 总线隔离与交错

真(CIO(OFF) = 8pF 典型值)

• 笔记本电脑图形控制

• 数据与控制输出上的下冲钳位二极管

• 低功耗(Icc = 3uA 最大值)

• Vcc 工作范围 4 V 至 5.5 V

• 数据 I/O 支持 0 至 5 V 信号级(0.8 V、1.2 V、1.5

V、1.8 V、2.5 V、3.3 V、4 V)

• 可在 I/O 上实施高达 5 V 的上拉电阻器

• I

off

支持带电插入、局部关断模式以及后驱动保护

• 闭锁性能超过 100 mA,符合 JESD 78 Class II 标

准

• ESD 性能等级超过 JESD 22 规范

– 2000 V 人体模型

(A114-B、Class II)

– 200 V 机器模型(A115-A)

– 1000 V 充电器件模型(C101)

说明

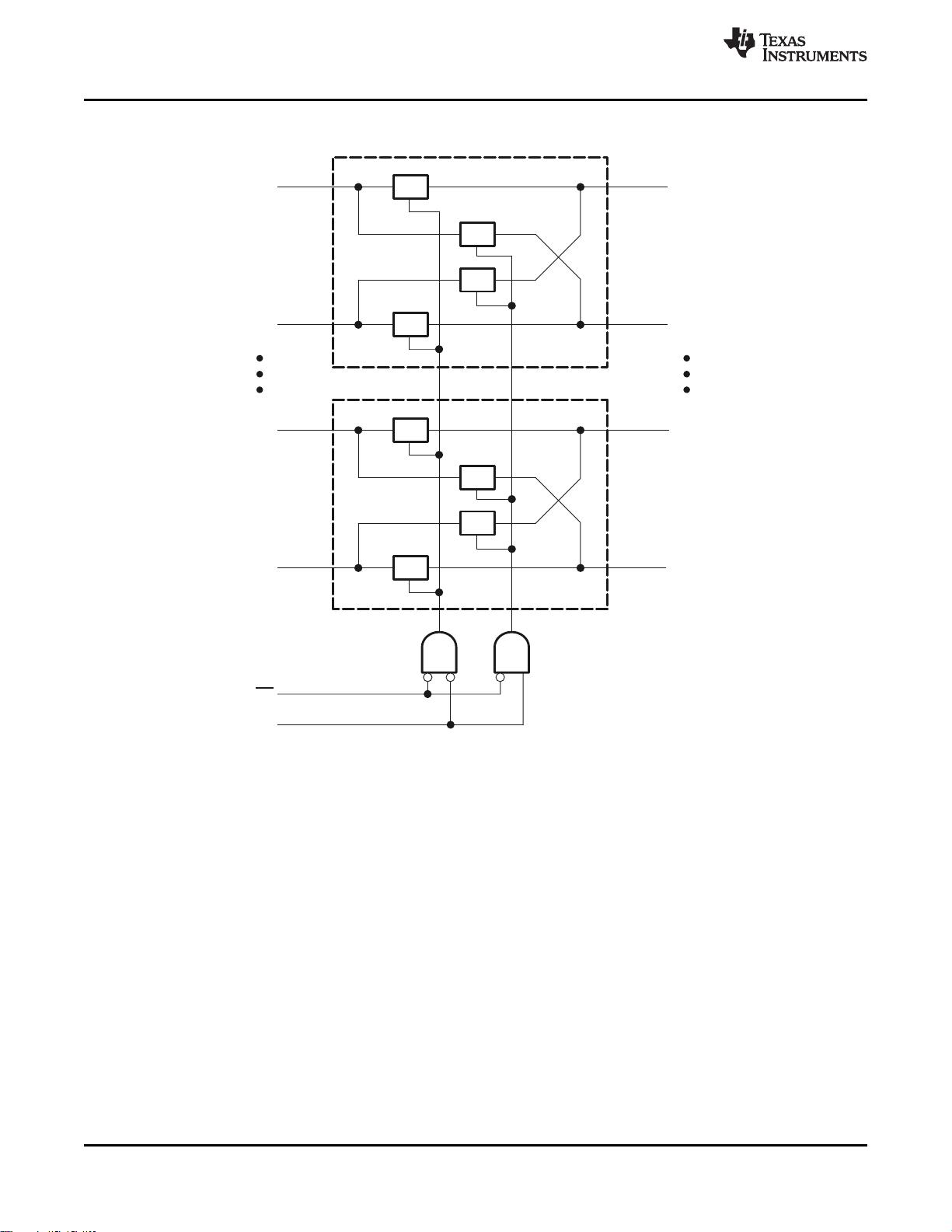

TS5V522C 是高带宽模拟开关,可为 VGA 信号开关提供 2:2 双图形交叉解决方案。 该器件支持 2 个 VGA 信号源

的开关,可在膝上型电脑中将信号指向两个目的位置中的一个。 TS5V522C 集成 5 个针对 RGB 信号的极高性能

380 Mhz(典型值)SPDT 开关、2 对适用于 HSYNC 与 VSYNC 线路的电平转换缓冲器以及集成型 ESD 保护。 5

个交叉开关均可通过 5 V 或 3.3 V TTL 控制信号控制。

TS5V522C 能够以更少的失真将 VGA 模拟信号带到目标位置。 DC 通道(SCA、SCL)可能需要 VGA 连接器上

+5 Vopen 的漏级,而且可能还需要在目标端上提供上拉电容器。 TS5V522C 数据端上的有源下冲保护电路可感测

下冲事件并确保在适当关闭状态下进行开关,从而可对低至 -2 V 的下冲事件提供保护。

要在上电或关断过程中确保高阻抗状态,OE 必须通过上拉电阻器的 V

CC

进行控制;驱动器电流吸收性能可检测电

阻器最小值。

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Copyright © 2011, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not English Data Sheet: SCDS317

necessarily include testing of all parameters.

TS5V522C

ZHCS156 –MARCH 2011

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

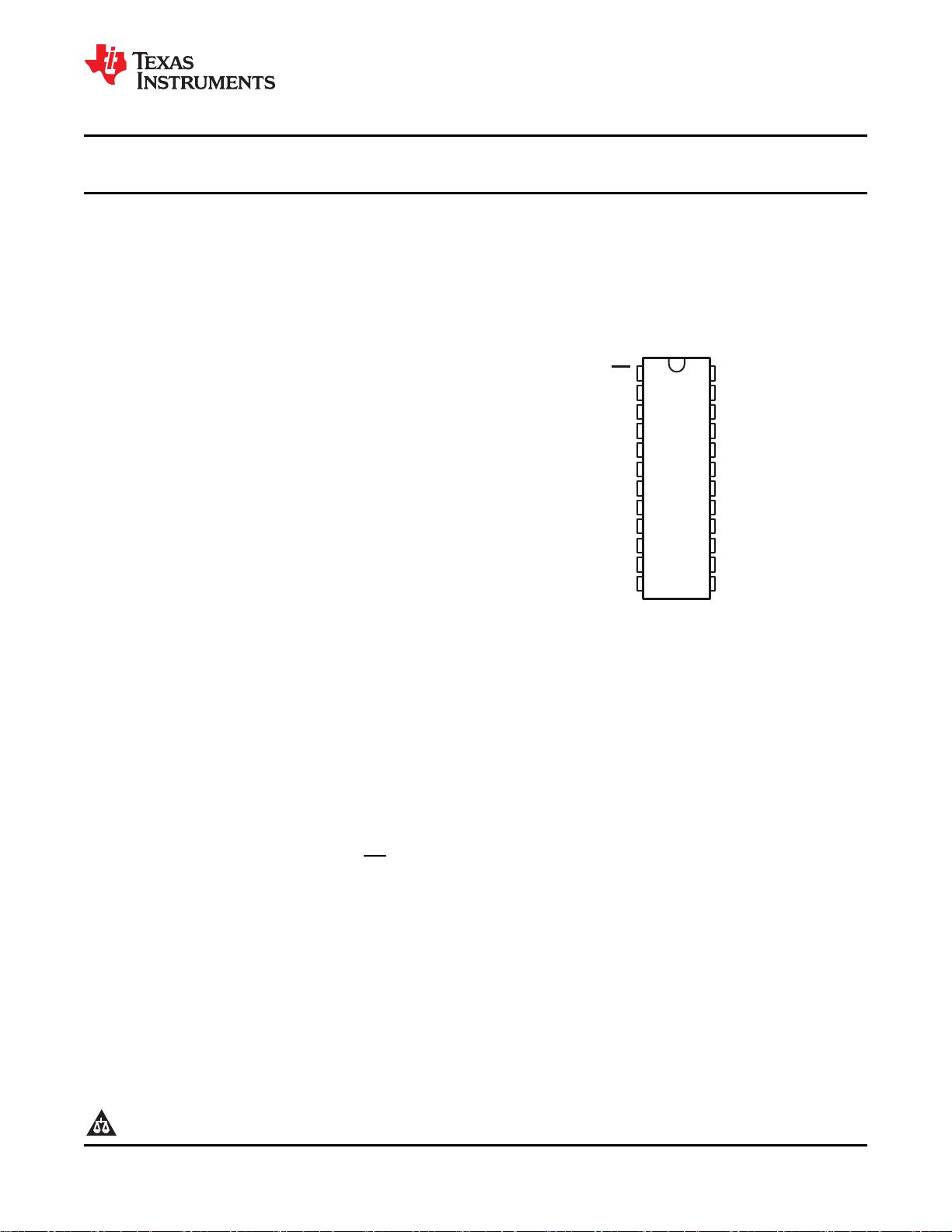

ORDERING INFORMATION

(1)

ORDERABLE PART

T

A

PACKAGE

(2)

TOP-SIDE MARKING

NUMBER

SSOP (QSOP) – DBQ Tape and Reel TS5V522CDBQR TS5V522C

–40°C to 85°C

TSSOP – PW Tape and Reel TS5V522CPWR TE522C

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

Web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

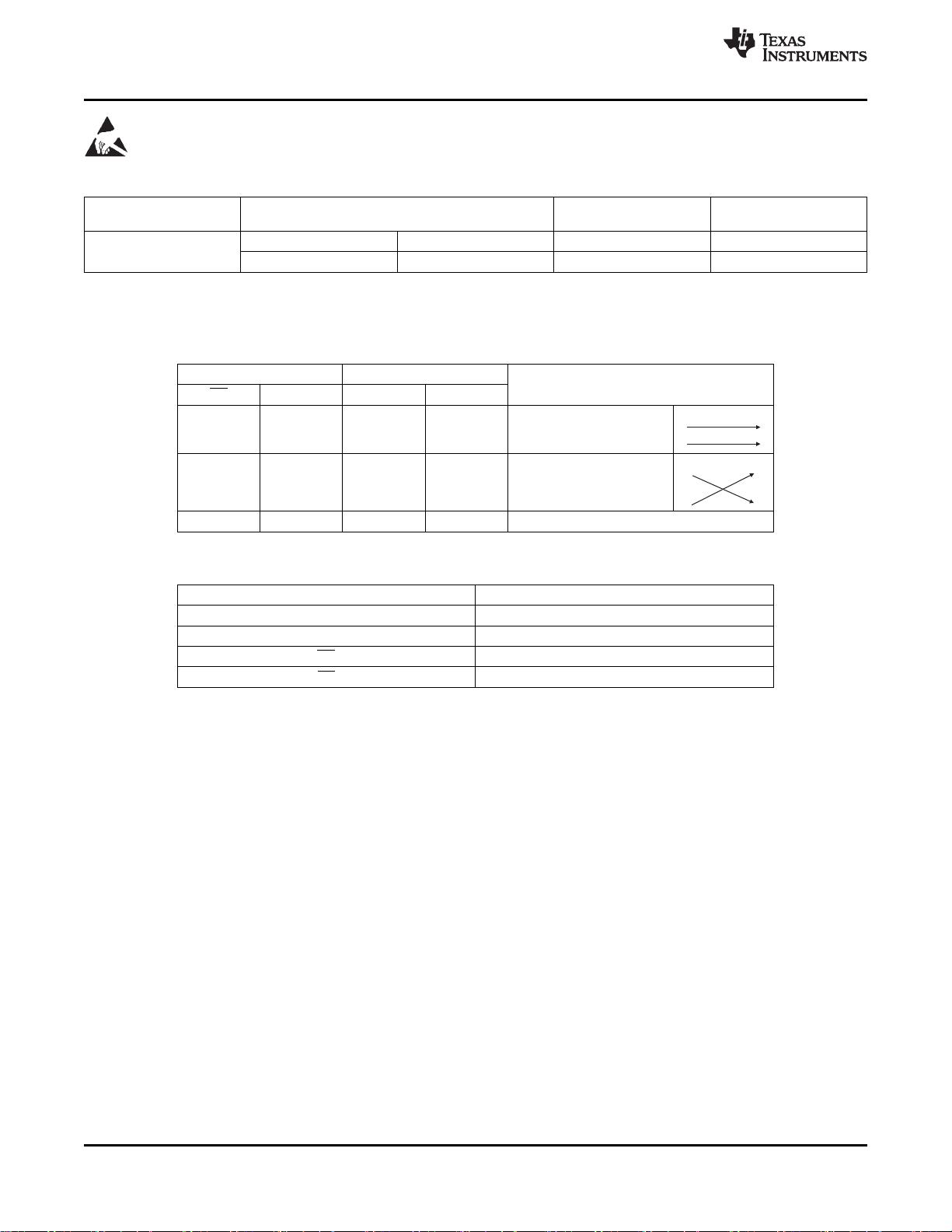

Table 1. FUNCTION TABLE

CONTROL INPUT/OUTPUTS

FUNCTIONS

OE SEL 1 X 2 X

1X port = AX port

L L A X B X

2x port = BX port

1X port = BX port

L H B X A X

2x port = AX port

H X Z Z Disconnect

Table 2. PIN DESCRIPTION

PIN NAME DESCRIPTION

xR, xG, xB Analog Video I/Os

xSCL, xSCA Analog sync I/Os

OE Enable pin

EN Input select

2 Copyright © 2011, Texas Instruments Incorporated

TS5V522C

www.ti.com.cn

ZHCS156 –MARCH 2011

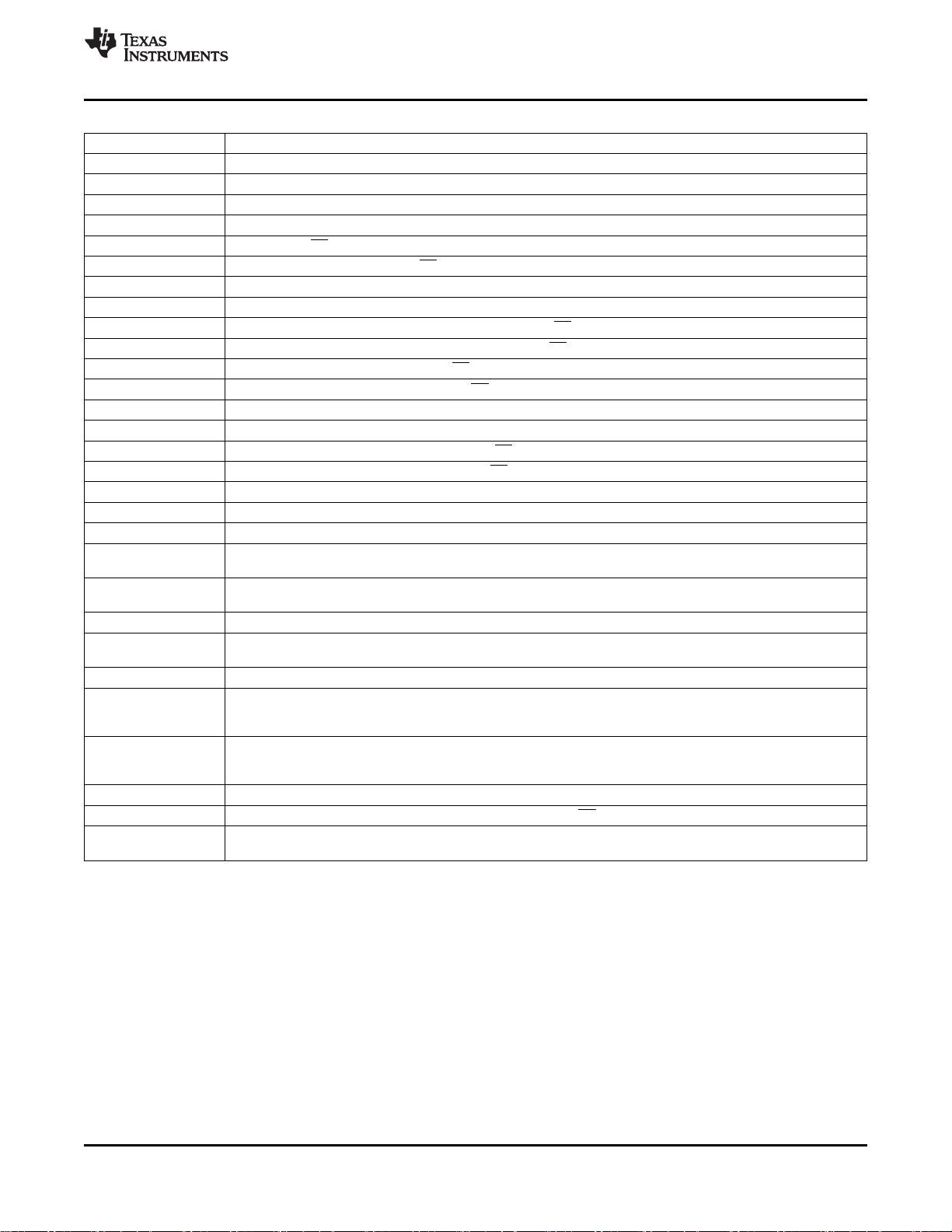

PARAMETER DEFINITIONS

PARAMETER DESCRIPTION

r

ON

Resistance between the input and output ports with the switch in the ON-state

I

OZ

Output leakage current measured at the D and S ports with the switch in the OFF-state

I

OS

Short circuit current measured at the I/O pins.

V

IN

Voltage at the IN pin

V

EN

Voltage at the EN pin

C

IN

Capacitance at the control inputs (EN, IN)

C

OFF

Capacitance at the analog I/O port when the switch is OFF

C

ON

Capacitance at the analog I/O port when the switch is ON

V

IH

Minimum input voltage for logic high for the control inputs (EN, IN)

V

IL

Minimum input voltage for logic low for the control inputs (EN, IN)

V

H

Hysteresis voltage at the control inputs (EN, IN)

V

IK

I/O and control inputs diode clamp voltage (EN, IN)

V

I

Voltage applied to the I/O pins when I/O is the switch input.

V

O

Voltage applied to the I/O pins when I/O is the switch output.

I

IH

Input high leakage current of the control inputs (EN, IN)

I

IL

Input low leakage current of the control inputs (EN, IN)

I

I

Current into the I/O pins when I/O is the switch input.

I

O

Current into the I/O pins when I/O is the switch output.

I

off

Output leakage current measured at the I/O ports with V

CC

= 0

Propagation delay measured between 50% of the digital input to 90% of the analog output when switch is turned

t

ON

ON.

Propagation delay measured between 50% of the digital input to 90% of the analog output when switch is turned

t

OFF

OFF.

BW Frequency response of the switch in the ON-state measured at –3 dB

Unwanted signal coupled from channel to channel. Measured in –dB. X

TALK

= 20 LOG V

OUT

/V

IN

. This is a

X

TALK

non-adjacent crosstalk.

O

IRR

Off-isolation is the resistance (measured in –dB) between the input and output with the switch OFF.

Magnitude variation between analog input and output pins when the switch is ON and the DC offset of composite

D

G

video signal varies at the analog input pin. In NTSC standard the frequency of the video signal is 3.58 MHz and

DC offset is from 0 to 0.714 V.

Phase variation between analog input and output pins when the switch is ON and the DC offset of composite

D

P

video signal varies at the analog input pin. In NTSC standard the frequency of the video signal is 3.58 MHz and

DC offset is from 0 to 0.714 V.

I

CC

Static power supply current

I

CCD

Variation of I

CC

for a change in frequency in the control inputs (EN, IN)

This is the increase in supply current for each control input that is at the specified voltage level, rather than V

CC

or

ΔI

CC

GND.

Copyright © 2011, Texas Instruments Incorporated 3

VGA

Graphics

(3.3V)

VGA

Graphics

(3.3V)

Logic Control

TS5V522C

VGA Connector

R

G

B

H.Sync

V.Sync

SDA

SCL

Docking Station

Connector

R

G

B

H.Sync

V.Sync

SDA

SCL

CBT3257C

VCC = + 5V

VCC = + 3.3V

VCC = + 5V

Design Notes:

1. DDC (SCL,SDA) is open drain I

2

C Bus type and need pull up resistors.

N-Channel FET Switch allow to pull up desired Vcc Level not exceeding the

Vcc of FET Switch

2. VGA (H.Sync, V.Sync) are TTL/CMOS Type from the source of V ideo and it may

required pull up to achieve as high as 5V Signal level to meet VGA Specifications too.

SW

SW

SW

SW

TS5V522C

www.ti.com.cn

ZHCS156 –MARCH 2011

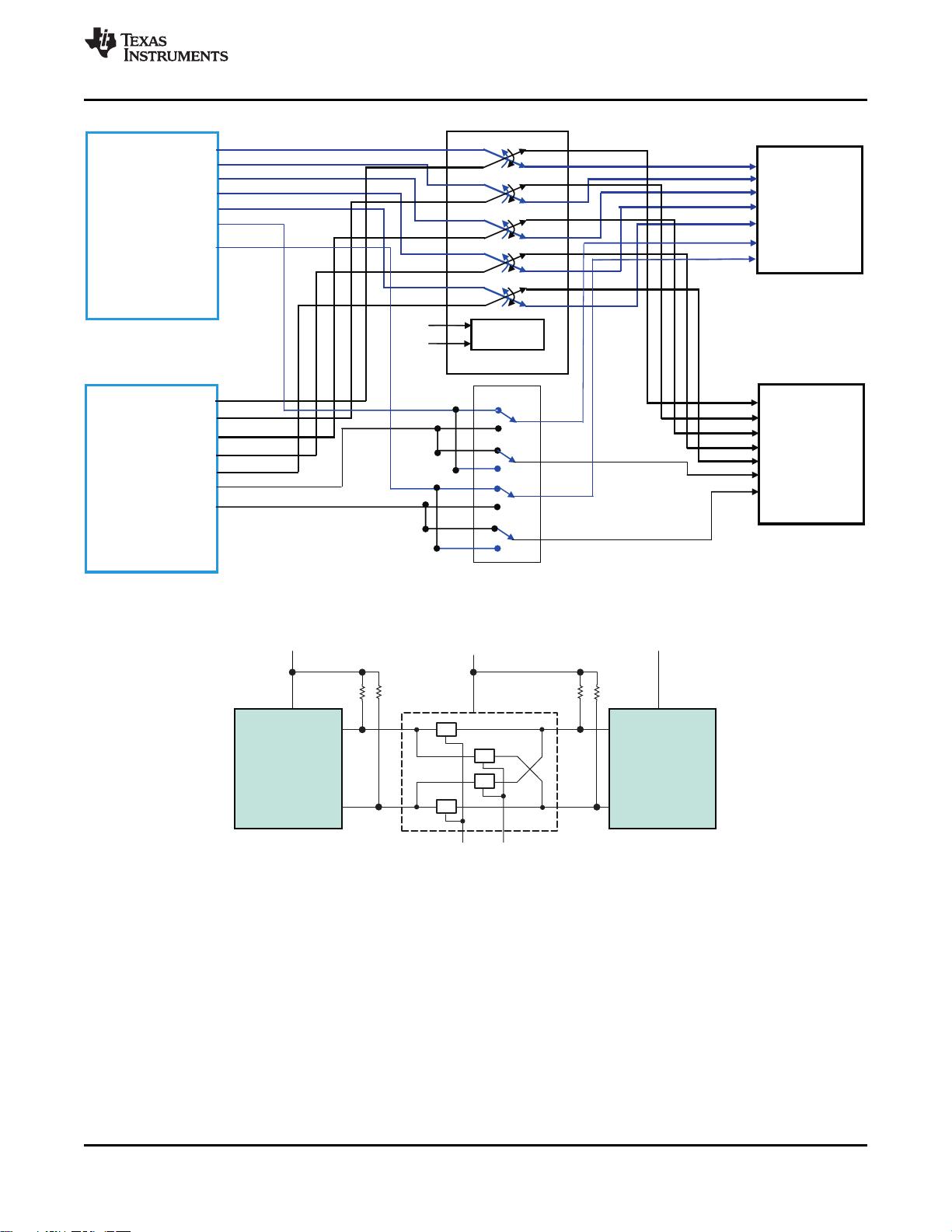

Figure 1. Typical Design Examples for Dual VGA Source Signal Exchange

Figure 2. Typical Design Example for Level Shifting with N-Channel FET Switch

Copyright © 2011, Texas Instruments Incorporated 5

剩余20页未读,继续阅读

资源评论

不觉明了

- 粉丝: 3102

- 资源: 5337

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功