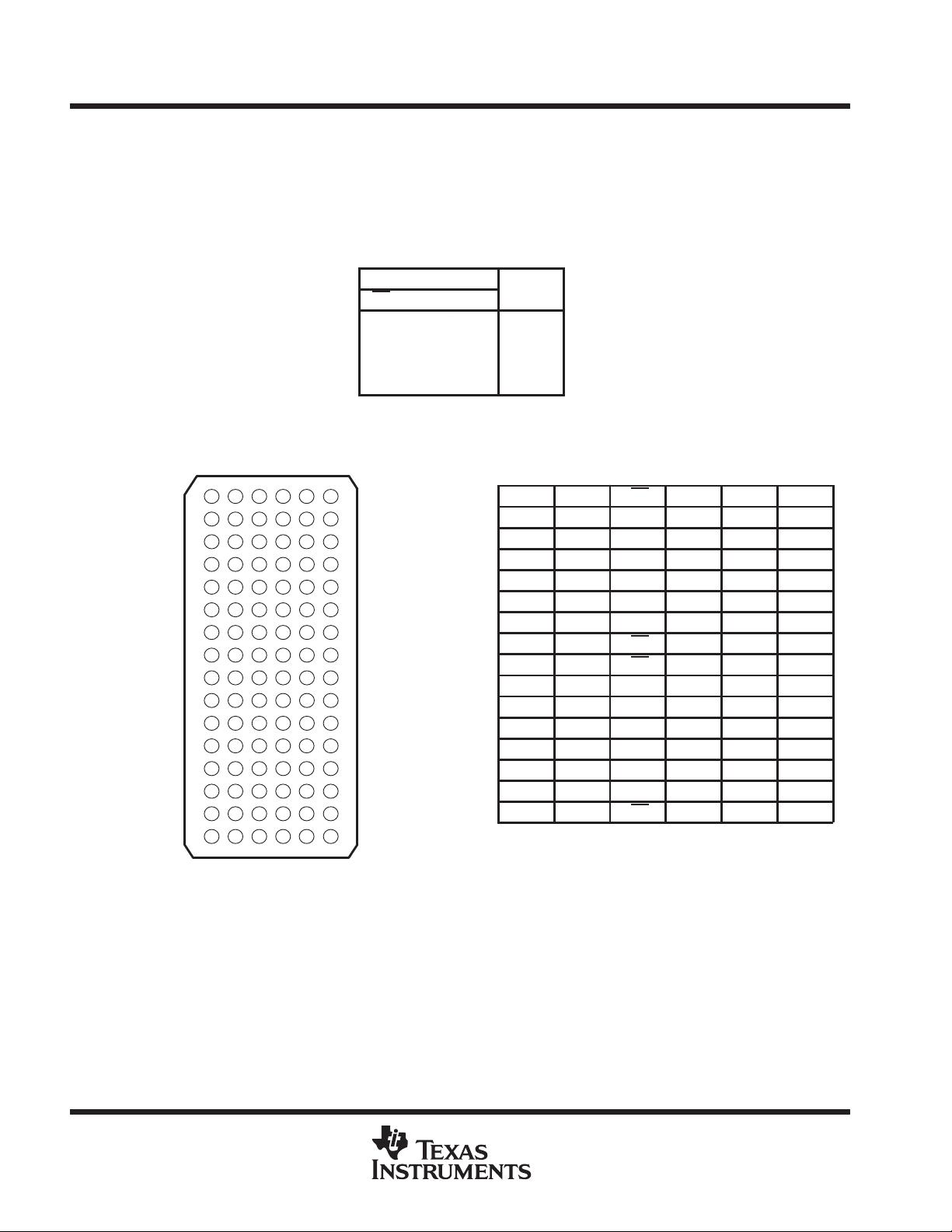

TI-SN74ALVTH32373是一款由德州仪器(TI)推出的高性能、低功耗的32位透明D型锁存器,它带有3态输出功能。这款芯片设计适用于2.5伏特或3.3伏特的工作电压,同时也能够支持5伏特系统环境下的TTL接口。其先进特性包括使用了先进的BiCMOS技术(ABT),即Advanced BiCMOS Technology(ABT),旨在实现宽总线设计,优化2.5伏特和3.3伏特操作以及低静态功率损耗。 在混合模式信号操作中,SN74ALVTH32373能够处理5伏特的输入和输出电压,同时保持2.3伏特至3.6伏特的VCC工作范围。它的典型输出接地反弹(VOLP)在VCC = 3.3伏特和TA = 25°C时小于0.8伏特,这意味着输出切换时具有出色的电源稳定性。此外,该器件提供了高驱动能力,2.5伏特VCC下输出驱动电流为-24/24毫安,3.3伏特VCC下则为-32/64毫安,确保了强大的驱动性能。 为了支持热插拔和节省能源,该芯片集成了Ioff和3态电源启动功能。数据输入端使用了Bus Hold功能,可以替代外部上拉/下拉电阻,防止总线浮空,提高了系统的稳定性。此外,自动3态功能在输出电压超过VCC + 0.5伏特时自动切断总线电流负载,进一步优化了能源效率。 SN74ALVTH32373采用了流线型架构,方便了印刷电路板的布局设计。分布式VCC和GND引脚有助于减少高速开关噪声。其抗锁定性能超过JESD 78,Class II标准,确保了设备在恶劣环境下的稳定运行。ESD保护也超过了JESD 22标准,包括2000V的人体模型(A114-A)、200V的机器模型(A115-A)以及1000V的充电设备模型(C101),增强了器件的静电防护能力。 封装方面,SN74ALVTH32373采用塑料精细间距球栅阵列(Fine-Pitch Ball Grid Array, FBGA)封装,提供高度集成和紧凑的解决方案。这些设备可作为四个8位锁存器、两个16位锁存器或一个32位锁存器使用。通过使能输入(LE)控制,当LE为高电平时,Q输出跟随数据输入(D);当LE为低电平时,Q输出将被D输入设置的电平锁定。缓冲的输出使能(OE)输入允许选择正常逻辑状态或高阻态,使输出能在需要时切换到高阻态,避免对总线造成额外负载。 TI-SN74ALVTH32373是适用于高性能、低功耗系统中的缓冲寄存器、I/O端口、双向总线驱动器和工作寄存器的理想选择,其卓越的电气特性和封装设计确保了在复杂系统中的可靠性和灵活性。

剩余14页未读,继续阅读

- 粉丝: 6378

- 资源: 5764

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 精益管摆盘周转车sw17可编辑全套设计资料100%好用.zip

- 可变距平皮带输送机sw16可编辑全套设计资料100%好用.zip

- 六轴二保焊焊接机器人设计(带焊接枪)x_t全套设计资料100%好用.zip

- C# 运动控制系统 雷赛运动控制卡控制系统 像高川控制卡、高川控制器、或者固高运动控制卡以及正运动控制器、正运动控制卡可以用这个框架,自己替一下库文件等代码就可以 源码全开放,不设限,标有注释

- 马铃薯收割机sw20可编辑全套设计资料100%好用.zip

- 奶酪包装装盒生产线 sw20全套设计资料100%好用.zip

- 皮带输送机检测机sw17全套设计资料100%好用.zip

- 农业机械-耕耘割茬播种一体机sw17全套设计资料100%好用.zip

- 基于拓展卡尔曼滤波的车辆质量与道路坡度估计 车辆坡度与质量识别模型,基于扩展卡尔曼滤波,估计曲线与实际误差合理 先用递归最小二乘法(RLS)质量识别,最后利用扩展卡尔曼坡度识别(EKF) 送纹献

- 随机路面,路面激励,路面不平度 软件使用:Matlab Simulink 适用场景:采用模块化建模方法,搭建随机路面模型,可实现不同车速,不同路面等级的路面激励 包含:simulink源码文件,详细

- wincc高级报表,支持自定义模版,支持打印预览,支持打印PDF,支持导出Excel表格,支持自定义打印区域,可显示最大值,最小值,平均值,可求和 可以在wincc7.4 7.5 8.0,博图win

- (179842242)校园食堂订餐系统 JAVA毕业设计 源码+数据库+论文+启动教程(SpringBoot+Vue.JS).zip

- 基于fpga的温度采集系统工程,max6675驱动源码,可上传到电脑上位机软件绘制温度曲线 fpga代码、和QT控制软件 是工程代码

- (21545816)JAVA登录注册页面实现前端与后台数据连接

- (4799648)图书管理系统(源代码)

- 燃烧器三维step全套设计资料100%好用.zip

信息提交成功

信息提交成功