5

MT4C16270 Micron Technology, Inc., reserves the right to change products or specifications without notice.

W06.pm5 – Rev. 10/96 1996, Micron Technology, Inc.

MT4C16270

256K x 16 DRAM

TECHNOLOGY, INC.

V

V

IH

IL

V

V

IH

IL

RAS#

V

V

IH

IL

ADDR

ROW

COLUMN (A)

DON’T CARE

UNDEFINED

V

V

IH

IL

WE#

V

V

IOH

IOL

OPEN

DQ

t

WPZ

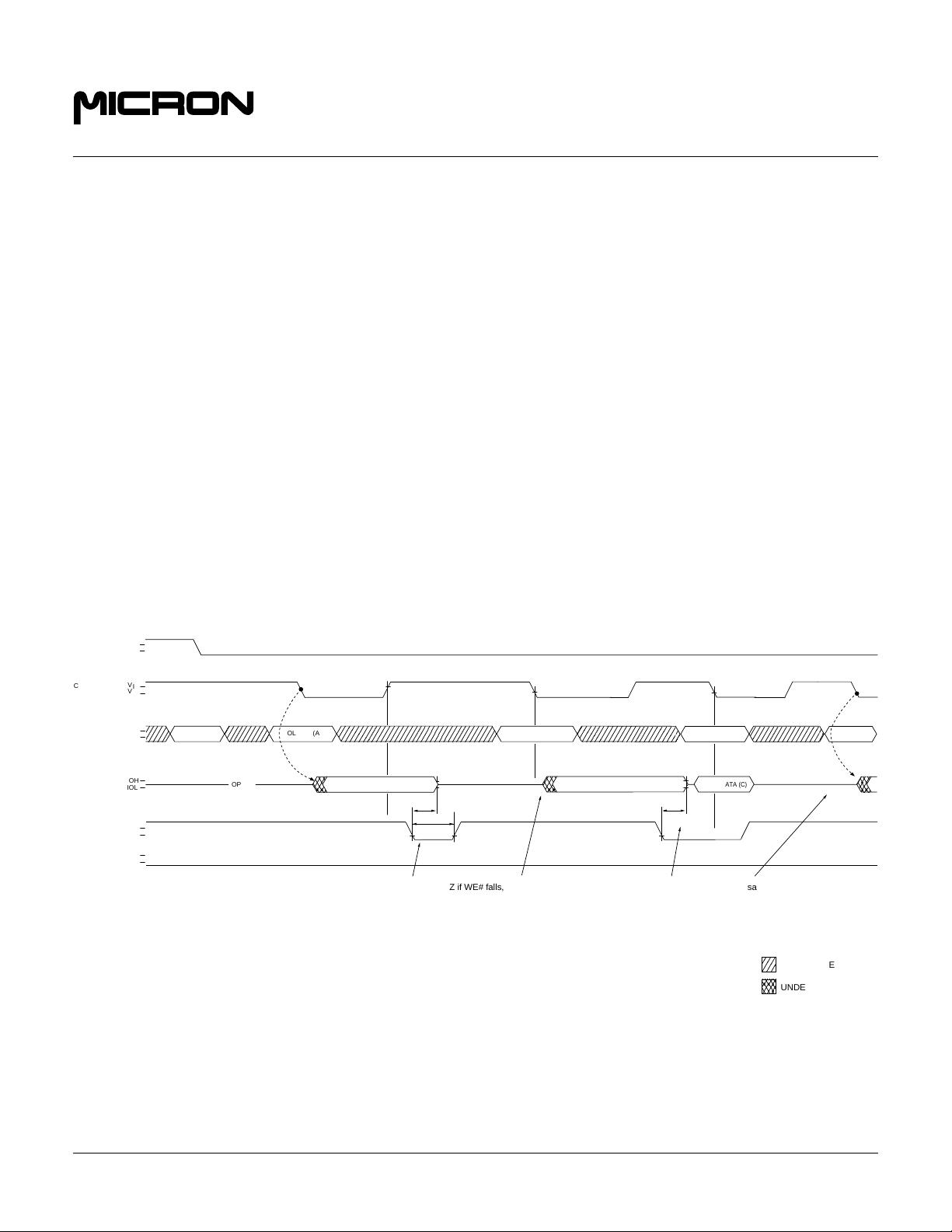

The DQs go to High-Z if WE# falls, and if

t

WPZ is met,

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

V

V

IH

IL

OE#

VALID DATA (B)

t

WHZ

WE# may be used to disable the DQs to prepare

for input data in an EARLY WRITE cycle. The DQs

will remain High-Z until CAS# goes LOW with

WE# HIGH (i.e., until a READ cycle is initiated).

t

WHZ

COLUMN (D)

VALID DATA (A)

COLUMN (B)

COLUMN (C)

INPUT DATA (C)

CASL#/CASH#

Figure 4

OUTPUT ENABLE AND DISABLE WITH WE#

transitions HIGH. Then OE# can pulse HIGH for a mini-

mum of

t

OEP anytime during the CAS# HIGH period and

the DQs will tristate and remain tristate, regardless of OE#,

until CAS# falls again (please reference Figure 3 for further

detail on the toggling OE# condition). During other cycles,

the outputs are disabled at

t

OFF time after RAS# and CAS#

are HIGH, or

t

WHZ after WE# transitions LOW. The

t

OFF

time is referenced from the rising edge of RAS# or CAS#,

whichever occurs last. WE# can also perform the function

of turning off the output drivers under certain conditions,

as shown in Figure 4.

Returning RAS# and CAS# HIGH terminates a memory

cycle and decreases chip current to a reduced standby level.

The chip is also preconditioned for the next cycle during the

RAS# HIGH time. Memory cell data is retained in its correct

state by maintaining power and executing any RAS# cycle

(READ, WRITE) or RAS# refresh cycle (RAS#-ONLY, CBR,

or HIDDEN) so that all 512 combinations of RAS# ad-

dresses (A0-A8) are executed at least every 8ms, regardless

of sequence. The CBR REFRESH cycle will also invoke the

refresh counter and controller for row address control.

EDO PAGE MODE

DRAM READ cycles have traditionally turned the out-

put buffers off (High-Z) with the rising edge of CAS#. If

CAS# goes HIGH, and OE# is LOW (active), the output

buffers will be disabled. The MT4C16270 offers an acceler-

ated PAGE MODE cycle by eliminating output disable from

CAS# HIGH. This option is called EDO and it allows CAS#

precharge time (

t

CP) to occur without the output data going

invalid (see READ and EDO-PAGE-MODE READ wave-

forms).

EDO operates as any DRAM READ or FAST-PAGE-

MODE READ, except data will be held valid after CAS#

goes HIGH, as long as RAS# and OE# are held LOW and

WE# is held HIGH. OE# can be brought LOW or HIGH

while CAS# and RAS# are LOW, and the DQs will transi-

tion between valid data and High-Z. Using OE#, there are

two methods to disable the outputs and keep them disabled

during the CAS# HIGH time. The first method is to have

OE# HIGH when CAS# transitions HIGH and keep OE#

HIGH for

t

OEHC. This will tristate the DQs and they will

remain tristate, regardless of OE#, until CAS# falls again.

The second method is to have OE# LOW when CAS#

评论0

最新资源