数字电路与逻辑设计实验

第三次实验报告

姓 名

学 院

专 业

班 级

学 号

班内序号

1

完成时间

2021 年 月

目录

一、实验七:4*4 键盘扫描控制器.................................................................................................................2

1.1 实验名称和实验任务要求.................................................................................................................2

1.2 设计思路、模块划分、总体框图等.................................................................................................3

1.3 VHDL 代码..........................................................................................................................................4

1.4 仿真波形图及分析...........................................................................................................................24

1.5 故障及问题分析...............................................................................................................................26

二、总结与结论..............................................................................................................................................26

一、实验七:4*4 键盘扫描控制器

1.1 实验名称和实验任务要求

1.1.1 实验名称:VHDL 组合时序电路设计——4*4 键盘扫描控制器的

设计与实现

1.1.2 实验任务要求:

(1):设计并实现 4*4 键盘扫描控制电路,判断哪个按键被按下,

在数码管上显示键值,并通过蜂鸣器发出按键音。

(2):键值采用 16 进制编码,即 16 个按键分别对应显示 16 进制数

0~F,按键对应关系如下:最上面一行从左至右依次为 0~3,第二行

从左至右依次为 4~7,第三行从左至右依次为 8~B,最下面一行从左

至右依次为 C~F,其中 b、d 显示为小写,其他字母大写;

2

(3):按键按下时显示当前键值并保持,直到下一按键按下时更新

显示;只有按键被按下时蜂鸣器发出按键音,放开后蜂鸣器不发声。

每个按键对应不同的按键音。

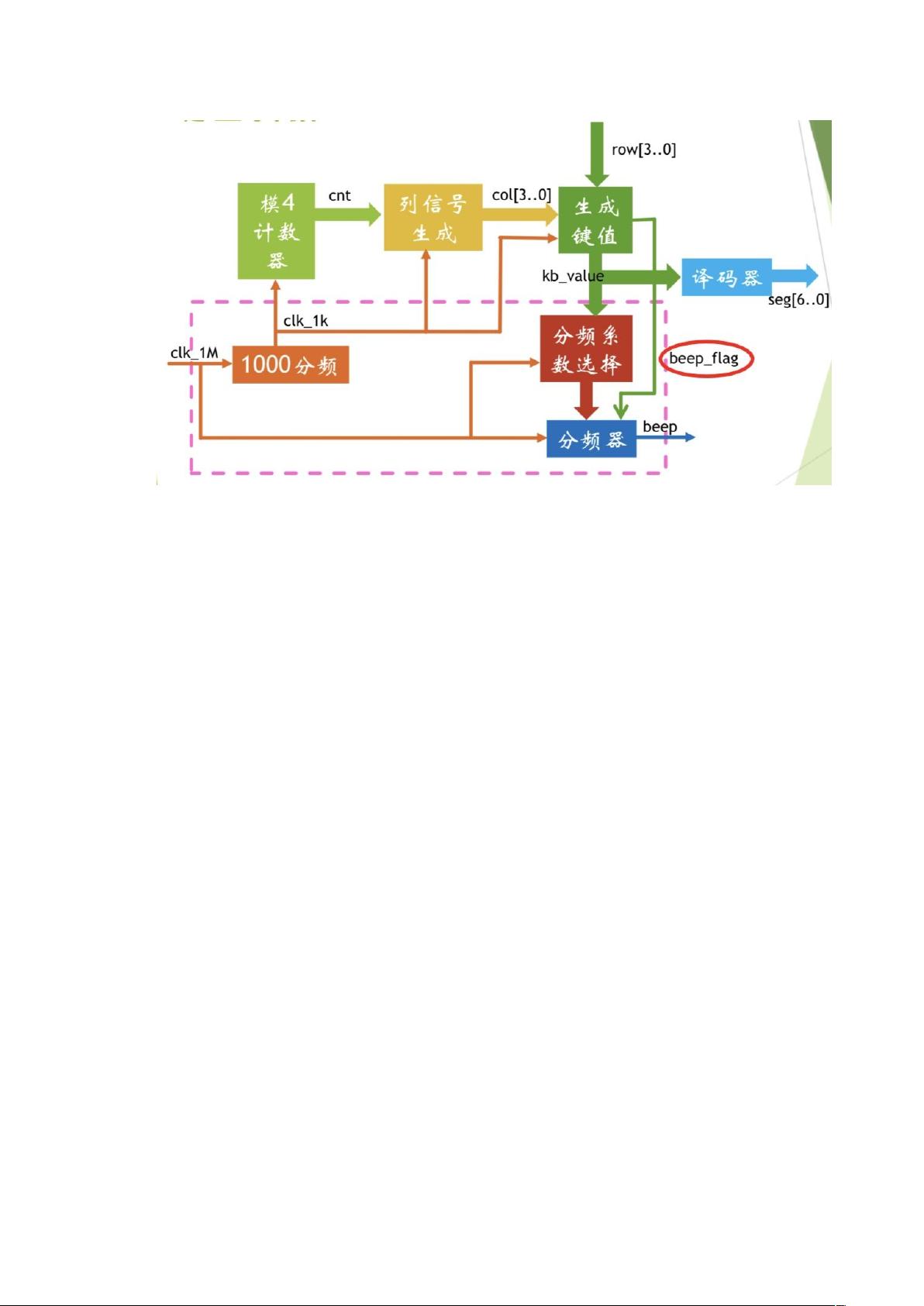

1.2 设计思路、模块划分、总体框图等

1.2.1 设计思路:col0~col3 为列输出信号,使用时循环向各列写‘0’;

没有按下时,row 接收到来自电源的高电平‘1’;row0~row3 为行输入

信号,使用时读取四路信号,判断是否有‘0’输入;如果读到行信号上

有‘0’,根据行、列信号为‘0’的位置判断哪个按键按下了。遵循这样的

原理,对于扫描显示,只需要不断寻找 row 和 col 都是‘0’的位置就能

确定相应数字的输出。

对于蜂鸣器,需要 16 分频器,按照需要的频率进行分频,并将其输

出到蜂鸣器。因为蜂鸣器在输入不同频率的时钟时,会产生不同频率

的声音。

1.2.3 总体框图:

3

1.3 VHDL 代码

(1)1000 分频器:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div_1000 is

port(

clk:in std_logic;

clkout:out std_logic

);

end div_1000;

4

architecture a of div_1000 is

signal t:STD_LOGIC;

begin

process(clk)

variable count:integer range 0 to 499;

begin

if (clk'event and clk='1') then

if count=499 then

count:=0;

t<= not t;

else

count:=count+1;

end if;

end if;

end process;

clkout<=t;

end;

(2)模 4 计数器:

library ieee;

use ieee. std_logic_1164.all;

use ieee. std_logic_unsigned.all;

5

- 1

- 2

- 3

- 4

- 5

前往页