没有合适的资源?快使用搜索试试~ 我知道了~

瑞萨R7F0C903_908芯片资料

需积分: 5 11 下载量 169 浏览量

2022-05-05

10:29:59

上传

评论

收藏 1.64MB PDF 举报

温馨提示

试读

99页

瑞萨R7F0C903_908芯片资料

资源详情

资源评论

资源推荐

Datasheet

R7F0C903-908

RENESAS MCU

True Low Power Platform (as low as 66 µA/MHz, and 0.57 µA for LVD), 1.6 V to 5.5 V

operation, 16 to 48 Kbyte Flash, 31 DMIPS at 24 MHz, for General Purpose Applications

Page 1 of 96

R01DS0237EJ0100

Rev.1.00

Jun 05, 2014

R01DS0237EJ0100 Rev.1.00

Jun 05, 2014

1. OUTLINE

1.1 Features

Ultra-Low Power Technology

1.6 V to 5.5 V operation from a single supply

Stop (RAM retained): 0.23 µA, (LVD enabled): 0.31

µA

Halt (LVD): 0.57 µA

Snooze: 0.70 mA (UART), 1.20 mA (ADC)

Operating: 66 µA/MHz

16-bit RL78 CPU Core

Delivers 31 DMIPS at maximum operating frequency

of 24 MHz

Instruction Execution: 86% of instructions can be

executed in 1 to 2 clock cycles

CISC Architecture (Harvard) with 3-stage pipeline

Multiply Signed & Unsigned: 16 x 16 to 32-bit result in

1 clock cycle

MAC: 16 x 16 to 32-bit result in 2 clock cycles

16-bit barrel shifter for shift & rotate in 1 clock cycle

1-wire on-chip debug function

Main Flash Memory

Density: 16 KB to 48 KB

Block size: 1 KB

On-chip single voltage flash memory with protection

from block erase/writing

Self-programming with secure boot swap function

and flash shield window function

Data Flash Memory

Data Flash with background operation

Data flash size: 2 KB size option or none

Erase Cycles: 1 Million (typ.)

Erase/programming voltage: 1.8 V to 5.5 V

RAM

2 KB or 3 KB size options

Supports operands or instructions

Back-up retention in all modes

High-speed On-chip Oscillator

24 MHz with +/ 1% accuracy over voltage (1.8 V to

5.5 V) and temperature (20 °C to 85 °C)

Pre-configured settings: 24 MHz, 16 MHz, 12 MHz, 8

MHz, 6 MHz, 4 MHz, 3 MHz, 2 MHz,

and 1 MHz

Reset and Supply Management

Power-on reset (POR) monitor/generator

Low voltage detection (LVD) with 14 setting options

(Interrupt and/or reset function)

Data Memory Access (DMA) Controller

2 channels

Transfer unit: 8- or 16-bit

Multiple Communication Interfaces

1 x I

2

C multi-master

Up to 3 x CSI/UART/Simple IIC

Extended-Function Timers

Multi-function 16-bit timers: Up to 8 channels

Interval Timer: 12-bit, 1 channel

15 kHz watchdog timer : 1 channel (window function)

Rich Analog

ADC: Up to 8 channels, 10-bit resolution, 2.1 µs

conversion time

Supports 1.6 V

Internal voltage reference (1.45 V)

Safety Features (IEC or UL 60730 compliance)

Flash memory CRC calculation

RAM parity error check

RAM write protection

SFR write protection

Illegal memory access detection

Clock stop/ frequency detection

ADC self-test

General Purpose I/O

5V tolerant, high-current (up to 20 mA per pin)

Open-Drain, Internal Pull-up support

Different potential interface support: Can connect to

a 1.8/2.5/3 V device

Operating Ambient Temperature

Standard: 40 °C to +85 °C

Package Type and Pin Count

32-pin LQFP (7 x 7 mm, 0.8 mm pitch)

R7F0C903-908 1. OUTLINE

Page 2 of 96

R01DS0237EJ0100 Rev.1.00

Jun 05, 2014

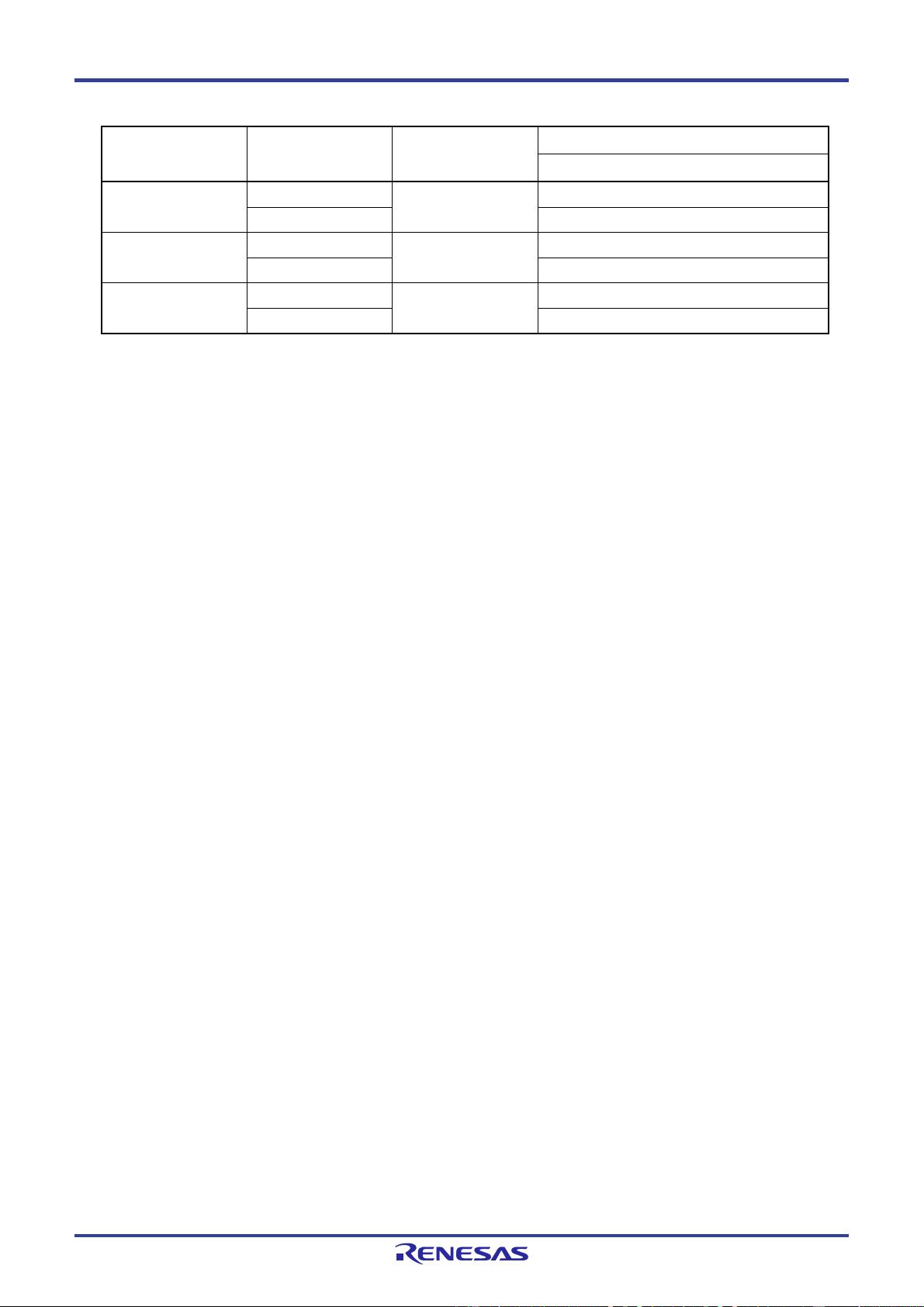

ROM, RAM capacities

R7F0C903-908 Flash ROM

Data flash

RAM

32 pins

2 KB R7F0C908B2

48 KB

3 KB

R7F0C905B2

2 KB R7F0C907B2

32 KB

2 KB

R7F0C904B2

2 KB R7F0C906B2

16 KB

2 KB

R7F0C903B2

R7F0C903-908 1. OUTLINE

Page 3 of 96

R01DS0237EJ0100 Rev.1.00

Jun 05, 2014

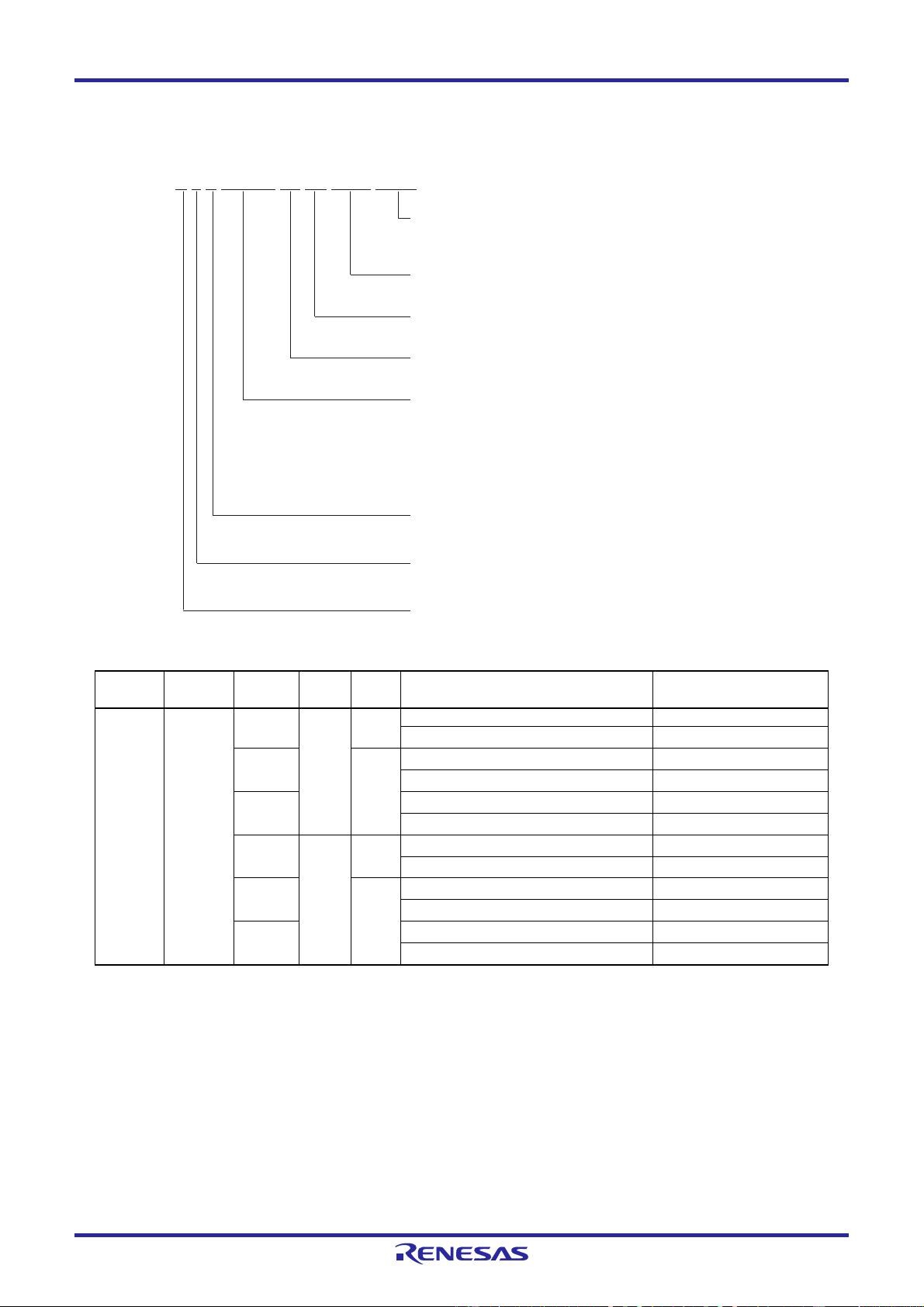

1.2 List of Part Numbers

Figure 1-1. Part Number, Memory Size, and Package of R7F0C903-908

Part No. R 7 F 0C908 B 2D FP-C #AA0

㩷

Packaging specification:

#AA0 :Tray and lead-free (pure Sn)

#HA0 :Embossed tape and lead-free (pure Sn)

Package type:

FP-C :32-pin LQFP (7x7 mm,0.8mm pin pitch)

Fields of application:

2D :Consumer applications, operating ambient temperature :T

A

=-40to +85

Pin count:

B :32-pin

ROM and data flash capacity:

0C903 :16 KROM and none of data flash

0C904 :32 K ROM and none of data flash

0C905 :48 K ROM and none of data flash

0C906 :16 KROM and 2 K data flash

0C907 :32 KROM and 2 K data flash

0C908 :48 KROM and 2 K data flash

Memory type:

F :Flash memory

Product type:

7 :MCUpart

Renesas semiconductor product

Table 1-1. List of Ordering Part Numbers

Pin count Package Flash

ROM

Data

flash

RAM Packaging specification and

environmental compliance

Ordering part number

Tray and lead-free (pure Sn) R7F0C908B2DFP-C#AA0

48 KB

3 KB

Embossed tape and lead-free (pure Sn) R7F0C908B2DFP-C#HA0

Tray and lead-free (pure Sn) R7F0C907B2DFP-C#AA0

32 KB

Embossed tape and lead-free (pure Sn) R7F0C907B2DFP-C#HA0

Tray and lead-free (pure Sn) R7F0C906B2DFP-C#AA0

16 KB

2 KB

2 KB

Embossed tape and lead-free (pure Sn) R7F0C906B2DFP-C#HA0

Tray and lead-free (pure Sn) R7F0C905B2DFP-C#AA0

48 KB

3 KB

Embossed tape and lead-free (pure Sn) R7F0C905B2DFP-C#HA0

Tray and lead-free (pure Sn) R7F0C904B2DFP-C#AA0

32 KB

Embossed tape and lead-free (pure Sn) R7F0C904B2DFP-C#HA0

Tray and lead-free (pure Sn) R7F0C903B2DFP-C#AA0

32 pins 32-pin

LQFP

(7

7

mm,

0.8 mm

pitch)

16 KB

-

2 KB

Embossed tape and lead-free (pure Sn) R7F0C903B2DFP-C#HA0

Note

For the fields of application, refer to

Figure 1-1 Part Number, Memory Size, and Package of R7F0C903-

908

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering

part numbers, refer to the target product page of the Renesas Electronics website.

R7F0C903-908 1. OUTLINE

Page 4 of 96

R01DS0237EJ0100 Rev.1.00

Jun 05, 2014

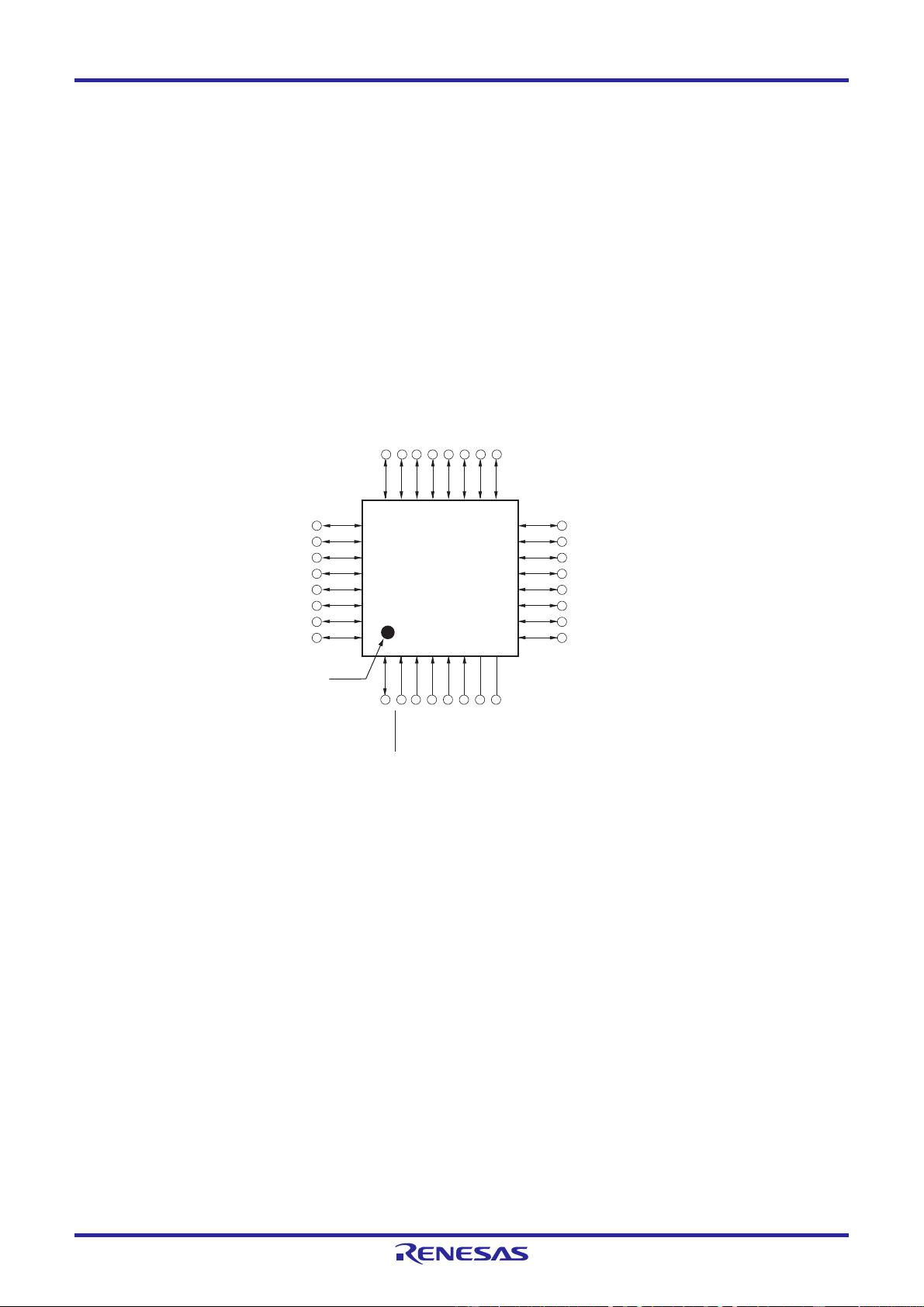

1.3 Pin Configuration (Top View)

32-pin LQFP (7 × 7 mm, 0.8 mm pitch)

16

15

14

13

12

11

10

9

25

26

27

28

29

30

31

32

24 23 22 21 20 19 18 17

1 2 3 4 5 6 7 8

P147/ANI18

P23/ANI3

P22/ANI2

P21/ANI1/AV

REFM

P20/ANI0/AV

REFP

P01/ANI16/TO00/RxD1

P00/ANI17/TI00/TxD1

P120/ANI19

P51/INTP2/SO11

P50/INTP1/SI11/SDA11

P30/INTP3/SCK11/SCL11

P70

P31/TI03/TO03/INTP4/PCLBUZ0

P62

P61/SDAA0

P60/SCLA0

P10/SCK00/SCL00/(TI07)/(TO07)

P11/SI00/RxD0/TOOLRxD/SDA00/(TI06)/(TO06)

P12/SO00/TxD0/TOOLTxD/(TI05)/(TO05)

P13/TxD2/SO20/(SDAA0)/(TI04)/(TO04)

P14/RxD2/SI20/SDA20/(SCLA0)/(TI03)/(TO03)

P15/PCLBUZ1/SCK20/SCL20/(TI02)/(TO02)

P16/TI01/TO01/INTP5/(RXD0)

P17/TI02/TO02/(TXD0)

P40/TOOL0

RESET

P137/INTP0

P122/X2/EXCLK

P121/X1

REGC

V

SS

V

DD

INDEX MARK

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1

F).

Remarks 1. For pin identification, see 1.4 Pin Identification.

2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O

redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register

(PIOR)

in the RL78/G13 User’s Manual Hardware

.

3. It is recommended to connect an exposed die pad to Vss.

R7F0C903-908 1. OUTLINE

Page 5 of 96

R01DS0237EJ0100 Rev.1.00

Jun 05, 2014

1.4 Pin Identification

ANI0 to ANI3,

ANI16 to ANI19: Analog input

AV

REFM: A/D converter reference

potential ( side) input

AVREFP: A/D converter reference

potential (+ side) input

EXCLK: External clock input (Main

system clock)

INTP0 to INTP5: Interrupt request from

peripheral

P00, P01: Port 0

P10 to P17: Port 1

P20 to P23: Port 2

P30, P31: Port 3

P40: Port 4

P50, P51: Port 5

P60 to P62: Port 6

P70: Port 7

P120 to P122: Port 12

P137: Port 13

P147: Port 14

PCLBUZ0, PCLBUZ1: Programmable clock

output/buzzer output

REGC: Regulator capacitance

RESET: Reset

RxD0 to RxD2: Receive data

SCK00, SCK11, SCK20: Serial clock input/output

SCL00, SCL11, SCL20: Serial clock output

SDA00, SDA11, SDA20: Serial data input/output

SI00, SI11, SI20: Serial data input

SO00, SO11, SO20: Serial data output

TI00 to TI07: Timer input

TO00 to TO07: Timer output

TOOL0: Data input/output for tool

TOOLRxD, TOOLTxD: Data input/output for external device

TxD0 to TxD2: Transmit data

V

DD: Power supply

V

SS: Ground

X1, X2: Crystal oscillator (main system clock)

剩余98页未读,继续阅读

泡面丶君

- 粉丝: 0

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0