Universal Asynchronous

Receiver/Transmitter

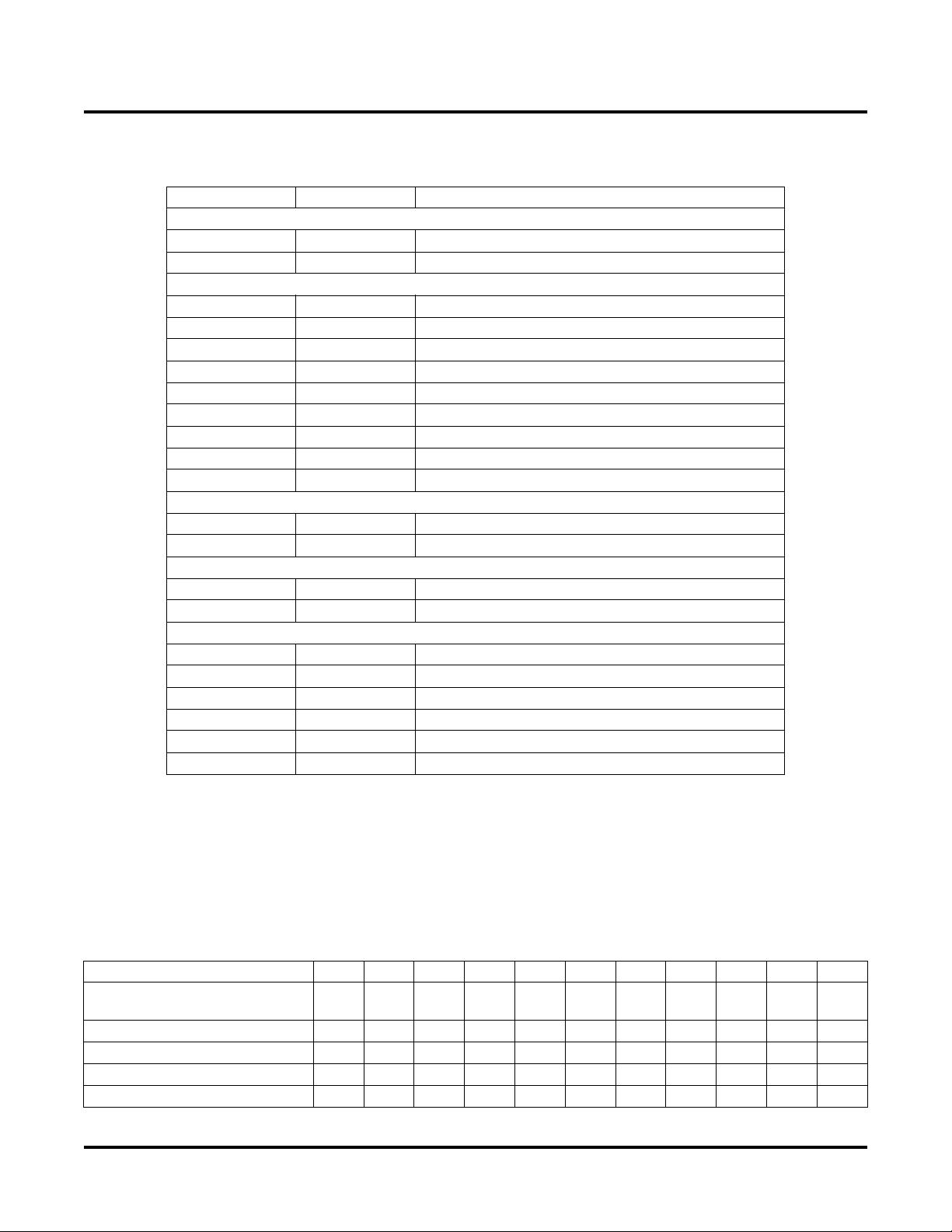

April 2011 Reference Design 1011

www.latticesemi.com 1 rd1011_01.5

© 2011 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Introduction

The Universal Asynchronous Receiver Transmitter (UART) is a popular and widely-used device for data communi-

cation in the field of telecommunication. There are different versions of UARTs in the industry. Some of them con-

tain FIFOs for the receiver/transmitter data buffering and some of them have the 9 data bits mode (start bit + 9 data

bits + parity + stop bits). This reference design describes a fully configurable UART optimized for and implemented

in a variety of Lattice devices, which offer superior performance and architecture compared to existing semiconduc-

tor ASSPs (application-specific standard products).

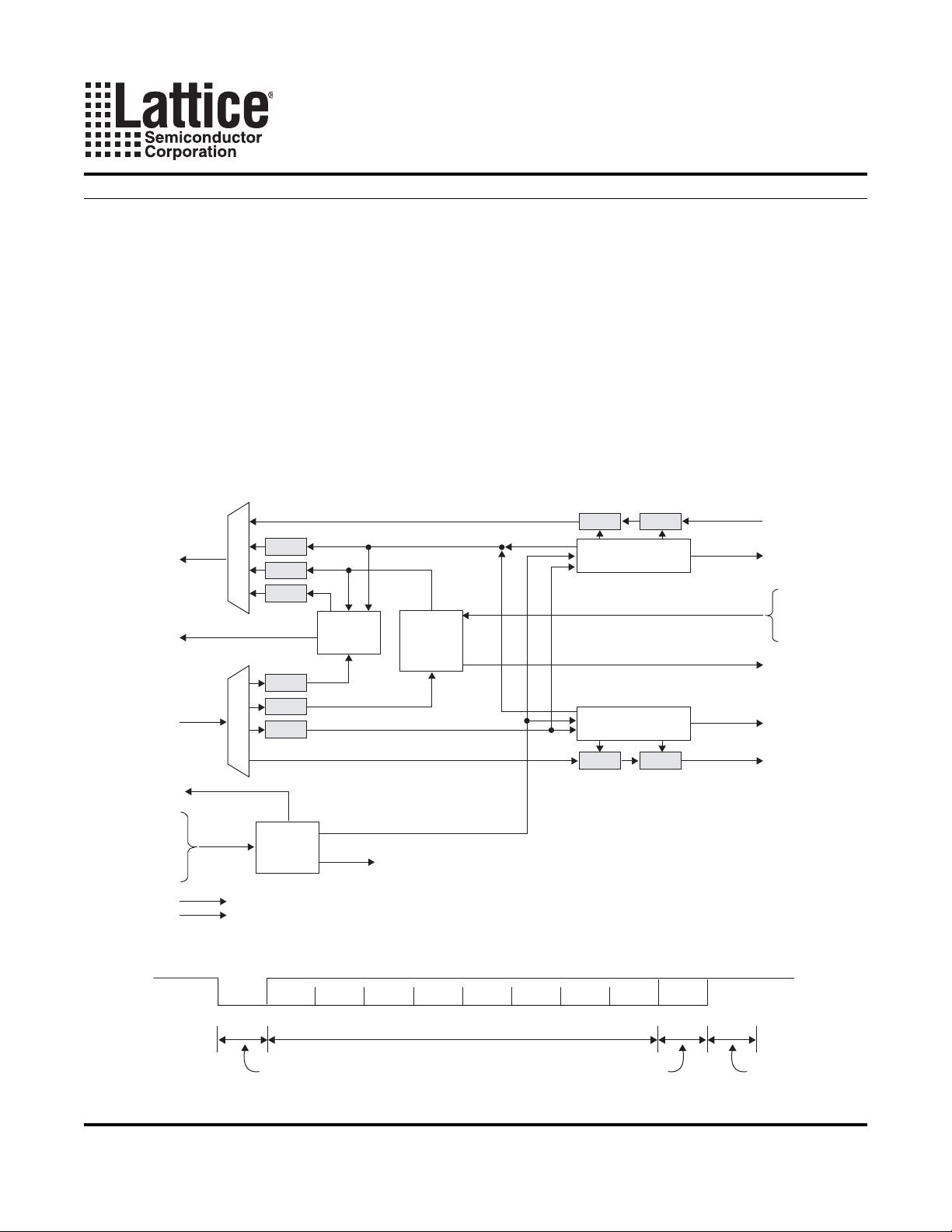

Figure 1 shows the major blocks implemented in this reference design. The receiver performs serial-to-parallel con-

version on the asynchronous data frame received from the serial data input SIN. The transmitter performs parallel-

to-serial conversion on the 8-bit data received from the CPU. In order to synchronize the asynchronous serial data

and to insure the data integrity, start, parity and stop bits are added to the serial data. An example of the UART

frame format is shown in Figure 2.

Figure 1. UART Block Diagram

Figure 2. UART Frame Format: (1 Start Bit, 8 Data Bits, 1 Parity Bit, 1 Stop Bit)

LSR

DOUT

DIN

DDIS

A

ADSn

CS

RDn

WRn

MR

MCLK

INTR

RBR RSR

THR TSR

SOUT

SIN

TxRDYn

RxRDYn

DCDn

CTSn

DSRn

RIn

DTRn

RTSn

MSR

IIR

IER

MCR

LCR

Modem

Control

Receiver Control

and Status

Transmitter Control

and Status

To All Registers

Except RSR and TSR

Tx/Rx Control Signals

Tx/Rx Status Signals

Interrupt

Arbitrator

Register

Access

Control

Start Bit

8 Data Bits

LSB MSB

Stop BitParity Bit

评论0