摘要:本文介绍了基于标准单元库的深亚微米数字集成电路的自动化设计流程。此流程从

设计的系统行为级描述或 RTL 级描述开始,依次通过系统行为级的功能验证,设计综合,

综合后仿真,自动化布局布线,到最后的版图后仿真。在这里,我们用 Synopsys 公司的

VSS(VHDL System Simulator)工具进行各种仿真,用 Design Compiler 进行综合,用 Cadence

公司的 Silicon Ensemble 进行自动布局布线。对于最后的版图后仿真,由于输出文件的限

制,我们改用 Active-HDL 工具进行验证。本文同时用一个实例 DDFS 对整个流程加以了举

例说明。

关键词:库,仿真,约束,综合, floorplan,布局布线。

前言

1

1

前

前前

前言

言言

言

传统的芯片设计方法是手工全定制。随着半导体工艺的几何缩小,集成电路设计已经

到了深亚微米的时代。在同一面积上,晶体管数目的迅猛增加,传统的芯片设计方已几乎

变得不可能。再加上 time-to-market 的压力越来越大,用户要求芯片制造商在最短的时间

内用最低的费用生产高性能产品。为了解决这些问题,新的方法学和工具得到了发展。近

几年来,为了缓解 time-to-market 的压力和快速更新设计以满足用户的要求,一些高性能

的工具和技术得到了发展。高级设计语言的应用,如 VHDL , Verilog ,取代了手画电路图,

并且提高了设计重用。技术更改指令 ECO(Engineering Change Orders)技术的发展更进一

步的提高了设计重用。 Formal Verification 代替动态仿真,不仅提高了验证速度,更重

要的是它摆脱了工艺的约束和仿真 test bench 的不完全性,更全面的检查了电路的功能。

从行为级开始综合大大提高了设计者的设计灵活性,使设计者更进一步脱离了工艺与物理

的限制。设计预算方法学的发展使设计者在较少的时间内得到了较好的 QOR ,并且提供了

更好的环境约束。模块编译器简化和自动化了 data-path 设计,帮设计者解决复杂而没有

规则的 data-path 设计。自动布局布线提高了版图生成的效率,减少了过多的人工干预所

带来的不确定性。版图提取和分析加强了逻辑设计与物理设计之间的联系与信息交换,更

进一步提高了逻辑综合时对版图的考虑。设计重用技术,验证技术,行为综合和逻辑综合,

设计预算技术,模块编译技术,布局布线自动化,版图提取和分析等技术的应用大大提高

了设计人员的设计能力,缩短了设计周期。

本文讲述的是基于标准单元库的数字集成电路的设计流程和方法学。它从行为级的 HDL

描述开始,依次进行系统行为级仿真, RTL 级仿真,逻辑综合,综合后仿真,自动化布局

布线,最后是版图后仿真。所有这些步骤都是通过工具自动完成,快速而有效。

我用 Synopsys 公司的 VSS(VHDL System Simulator)工具进行各种仿真,用 Design

Compiler 进行综合,用 Cadence 公司的 Silicon Ensemble 进行自动布局布线。对于最后的

版图后仿真,由于输出文件的限制,我们改用 Active-HDL 工具进行验证。并且解决 clock

tree 和版图后仿真的问题。本文用 DDFS , I2C , counter 等实例对整个流程加以了验证。

本文的第1章简要介绍了深亚微米数字集成电路的设计流程。从第 2 章开始我们将分

章节详细介绍各个主要步骤。第 2 章介绍系统行为级仿真方法。第 3 章介绍行为级综合和

模型编译。第 4 章解释了综合的概念,介绍了逻辑综合的实现及讨论了几个常见问题的解

决方法。第 5 章解决了版图后仿真的实现问题,阐述了各种技术库的生成,比较了系统行

为级仿真和综合后仿真的区别。第 6 章介绍了 Formal Verification 和其他辅助工具的应

用。第 7 章详细讲述了自动化布局布线方法,解决了 clock tree 的生成问题。由于版图后

仿真与综合后仿真在操作上没什幺区别,这里就略去不讲。

EDA设计的概述

1

1

第

第第

第1

11

1章

章章

章

E

EE

ED

DD

DA

AA

A 设

设设

设计

计计

计的

的的

的概

概概

概述

述述

述

随着电路设计进入 VLSI ,甚至 ULSI 时代,电路规模迅速上升到几十万门甚至几

百万门。根据摩尔定律,每十八个月增加一倍。而设计人员的设计能力只是一个线性增长

的曲线,远远跟不上电路规模指数上升的速度。为了弥补这个差距,工业界对 EDA 软件和

设计方法不断提出新的要求。在 80 年代,由美国国防部支持的 Very High Speed Integrated

Circiut 发展计划促成了 VHDL 的诞生,并使之成为了国际标准。而 Cadence 公司的 Verilog

HDL 在工业界获得了广泛的接受,并最终成为了国际标准。利用 HDL 进行设计大大方便了设

计输入,提高了设计抽象程度,更有利于设计人员发挥聪明才智,因而可以大大提高设计

效率,缩短了设计周期。

随着电路规模的增大和系统复杂度的增加,直接用电路实现已是不可能, RTL 级的 HDL

编码也变得越来越难以忍受。行为级综合技术的发展为设计者带来了曙光。它使设计者开

始逐步摆脱繁重的 RTL 级编码,大大提高了设计者的设计灵活性和设计效率,减少了工艺

及物理对设计的约束。

为了提高设计的速度和设计成功率,利用已验证正确的设计作为新设计的一部分是现

在大规模设计的常用方法。随着时代的发展,人们对产品的要求越来越高。他们要求的不

仅仅是新产品的出现,更多的是要求改善旧产品的性能,增加更多的功能。为此对旧的设

计的修改是必须的。为了充分利用以前的成果,减少修改的工作量,加快设计修改速度,

同时尽量不影响不变部分,提高修改的成功率,技术更改指令 ECO 被提了出来并得到了发

展。

随着半导体工艺的不断进步,器件的特征尺寸越来越小,线宽越来越窄,器件的速度

变得越来越快。但同时随着设计的越来越复杂,电路规模的越来越大,金属线的长度和层

数不断增加,线宽也随之变小。这都导致了金属连线的延时变大。于是器件的延时不再是

一个系统的主要延时,连线的延时变得越来越重要,甚至超过了器件的延时。因此以前设

计系统时只考虑器件延时的观念已经行不通,设计时考虑连线的延时是必须的。设计者在

设计时必须同时考虑到综合和版图,且使综合和版图尽量结合在一起。把综合后的时序信

息前注释到布局布线,同时布局布线后提取寄生参数和时序延时信息后注释回综合,从而

使逻辑设计和物理设计紧密的结合起来。考虑到连线延时,必须进行版图后仿真。版图后

仿真必须后注释大量的版图时序延时信息。

电路规模的增大导致了时钟同步的问题。时钟到达不同子模块的延时不同,这成了一

个系统失败的致命弱点。为了解决时钟延时的问题,在布局布线中 CLOCK TREE 的技术得到

了极大的发展。它较好的解决了这时钟延时的问题。

随着系统规模的不断增大,功耗的问题变得越来越重要,散热成了人们的一大难题。

为此,设计者在进行设计系统的时候必须考虑功耗的问题。在逻辑综合后必须进行功耗分

析。

设计流程

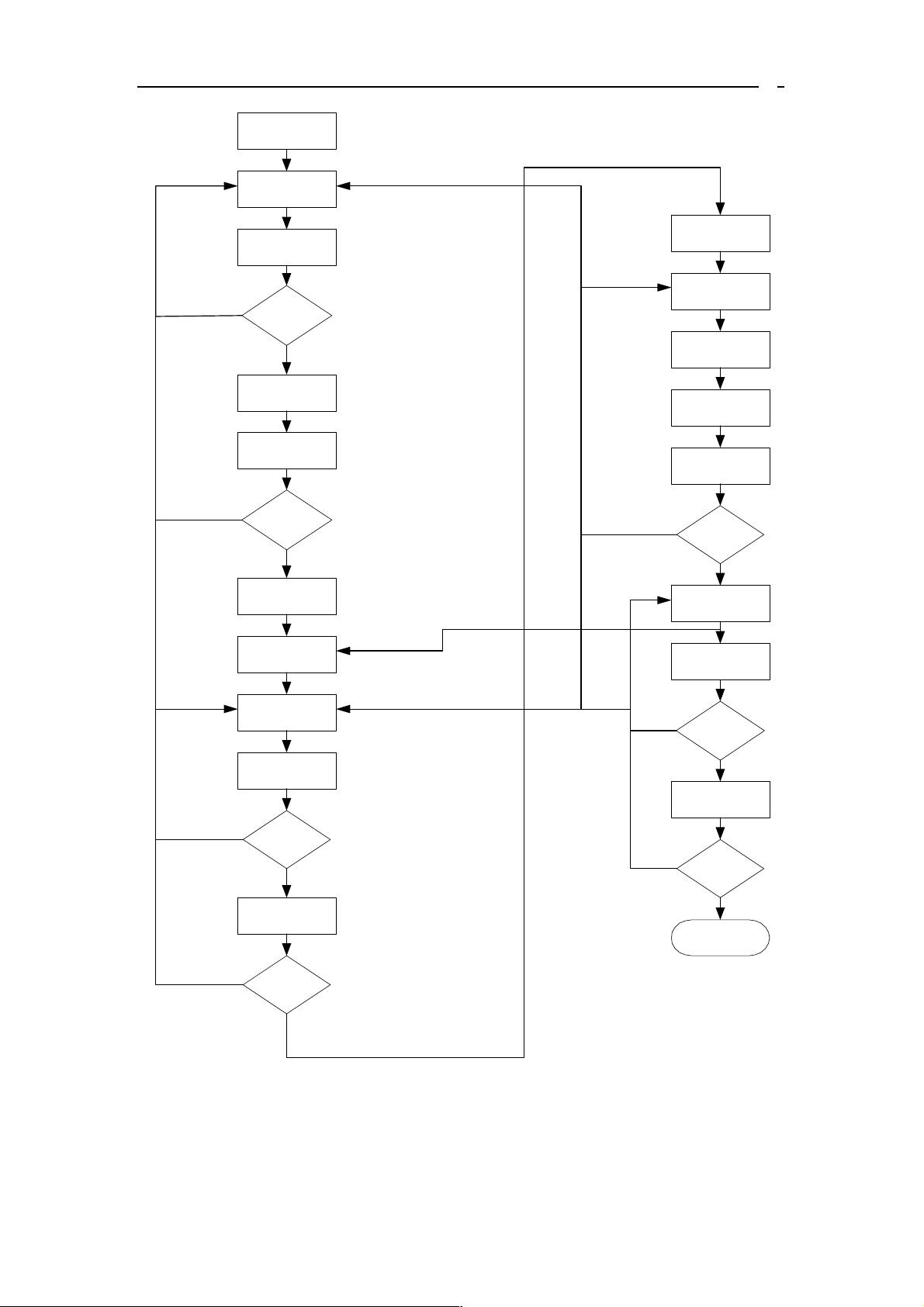

基于标准单元库的数字集成电路设计方法主要流程为及工具使用如下:

1. 功能与规格要求;

2. 行为级编码,仿真 test bench 的准备及 DFT 存储器的 BIST 插入;

3. 用 VSS 进行系统行为级的功能验证;

4. 用 Behavioral Compiler 进行行为级综合,生成 RTL 级网表;

5. 用 VSS 进行 RTl 级仿真;

6. 用 Design Compiler 进行初级综合;

7. 用 Design Budgeter 进行设计约束的分配;

8. 用 Design Compiler 进行逻辑综合与测试扫描插入;

9. 用 VSS 进行综合后时序功能验证;

10. 用 Design Compiler 或 Prime Time 版图前静态时序分析;

11. 用 Power Compiler 进行功耗分析;

12. 用 Silicon Ensemble 进行 floorplan,布局,Clock Tree 的插入以及全局布线;

13. 插入 Clock Tree 后的网表重新读回 Design Compiler ;

14. 用 Formality 验证原来的综合后网表和插入 Clock Tree 后的网表;

EDA设计的概述

2

2

15. 用 Prime Time 进行全局布线后静态时序分析;

16. 用 Silicon Ensemble 进行细节布线;

17. 用 Prime Timing 进行版图后静态时序分析;

18. 用 VCS 或其他门级电路的仿真器进行版图后时序功能验证;

19. 流片

大体的流程图如图 1.1 所示:

由于篇幅的限制,本文将只详细讲述几个重要的工具,其他工具只讲述其流程。

EDA设计的概述

3

3

功能与 规格要求

行为级编码

行为级的功能验证

行为级综合

功能正确?

RTL级功能验证

功能正确?

初级综合

约束分配

逻辑综合与测试扫

描的插入

综合后仿真

功能正确?

版图前 STA

时序满足?

功 耗分析

floorplan ,布

局 , CT插入和全

局布线

重新综合插 入 CT后

的网表

全局布线 后 STA

时序满足?

细节布线

版图后STA

时序满足?

版图后仿真

功能正确?

插入CT前后 的 逻辑

网表比较

流片

NO

YES

YES

NO

NO

YES

YES

NO

YES

NO

NO

YES

NO

YES

RCs,SDF

图 1.1 数字集成电路的设计流程

评论0