7 Series FPGAs

Clocking Resources

User Guide

UG472 (v1.6) October 2, 2012

7 Series FPGAs Clocking Resources User Guide www.xilinx.com UG472 (v1.6) October 2, 2012

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum

extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL

WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF

MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether

in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising

under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or

consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action

brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same.

Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. You may not

reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and

conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm

; IP cores may be subject to warranty and

support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any

application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications:

http://www.xilinx.com/warranty.htm#critapps

.

AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING

FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A

VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE

XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES

THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF

XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2011–2012 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Kintex, Zynq, Artix, Spartan, ISE, Vivado, Zynq, and other designated

brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCIe, and PCI Express are trademarks of

PCI-SIG and used under license. All other trademarks are the property of their respective owners.

UG472 (v1.6) October 2, 2012 www.xilinx.com 7 Series FPGAs Clocking Resources User Guide

Revision History

The following table shows the revision history for this document.

Date Version Revision

03/01/11 1.0 Initial Xilinx release.

03/28/11 1.1 Updated disclaimer and copyright on page 2. Updated Clocking Architecture Overview

and Figure 2-2. Revised the discussion in Clock-Capable Inputs including adding

Table 1-1 and Figure 2-1. Revised some of the Global Clock Buffers descriptions. Revised

the description under Figure 2-17. Updated the I/O Clock Buffer—BUFIO section.

Updated Figure 2-20. Updated the Regional Clock Buffer—BUFR section. Updated the

description in Table 2-8. Revised Figure 2-23. Added the BUFMRCE to the BUFMR

Primitive section including Figure 2-25. Added BUFHCE to the Horizontal Clock

Buffer—BUFH, BUFHCE section. Moved Clock Gating for Power Savings.

Updated the MMCMs and PLLs section. Revised the Frequency Synthesis Only Using

Integer Divide section including Figure 3-4. Revised the discussion around adjacent

regions in CLKOUT[0:6] – Output Clocks. Updated the examples after Equation 3-11.

Moved and revised VHDL and Verilog Templates and the Clocking Wizard.

Added Appendix A, Multi-Region Clocking.

05/31/11 1.2 Added section on 7 Series FPGAs Clocking Differences from Previous FPGA

Generations.

Updated Figure 2-2. Clarified discussion in Clock-Capable Inputs section including

removing Table 1-1: Migration of devices in the same package with different top/bottom

alignments. Redrew Figure 2-4, Figure 2-16, Figure 2-18, and Figure 2-22.

Updated description of CLKOUT[0:6] in Table 3-5. Updated CLKFBSTOPPED –

Feedback Clock Status, page 79. Clarified the MMCM/PLL relationship including

updating Figure 3-10. Added more information to the Phase Shift section, including

Equation 3-5.

Revised Figure A-6 and Figure A-7

. Added Appendix B, Clocking Resources and

Connectivity Variations per Clock Region.

10/27/11 1.3 Moved 7 Series FPGAs Clocking Differences from Previous FPGA Generations. Added

Clock Buffer Selection Considerations. Clarified description in Clock-Capable Inputs.

Added another note after Figure 2-22, page 51. Added the Stacked Silicon Interconnect

Clocking section.

Updated Figure 3-6, page 69. Clarified descriptions in Frequency Synthesis Using

Fractional Divide in the MMCM, page 69, Interpolated Fine Phase Shift in Fixed or

Dynamic Mode in the MMCM, page 71, Determine the Input Frequency, page 72,

CLKOUT[0:6] – Output Clocks, page 78, and Reference Clock Switching, page 87.

Revised description of STARTUP_WAIT, page 81. Updated RST description in Table 3-5,

page 74. Updated CLKOUT[0]_DIVIDE_F allowed values in Table 3-7, page 79. Updated

Clock Network Deskew, page 68 adding Figure 3-12, page 88.

Updated Table B-1 and added Table B-2.

02/16/12 1.4 Replaced “clocking backbone” with “clock backbone” and “clocking region” with “clock

region” throughout.

Added Chapter 1, Clocking Overview, containing 7 Series FPGAs Clocking Differences

from Previous FPGA Generations from Chapter 2 and Summary of Clock Connectivity

from Appendix B. Updated Table 1-1. Removed XC7A8, XC7A15, XC7A30T, and

XC7A50T from Table 1-2.

Added Clock-Capable Inputs. Updated Global Clocking Resources, including BUFMR

Primitive. Updated Horizontal Clock Buffer—BUFH, BUFHCE. Updated paragraph

before Figure 2-27.

7 Series FPGAs Clocking Resources User Guide www.xilinx.com UG472 (v1.6) October 2, 2012

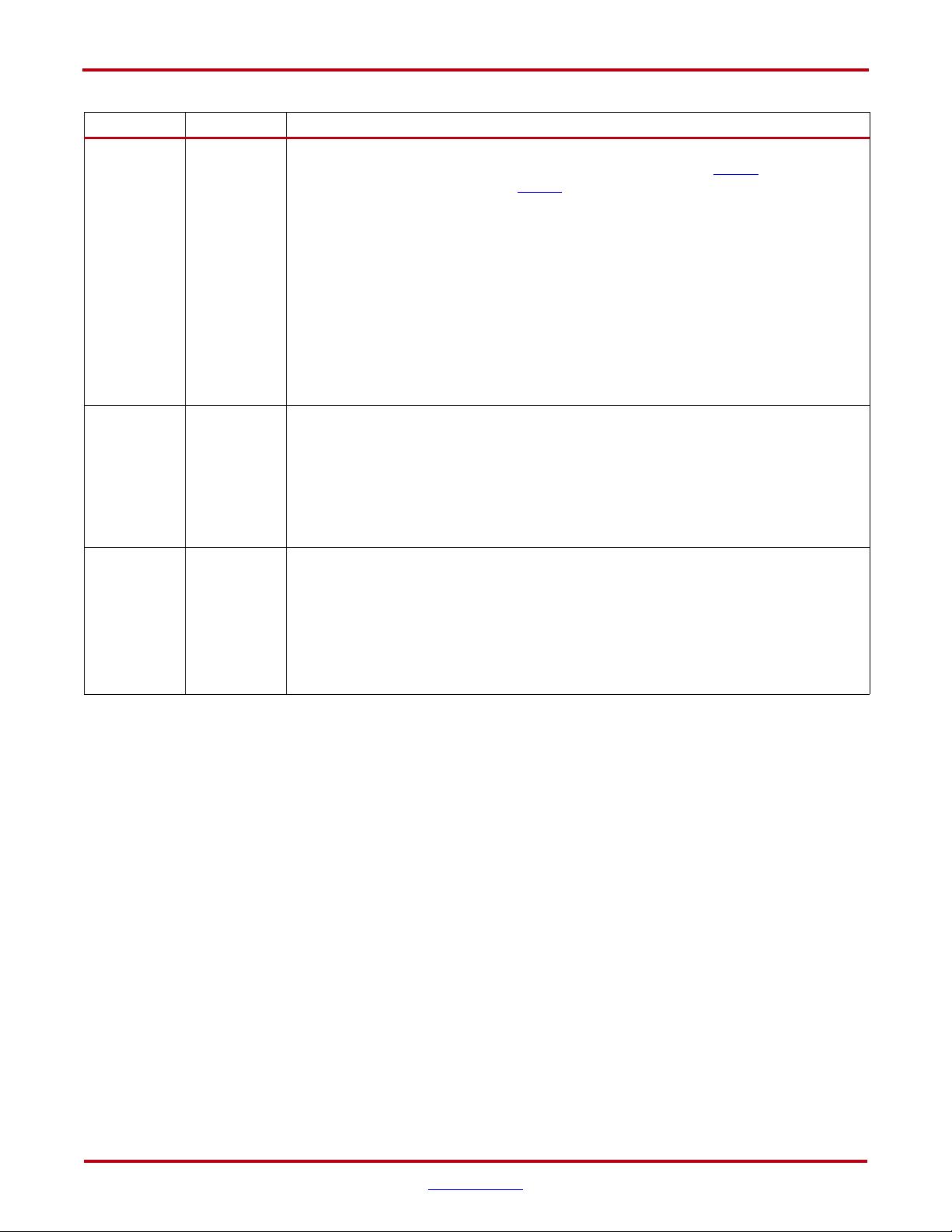

02/16/12 1.4

(Cont’d)

In introductory paragraph of High-Performance Clocks, removed description of HPCs

connecting to OSERDES and buffers. Replaced cross reference to UG429, 7 Series FPGAs

Migration Methodology Guide, with UG872

, Large FPGA Methodology Guide. Updated

Stacked Silicon Interconnect Clocking. Replaced SRL with SLR in Figure 2-28. Added

Figure 2-30.

Removed hold block from Figure 3-2. Updated clock frequencies in Frequency Synthesis

Only Using Integer Divide. Replaced 64 with 63 in Equation 3-4. Updated Interpolated

Fine Phase Shift in Fixed or Dynamic Mode in the MMCM. Updated pin description of

LOCKED in Table 3-5. Updated LOCKED. In Table 3-7, updated type and allowed

values of CLKOUT[0]_DIVIDE_F and CLKFBOUT_MULT_F, and description of

STARTUP_WAIT and COMPENSATION. In Table 3-8, added STARTUP_WAIT and

updated description of COMPENSATION. Replaced GTX with GT in Figure 3-10.

Updated Dynamic Reconfiguration Port.

Added Appendix B, Clocking Resources and Connectivity Variations per Clock Region.

07/13/12 1.5 Updated paragraph after Figure 1-4. Added bullet about spread spectrum support to

Key Differences from Virtex-6 FPGAs. Updated BUFG and BUFH pins, and removed

IBUFDS_GTE2.O/IBUFDS_GTE2.ODIV2 pin from Table 1-1. Updated Table 1-2.

Updated note 5 in Table 2-1. Added Figure 2-28.

Updated last sentence of Introduction. Updated DO[15:0] – Dynamic Reconfiguration

Output Bus. Added SS_EN, SS_MODE, and SS_MOD_PERIOD to Table 3-7. Added

Spread-Spectrum Clock Generation.

10/02/12 1.6 Added note to Table 1-1. Removed XC7A350T and XC7V1500T from Table 1-2.

Updated first paragraph of Single Clock Driving Multiple CMTs. Added notes 5 and 8 to

Table 2-1. Updated paragraph after Table 2-10.

Added Table 3-9 and timing constraint calculations for 25 MHz and 80 MHz input

clocks. In Table 3-10, changed Bandwidth value from N/A to Low, and removed

duplicate paragraph after table.

Removed XC7A350T from title of Figure B-4.

Date Version Revision

7 Series FPGAs Clocking Resources User Guide www.xilinx.com 5

UG472 (v1.6) October 2, 2012

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Preface: About This Guide

Guide Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Chapter 1: Clocking Overview

Clocking Architecture Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Clock Routing Resources Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

CMT Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Clock Buffers, Management, and Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

7 Series FPGAs Clocking Differences from Previous FPGA Generations . . . . . 19

Key Differences from Virtex-6 FPGAs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Key Differences from Spartan-6 FPGAs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Summary of Clock Connectivity. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Clocking Differences in 7 Series FPGAs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Chapter 2: Clock Routing Resources

Clock Buffer Selection Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Clock-Capable Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Single Clock Driving a Single CMT. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Single Clock Driving Multiple CMTs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Clock-Capable Input Pin Placement Rules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Global Clocking Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Clock Tree and Nets - GCLK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Clock Regions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Global Clock Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Global Clock Buffer Primitives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Additional Use Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Regional Clocking Resources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Clock-Capable I/O. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

I/O Clock Buffer—BUFIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

BUFIO Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

BUFIO Use Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Regional Clock Buffer—BUFR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

BUFR Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

BUFR Attributes and Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

BUFR Use Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Regional Clock Nets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Multi-Region Clock Buffer—BUFMR/BUFMRCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

BUFMR Primitive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Horizontal Clock Buffer—BUFH, BUFHCE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

High-Performance Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Clock Gating for Power Savings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table of Contents