多功能 ALU 的设计实验

姓 名: 罗登

学 院: 信息科学与技术

专 业:计算机科学与技术

班 级: 计科 1605

学 号: 2016011186

1

0.1 实验目标

在本次实验中,要求设计一个具有 8 种功能的 32 位 ALU,并能够产生运算结果的表示:

结果为零标志 ZF(Zero Flag)、进借位标志 CF(Carry Flag),溢出标志 OF(Overow Flag)、符

号位标志 (Sign Flag) 和奇偶位标志 PF(Parity Flag)。

ALU 通过 4 根控制线 ALU_OP[3:0] 来选择其 8 种功能,功能见表(多余 8 位用于扩展

后续的运算功能):

表 1: ALU 的功能说明

ALU_OP[3:0] ALU

功能 功能说明

0000 and 按位与运算

0001 or 按位或运算

0010 xor 按位异或运算

0011 nor 按位或非运算

0100 add 算术加法运算

0101 sub 算术减法运算

0110 slt 如果 A<B,则输出 1,否则输出 0

0111 sll B 逻辑左移给定 A 位数

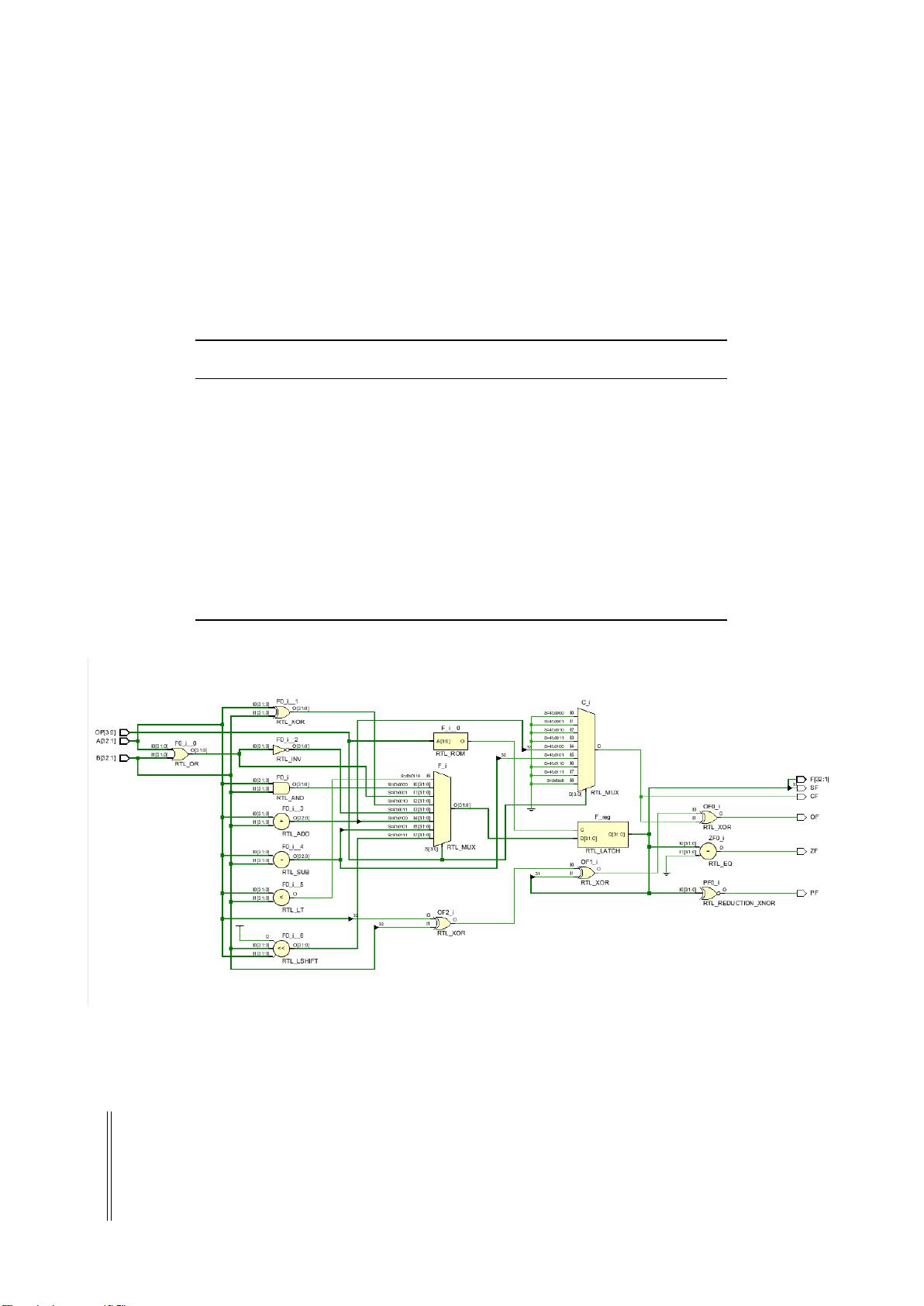

图 1: 原理图

创建 Verilog HDL 文件后,写入下列代码:

1 `timescale 1ns / 1ps

2

3 module ALU(OP , A, B, F, ZF, CF , OF , SF, PF);

4 parameter SIZE = 32;

5 input [3:0] OP; // the name of the operator

2