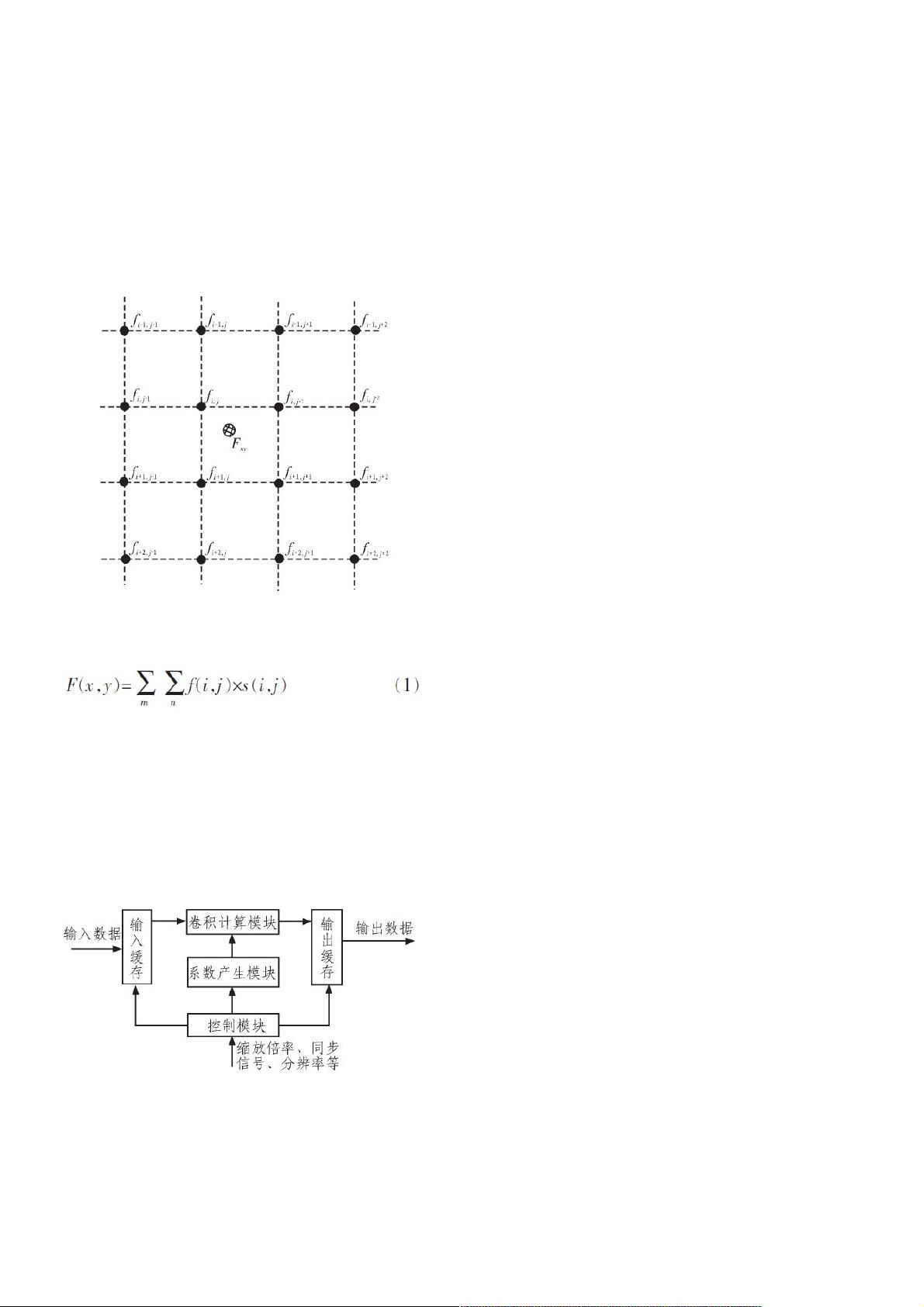

基于FPGA硬件实现固定倍率的图像缩放,将2维卷积运算分解成2次1维卷积运算,对输入原始图像像素先进行行方向的卷积,再进行列方向的卷积,从而得到输出图像像素。把图像缩放过程设计为一个单元体的循环过程,在单元体内部,事先计算出卷积系数。降低了FPGA设计的复杂性,提高了图像缩放算法的运算速度,增强了系统的实时性,已经应用于某款航空电子产品中,应用效果良好。 基于FPGA实现固定倍率的图像缩放是一种高效、实时的图像处理技术,它通过将复杂的2维卷积运算拆分为两次1维卷积运算来简化设计,首先在行方向上进行卷积,随后在列方向上进行,以此达到缩放目的。这种方法降低了FPGA设计的复杂性,同时提高了运算速度,确保了系统的实时性。 图像缩放是图像处理中的基本操作,用于调整图像的尺寸,使其适应不同的显示设备和应用需求。在航空电子领域,由于图像处理系统的高要求,硬件实现图像缩放成为首选,因为它可以提供更高的分辨率和更强的实时性。FPGA(Field-Programmable Gate Array)因其可编程性和内置的硬件资源(如PLL、乘法器和存储器)成为实现这种功能的理想平台。 固定倍率的图像缩放算法中,输出图像的每个像素F(x, y)是输入图像f(x, y)像素矩阵中对应位置的2维卷积结果。卷积系数s(i, j)决定了邻域像素的相关程度,而邻域范围则影响着算法的运算速度。为了优化FPGA实现,2维卷积被分解为两个1维过程,这样可以减少计算复杂性,提高处理速度。 在FPGA实现的图像缩放功能结构中,卷积计算模块是关键,它接收输入像素和系数,进行两次卷积运算。控制模块是核心逻辑,负责协调各个部分的工作,可以选择逆向映射或顺向映射方式来确定输入像素坐标。逆向映射需要较大的输入缓存,以保持输入和输出时钟同步,而顺向映射则利用输入像素的时序,减少了存储需求。 在实际设计中,为了简化控制模块和硬件结构,可以将图像缩放过程划分为多个单元体,每个单元体内预先计算好卷积系数。例如,若要将每行720个像素放大到768个像素,那么15个输入像素可以作为一个单元体,对应16个输出像素。这样,设计一个15状态的状态机就足以处理所有情况。通过这种方式,可以有效降低设计难度,同时保证处理效率。 以768x576的输入图像放大到1024x768为例,该过程会先对输入图像的每一行进行卷积,然后在列方向上进行同样的处理。通过这种方法,能够得到所需尺寸的输出图像,且由于采用了固定倍率,整个过程可以精确控制,确保了输出图像的质量。 基于FPGA实现固定倍率的图像缩放通过巧妙地分解2维卷积运算,优化了硬件资源的使用,提升了处理速度,满足了航空电子等对实时性要求高的领域的需求。这种方法不仅降低了设计复杂度,还为实现其他复杂图像处理任务提供了基础,是现代嵌入式系统中图像处理的重要技术之一。

- 粉丝: 5

- 资源: 894

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 角度OpenGL ES 到 DirectX 的转换.zip

- 视频播放效果,滤镜(DirectX .hlsl 像素着色器、mpv .hook).zip

- 自用stm32学习项目,禁止商用

- 02 计算机基础模拟卷1

- 虚拟 GIZMO - 3D 对象操纵器,定位器,通过鼠标,具有平移和推拉,缩放功能.zip

- dutyyyyyyyyyyyyyyyyyy

- 英雄联盟 DirectX11 内部基础.zip

- 英特尔小行星 DirectX 12 示例.zip

- 自动 wget 脚本用于下载并安装 PC 游戏所需的所有 .Net,VC++ 可再发行组件 + 一些其他工具(如 7zip、Powershell 等) 焦土红色政策 .zip

- 自动化连线工具使用教程

信息提交成功

信息提交成功