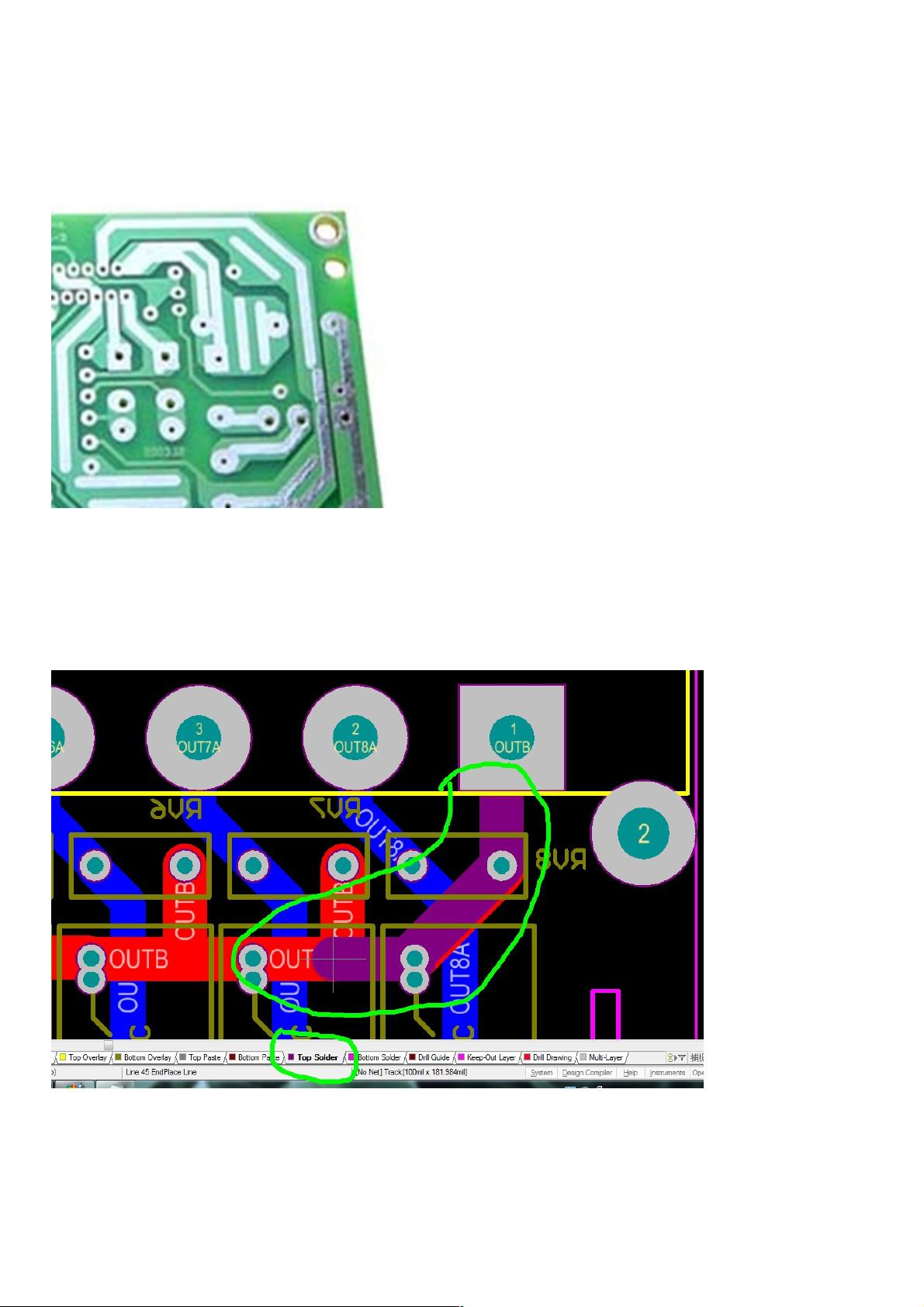

在电子硬件设计中,PCB(印制电路板)的设计是一项关键步骤,它涉及到电路的布局、信号传输以及元件的连接。在特定情况下,为了满足大电流通过的需求,设计师可能会选择进行PCB走线开窗上锡的操作。下面将详细解释这一过程。 我们来看标题中的“PCB走线开窗上锡”。走线开窗意味着在PCB的阻焊层(通常称为绿油层)上移除一部分,以便于在这些区域上锡。阻焊层的作用是防止焊接过程中不需要焊接的地方被锡膏覆盖,防止短路和提高生产效率。然而,当电路需要承载较大电流时,简单的走线宽度增加可能不足以满足需求,这时就需要在特定线路上去除阻焊层,使线路能被更多的锡覆盖,从而增强其载流能力。 在DXP(Altium Designer或其他类似PCB设计软件)中实现这一操作通常分为以下几步: 1. **绘制走线**: 在顶层(top layer)或底层(bottom layer)根据实际需求绘制走线。这些走线将承载大电流,因此需要确保它们的宽度足够。 2. **创建开窗**: 在助焊层(top solder或bottom solder)中,再次绘制与走线完全重合的非电气线。这是因为助焊层是负片工艺,即有线条的地方不会涂敷阻焊层,无线条的地方则会保留阻焊层。所以,我们要在需要去除阻焊层的位置画线。 3. **大面积开窗**: 如果需要在大面积的阻焊层上开窗,可以利用覆铜工具在top solder层或bottom solder层上拖拽出相应形状。这里要注意,虽然使用了覆铜工具,但目的并不是覆盖铜皮,而是定义阻焊层不覆盖的区域,没有网络概念,纯粹是为了开窗。 补充内容中提到了top solder层和top paster层: 1. **top solder层**: 它是助焊层,意味着该层上无阻焊的地方会喷锡,而有线路的地方则不会喷锡。设计师有时会利用这个特性来实现特定区域的上锡处理。 2. **top paster层**: 这是制作钢网(用于印刷锡膏)的参考层。设计错误往往发生在混淆top paster层与top solder层,如将top paste层当作solder层使用,或者将solder层同时作为线路层和助焊层,这会导致预期的开窗和线路分布出现问题。 PCB走线开窗上锡是一个细致且技术性强的过程,它需要设计师对PCB设计软件的深入理解以及对电子制造工艺的熟悉。正确操作不仅可以优化电路性能,还能提高生产效率和产品质量。在设计过程中,一定要避免常见的错误,确保每个层的功能得以正确体现,以达到预期的电路效果。

小小二-yan2023-07-28文件中的步骤经过实践验证,可信度高。

小小二-yan2023-07-28文件中的步骤经过实践验证,可信度高。 SLHJ-Translator2023-07-28文件内容清晰,对于了解PCB走线开窗上锡的原理和过程有很好的帮助。

SLHJ-Translator2023-07-28文件内容清晰,对于了解PCB走线开窗上锡的原理和过程有很好的帮助。 一曲歌长安2023-07-28对于初学者来说,这是一份很有指导性的文件,对提高走线技术有很大帮助。

一曲歌长安2023-07-28对于初学者来说,这是一份很有指导性的文件,对提高走线技术有很大帮助。 lowsapkj2023-07-28文档内容简洁明了,不会让人感到晦涩难懂。

lowsapkj2023-07-28文档内容简洁明了,不会让人感到晦涩难懂。 丽龙2023-07-28这份文件详细介绍了PCB走线开窗上锡的实现方法,让人一目了然。

丽龙2023-07-28这份文件详细介绍了PCB走线开窗上锡的实现方法,让人一目了然。

- 粉丝: 3

- 资源: 931

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 漂亮动态效果PPT柱形图-3.pptx

- 山形柱状图数据分析PPT模板-1.pptx

- 长阴影扁平化PPT柱形图模板-1.pptx

- 山形锥形柱状图PPT模板素材-1.pptx

- 条形图-数据图表-简约扁平-3.pptx

- 条形图-数据图表-时尚红蓝-PPT模板-3.pptx

- 小人人数比例分析说明PPT模板-1.pptx

- 柱状图-数据图表-高端商务-3.pptx

- 柱状图-数据图表-扁平简洁-3.pptx

- 柱状图-数据图表-简约扁平 -3.pptx

- 柱状图-数据图表-清新活泼-3.pptx

- 柱状图-数据图表-折纸简洁-3.pptx

- 柱状图-数据图表-简约扁平--1.pptx

- windows tcp连通性测试工具tcping64

- CDN(内容分发网络)核心技术解析及其在网络优化中的应用

- 饼图-数据图表-简约清新 -3.pptx

信息提交成功

信息提交成功