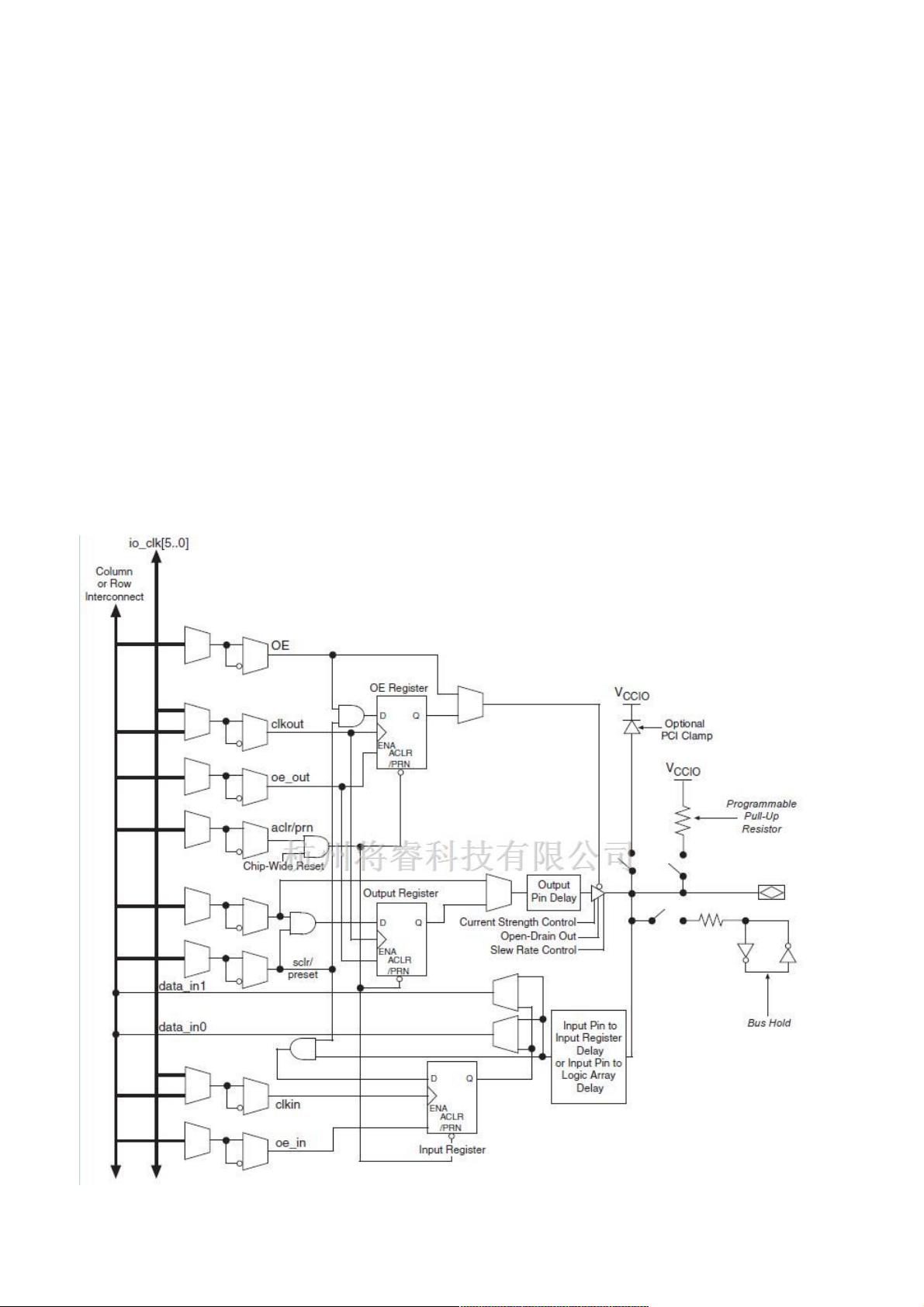

1. FPGA概述 FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点 2. FPGA芯片结构 FPGA芯片主要由三部分组成,分别是IOE(input output element,输入输出单元)、LAB(logic array block,逻辑阵列块,对于Xilinx称之为可配置逻辑块CLB)和Interconnect( FPGA(Field Programmable Gate Array)是现代电子设计中广泛使用的可编程逻辑器件,它允许设计者在不改变硬件的情况下,通过编程实现复杂的数字逻辑电路。这种灵活性使得FPGA成为原型验证、快速原型开发和定制化应用的理想选择。 1. FPGA概述 FPGA是由早期的可编程逻辑器件如PAL(Programmable Array Logic)、GAL(Generic Array Logic)和EPLD(Electrically Programmable Logic Device)演进而来。作为ASIC(Application-Specific Integrated Circuit)的补充,FPGA提供了一种介于完全定制电路和固定功能的集成电路之间的解决方案。FPGA的优势在于它具有较高的设计灵活性和较短的上市时间,同时避免了ASIC高昂的初期成本和较长的设计周期。 2. FPGA芯片结构 FPGA芯片主要包括以下三个主要组成部分: - IOE(Input Output Element):输入输出单元负责处理与外部电路的接口,提供多种电气标准的兼容性,包括LVTTL、LVCMOS、PCI、LVDS等。IOE可以配置为输入或输出,支持不同电压等级和驱动能力,以适应不同的系统需求。 - LAB(Logic Array Block):逻辑阵列块是FPGA的核心逻辑单元,通常由多个查找表(LUT)和寄存器构成。Xilinx公司将其称为CLB(Configurable Logic Block)。每个LAB包含一定数量的可编程逻辑元素(LE),LE通常由LUT和寄存器组成,LUT用于实现组合逻辑,寄存器则用于时序逻辑。 - Interconnect:内部连接网络负责将IOE、LAB以及其他内部组件相互连接。它包括各种类型的连接线,如Row interconnect、Column interconnect、Direct link interconnect、Local interconnect等,它们共同构建出复杂的互连网络,使得设计者可以自由地定义信号路径。 3. FPGA工作原理 FPGA的工作原理基于查找表和触发器的组合。每个LE中的LUT通过预编程的SRAM存储逻辑函数,当输入信号改变时,LUT会根据存储的逻辑函数输出相应的结果。D触发器则用于存储状态,形成时序逻辑。这些LE和触发器通过丰富的Interconnect网络进行互联,实现了组合逻辑和时序逻辑的混合设计。在设计过程中,设计者用硬件描述语言(HDL)如Verilog或VHDL编写逻辑设计,经过综合工具转换为逻辑网表,然后通过布局布线工具自动配置FPGA的内部资源,完成电路实现。 4. FPGA开发流程 开发FPGA通常涉及以下步骤: - 设计描述:使用HDL编写逻辑功能。 - 综合:将HDL代码转化为逻辑网表,优化逻辑资源。 - 布局布线:根据网表分配FPGA内部资源,确定信号路径。 - 验证:通过仿真和测试确保设计正确无误。 - 编程:将配置数据烧录到FPGA中,使其执行设计的功能。 - 调试与优化:根据测试结果调整设计,直至满足性能和功能要求。 FPGA因其灵活性和高效性在众多领域中得到广泛应用,包括通信、计算机、航空航天、工业控制以及消费电子产品等。理解FPGA的组成、工作原理以及开发流程,对于高效地利用这一技术至关重要。

- 粉丝: 6

- 资源: 924

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功