没有合适的资源?快使用搜索试试~ 我知道了~

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容。 11.1.1 层数的选择和叠加原则 确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是P

资源推荐

资源详情

资源评论

多层电路板的设计步骤多层电路板的设计步骤

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的

电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这

些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑

制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容。 11.1.1 层数的选择和叠加原则 确定

多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增

加。对于生产厂家来说,层叠结构对称与否是P

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结

构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信

号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节

将介绍多层PCB板层叠结构的相关内容。

11.1.1 层数的选择和叠加原则层数的选择和叠加原则

确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于

生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到的平衡。

对于有经验的设计人员来说,在完成元器件的预布局后,会对PCB的布线瓶颈处进行重点分析。结合其他EDA工具分析电路板的布

线密度;再综合有特殊布线要求的信号线如差分线、敏感信号线等的数量和种类来确定信号层的层数;然后根据电源的种类、隔离和抗干

扰的要求来确定内电层的数目。这样,整个电路板的板层数目就基本确定了。

确定了电路板的层数后,接下来的工作便是合理地排列各层电路的放置顺序。在这一步骤中,需要考虑的因素主要有以下两点。

(1)特殊信号层的分布。

(2)电源层和地层的分布。

如果电路板的层数越多,特殊信号层、地层和电源层的排列组合的种类也就越多,如何来确定哪种组合方式也越困难,但总的原则有

以下几条。

(1)信号层应该与一个内电层相邻(内部电源/地层),利用内电层的大铜膜来为信号层提供屏蔽。

(2)内部电源层和地层之间应该紧密耦合,也就是说,内部电源层和地层之间的介质厚度应该取较小的值,以提高电源层和地层之

间的电容,增大谐振频率。内部电源层和地层之间的介质厚度可以在Protel的Layer Stack Manager(层堆栈管理器)中进行设置。选择

【Design】/【Layer Stack Manager…】命令,系统弹出层堆栈管理器对话框,用鼠标双击Prepreg文本,弹出如图11-1所示对话框,可

在该对话框的Thickness选项中改变绝缘层的厚度。

如果电源和地线之间的电位差不大的话,可以采用较小的绝缘层厚度,例如5mil(0.127mm)。

(3)电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间。这样两个内电层的铜膜可以为高速信号传输提供电磁

屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

(4)避免两个信号层直接相邻。相邻的信号层之间容易引入串扰,从而导致电路功能失效。在两信号层之间加入地平面可以有效地

避免串扰。

(5)多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。

(6)兼顾层结构的对称性。

11.1.2 常用的层叠结构常用的层叠结构

下面通过4层板的例子来说明如何优选各种层叠结构的排列组合方式。

对于常用的4层板来说,有以下几种层叠方式(从顶层到底层)。

(1)Siganl_1(Top),GND(Inner_1),POWER(Inner_2),Siganl_2(Bottom)。

(2)Siganl_1(Top),POWER(Inner_1),GND(Inner_2),Siganl_2(Bottom)。

(3)POWER(Top),Siganl_1(Inner_1),GND(Inner_2),Siganl_2(Bottom)。

显然,方案3电源层和地层缺乏有效的耦合,不应该被采用。

那么方案1和方案2应该如何进行选择呢?一般情况下,设计人员都会选择方案1作为4层板的结构。选择的原因并非方案2不可被采

用,而是一般的PCB板都只在顶层放置元器件,所以采用方案1较为妥当。但是当在顶层和底层都需要放置元器件,而且内部电源层和地

层之间的介质厚度较大,耦合不佳时,就需要考虑哪一层布置的信号线较少。对于方案1而言,底层的信号线较少,可以采用大面积的铜

膜来与POWER层耦合;反之,如果元器件主要布置在底层,则应该选用方案2来制板。

如果采用如图11-1所示的层叠结构,那么电源层和地线层本身就已经耦合,考虑对称性的要求,一般采用方案1。

在完成4层板的层叠结构分析后,下面通过一个6层板组合方式的例子来说明6层板层叠结构的排列组合方式和优选方法。

(1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。

方案1采用了4层信号层和2层内部电源/接地层,具有较多的信号层,有利于元器件之间的布线工作,但是该方案的缺陷也较为明显,

表现为以下两方面。

① 电源层和地线层分隔较远,没有充分耦合。

② 信号层Siganl_2(Inner_2)和Siganl_3(Inner_3)直接相邻,信号隔离性不好,容易发生串扰。

(2)Siganl_1(Top),Siganl_2(Inner_1),POWER(Inner_2),GND(Inner_3),Siganl_3(Inner_4),Siganl_4(Bottom)。

方案2相对于方案1,电源层和地线层有了充分的耦合,比方案1有一定的优势,但是Siganl_1(Top)和Siganl_2(Inner_1)以及

Siganl_3(Inner_4)和Siganl_4(Bottom)信号层直接相邻,信号隔离不好,容易发生串扰的问题并没有得到解决。

(3)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),POWER(Inner_3),GND(Inner_4),Siganl_3(Bottom)。

相对于方案1和方案2,方案3减少了一个信号层,多了一个内电层,虽然可供布线的层面减少了,但是该方案解决了方案1和方案2共

有的缺陷。

① 电源层和地线层紧密耦合。

② 每个信号层都与内电层直接相邻,与其他信号层均有有效的隔离,不易发生串扰。

③ Siganl_2(Inner_2)和两个内电层GND(Inner_1)和POWER(Inner_3)相邻,可以用来传输高速信号。两个内电层可以有效

地屏蔽外界对Siganl_2(Inner_2)层的干扰和Siganl_2(Inner_2)对外界的干扰。

综合各个方面,方案3显然是化的一种,同时,方案3也是6层板常用的层叠结构。

通过对以上两个例子的分析,相信读者已经对层叠结构有了一定的认识,但是在有些时候,某一个方案并不能满足所有的要求,这就

需要考虑各项设计原则的优先级问题。遗憾的是由于

电路板的板层设计和实际电路的特点密切相关,不同电路的抗干扰性能和设计侧重点各有所不同,所以事实上这些原则并没有确定的

优先级可供参考。但可以确定的是,设计原则2(内部电源层和地层之间应该紧密耦合)在设计时需要首先得到满足,另外如果电路中需

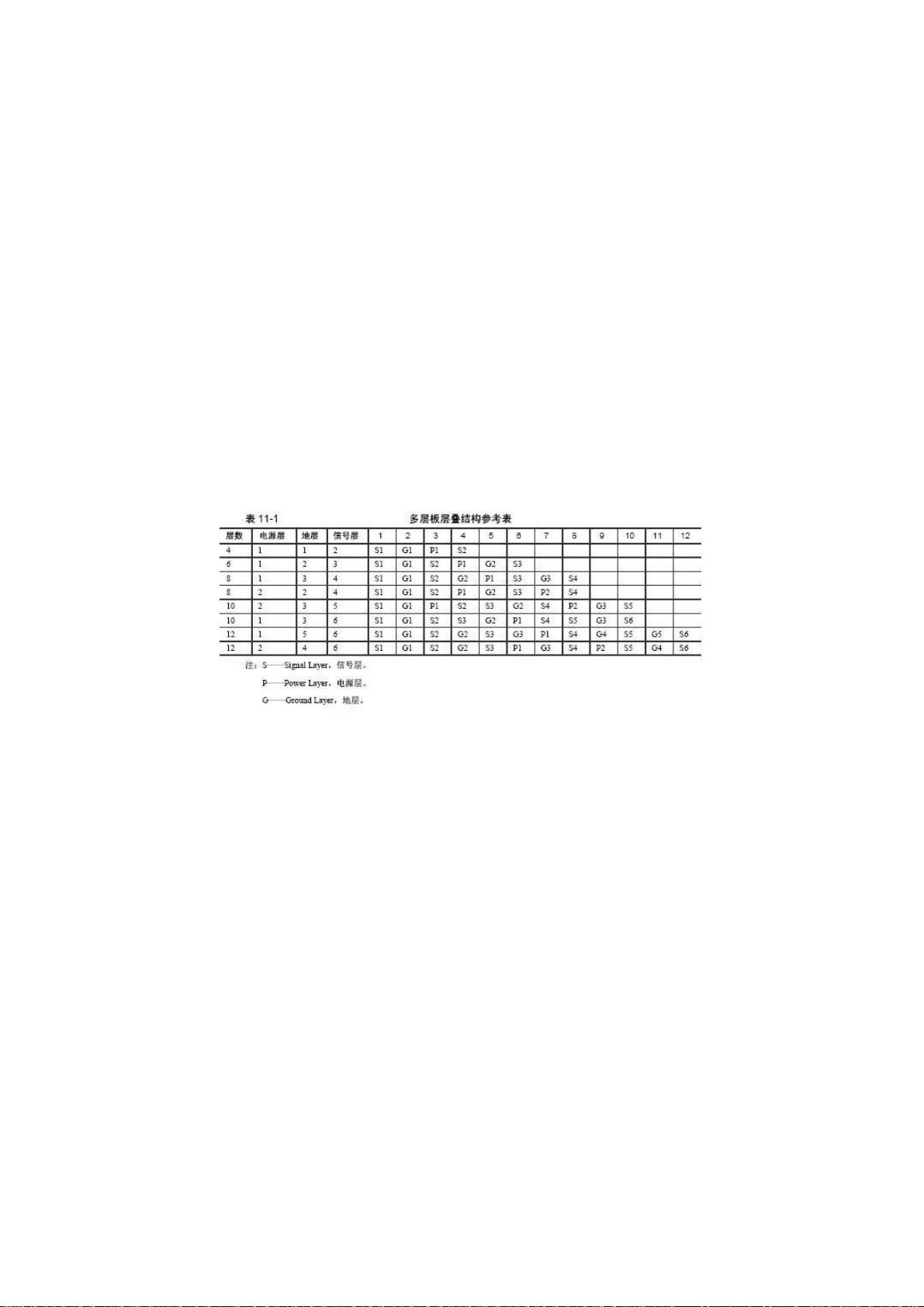

要传输高速信号,那么设计原则3(电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间)就必须得到满足。表11-1给

出了多层板层叠结构的参考方案,供读者参考。

11.2.1 元器件布局的一般原则元器件布局的一般原则

设计人员在电路板布局过程中需要遵循的一般原则如下。

(1)元器件单面放置。如果需要双面放置元器件,在底层(Bottom Layer)放置插针式元器件,就有可能造成电路板不易安放,也

不利于焊接,所以在底层(Bottom Layer)只放置贴片元器件,类似常见的计算机显卡PCB板上的元器件布置方法。单面放置时只需在电

路板的一个面上做丝印层,便于降低成本。

(2)合理安排接口元器件的位置和方向。一般来说,作为电路板和外界(电源、信号线)连接的连接器元器件,通常布置在电路板

的边缘,如串口和并口。如果放置在电路板的中央,显然不利于接线,也有可能因为其他元器件的阻碍而无法连接。另外在放置接口时要

注意接口的方向,使得连接线可以顺利地引出,远离电路板。接口放置完毕后,应当利用接口元器件的String(字符串)清晰地标明接口

的种类;对于电源类接口,应当标明电压等级,防止因接线错误导致电路板烧毁。

(3)高压元器件和低压元器件之间要有较宽的电气隔离带。也就是说不要将电压等级相差很大的元器件摆放在一起,这样既有利于

电气绝缘,对信号的隔离和抗干扰也有很大好处。

(4)电气连接关系密切的元器件放置在一起。这就是模块化的布局思想。

(5)对于易产生噪声的元器件,例如时钟发生器和晶振等高频器件,在放置的时候应当尽量把它们放置在靠近CPU的时钟输入端。

大电流电路和开关电路也容易产生噪声,在布局的时候这些元器件或模块也应该远离逻辑控制电路和存储电路等高速信号电路,如果可能

的话,尽量采用控制板结合功率板的方式,利用接口来连接,以提高电路板整体的抗干扰能力和工作可靠性。

(6)在电源和芯片周围尽量放置去耦电容和滤波电容。去耦电容和滤波电容的布置是改善电路板电源质量,提高抗干扰能力的一项

重要措施。在实际应用中,印制电路板的走线、引脚连线和接线都有可能带来较大的寄生电感,导致电源波形和信号波形中出现高频纹波

和毛刺,而在电源和地之间放置一个0.1mF的去耦电容可以有效地滤除这些高频纹波和毛刺。如果电路板上使用的是贴片电容,应该将贴

片电容紧靠元器件的电源引脚。对于电源转换芯片,或者电源输入端,是布置一个10mF或者更大的电容,以进一步改善电源质量。

(7)元器件的编号应该紧靠元器件的边框布置,大小统一,方向整齐,不与元器件、过孔和焊盘重叠。元器件或接插件的第1引脚

表示方向;正负极的标志应该在PCB上明显标出,不允许被覆盖;电源变换元器件(如DC/DC变换器,线性变换电源和开关电源)旁应

该有足够的散热空间和安装空间,外围留有足够的焊接空间等。

11.2.2 元器件布线的一般原则元器件布线的一般原则

设计人员在电路板布线过程中需要遵循的一般原则如下。

(1)元器件印制走线的间距的设置原则。不同网络之间的间距约束是由电气绝缘、制作工艺和元件大小等因素决定的。例如一个芯

片元件的引脚间距是8mil,则该芯片的【Clearance Constraint】就不能设置为10mil,设计人员需要给该芯片单独设置一个6mil的设计规

则。同时,间距的设置还要考虑到生产厂家的生产能力。

另外,影响元器件的一个重要因素是电气绝缘,如果两个元器件或网络的电位差较大,就需要考虑电气绝缘问题。一般环境中的间隙

安全电压为200V/mm,也就是5.08V/mil。所以当同一块电路板上既有高压电路又有低压电路时,就需要特别注意足够的安全间距。

(2)线路拐角走线形式的选择。为了让电路板便于制造和美观,在设计时需要设置线路的拐角模式,可以选择45°、90°和圆弧。一

般不采用尖锐的拐角,采用圆弧过渡或45°过渡,避免采用90°或者更加尖锐的拐角过渡。

剩余11页未读,继续阅读

资源评论

weixin_38687343

- 粉丝: 6

- 资源: 903

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 光影魔术手v4.6.4.920图像画质优化效果处理.mp4

- 谷歌地球pc版Google Earth Pro 7.3.6.10155.mp4

- 谷歌商店客户端 Google Play Store v43.9.18.mp4

- 果茶视频app 高清热门电影电视剧.mp4

- 还有玩LOL的吗,免费新皮肤又来了.mp4

- 海底捞火锅75亓买100亓代金券.mp4

- 基于android studio开发的安卓的新闻app项目源码+报告(高分期末大作业)

- WordPress子比AI自动发文章插件AI辅助写作随更版wapai-ai-create.zip

- springboot004网页时装购物系统(源码+数据库+论文+PPT+包调试+一对一指导)

- 吸波材料建模单元周期仿真模拟,参数优化,计算反射损耗,极化角,入射角,等效阻抗等

- 基于Android studio开发的安卓的点餐系统源码(高分安卓期末大作业)

- WinCC V7.5结构变量创建面板实例的技术实现与应用场景

- springboot005学生心理咨询评估系统(源码+数据库+论文+PPT+包调试+一对一指导)

- Comsol声子晶体板能带模式区分

- 基于Android Studio开发的安卓的蜜雪冰城APP源码(高分项目)

- 基于MATLAB2020b的深度学习框架,提出了一种基于CNN-LSTM的多变量电力负荷预测方法,该方法将历史负荷与气象数据作为输入,输出一天96个时刻负荷值,建模学习特征内部动态变化规律,即多变量输

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功