Lab05_A 实验报告

毫秒计时器的设计与实现

1 实验目的

a. 掌握 Verilog 的结构化编程,学会模块的编写和调用。

b. 综合运用 Nexys3 开发板。

c. 混合利用时序电路与逻辑电路。

2 实验内容

实验介绍

通过使用 ISE 软件进行毫秒计时器的设计与实现,包括使用 ISE 软件设计并仿真和程序

下载。

计时器可以从 0.000s 计时到 9.999s,然后从头开始,Nexys3 开发板上面的 7 段数码管要

实时显示当前时间值(包括小数点),另外还有 4 个控制按钮,分别为复位、开始、停止、加

时(时间值加 0.001s)。

实验原理

a. ISE 软件是一个支持数字系统设计的开发平台。

b. 用 ISE 软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择 的器件型号是与实际下载板上的器件型号相同。

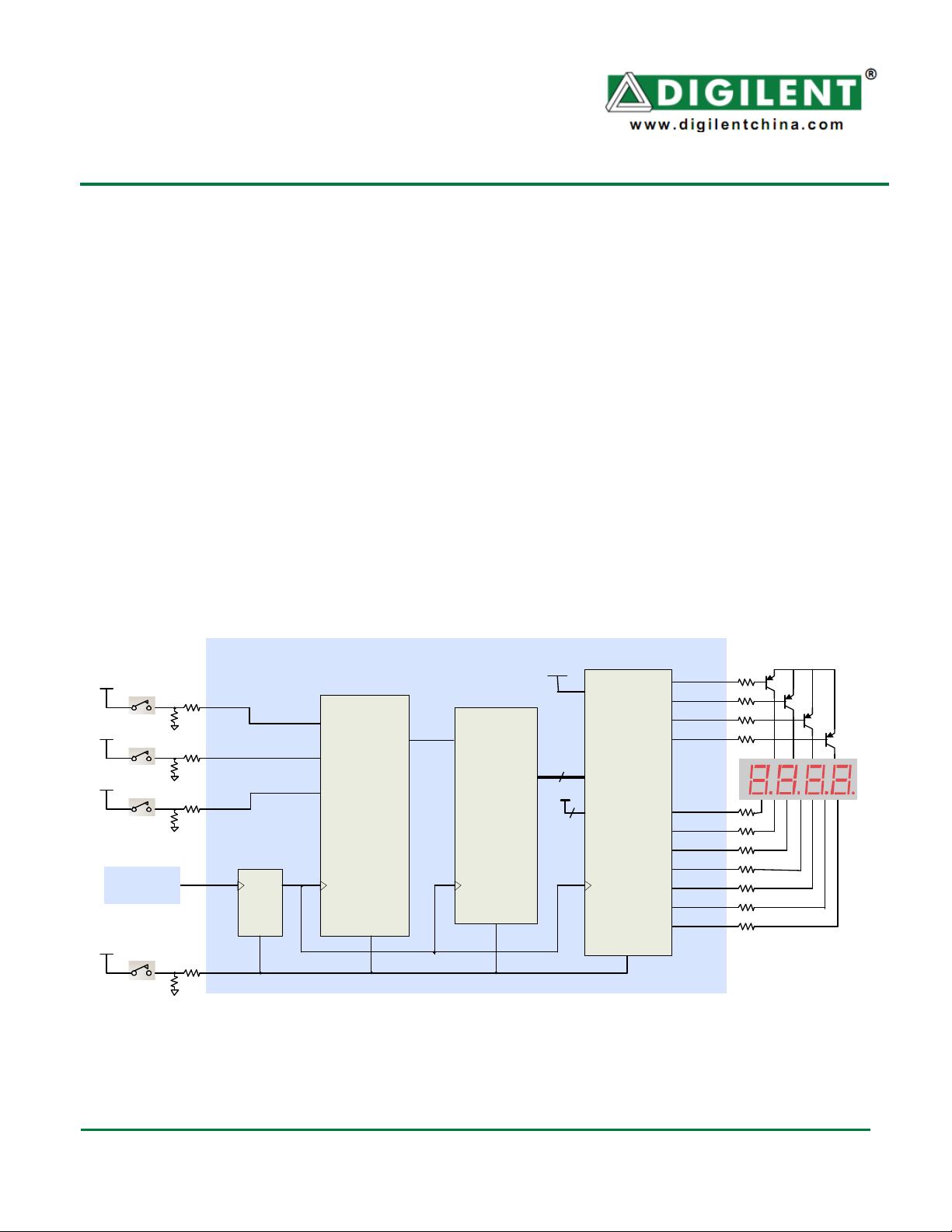

c. 计时器包含 4 个不同模块,图 1-1-1 所示为计时器顶级逻辑图。

图 1-1-1 计时器顶级逻辑图